tS) УСТРОЙСТВО для ПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для числового программного управления станком | 1978 |

|

SU744465A1 |

| Устройство для программного управления | 1978 |

|

SU734617A1 |

| Устройство для числового программного управления станком | 1980 |

|

SU924674A1 |

| Многоканальное устройство для программного управления | 1978 |

|

SU748431A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1356176A2 |

| Устройство для управления шаговым двигателем | 1983 |

|

SU1108600A1 |

| Система адаптивного числового программного управления металлорежущим станком | 1980 |

|

SU954945A1 |

| Система числового программногоупРАВлЕНия "TPACCA-Кп | 1979 |

|

SU813371A1 |

| Устройство для кинематического дробления стружки на токарных станках с числовым программным управлением | 1980 |

|

SU959036A1 |

1

Изобретение относится к автоматике и вычисли1ельной технике, в частности к автоматизации производственных процессов для позиционного программного управления рабочими органами станков.

Известно устройство для программного управления, содержащее последовательно соединенные блок ввода, блок буферной памяти, интерполятор и привод, причем интерполятор соединен с генератором импульсов СПНаиболее близким по технической сущности к изобретению является, устройство для программного управления, содержащее генератор импульсов, датчики изменения нагрузки, выт ходами соединенные с коммутаторами, а также последовательно соединенные блок ввода программы, блок декодирования и интерполятор, а.также первый и второй блоки управления шаговыми двигателями 2,

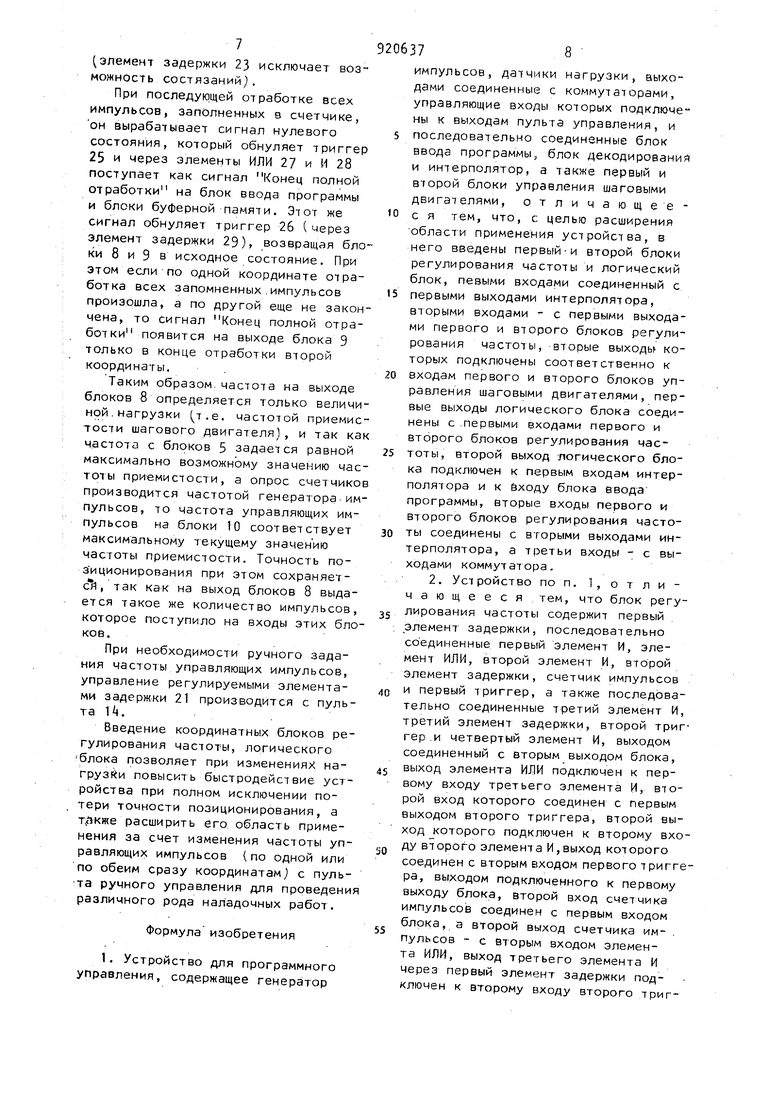

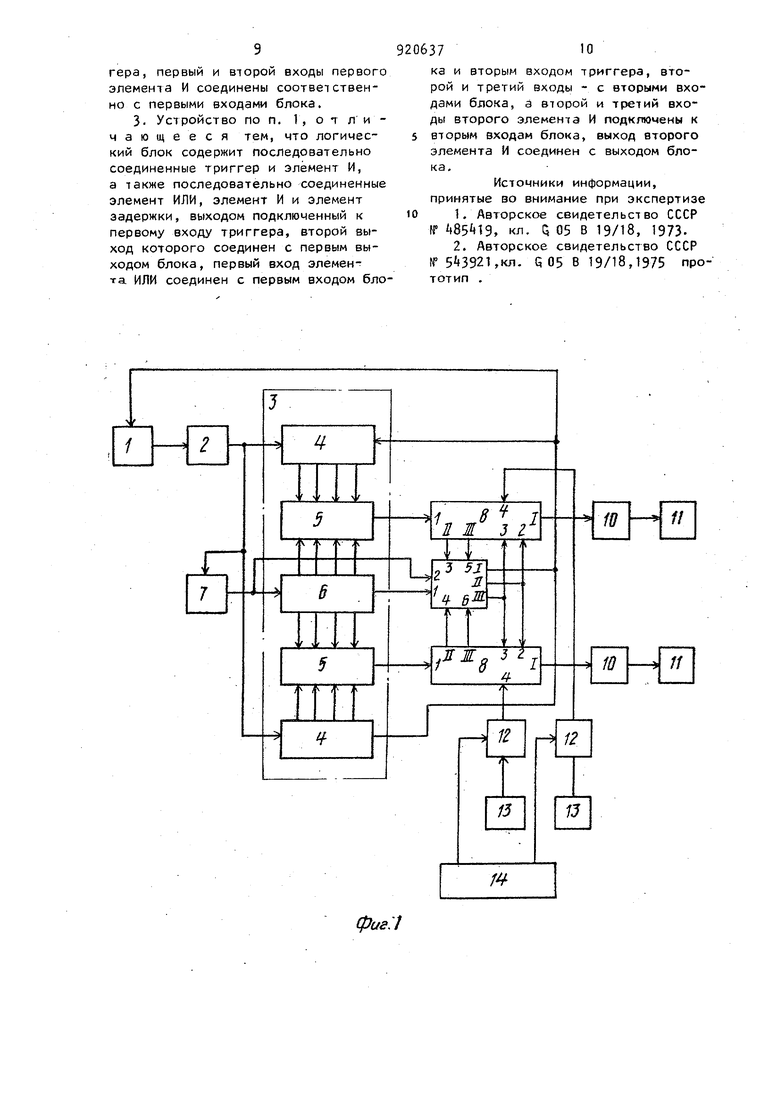

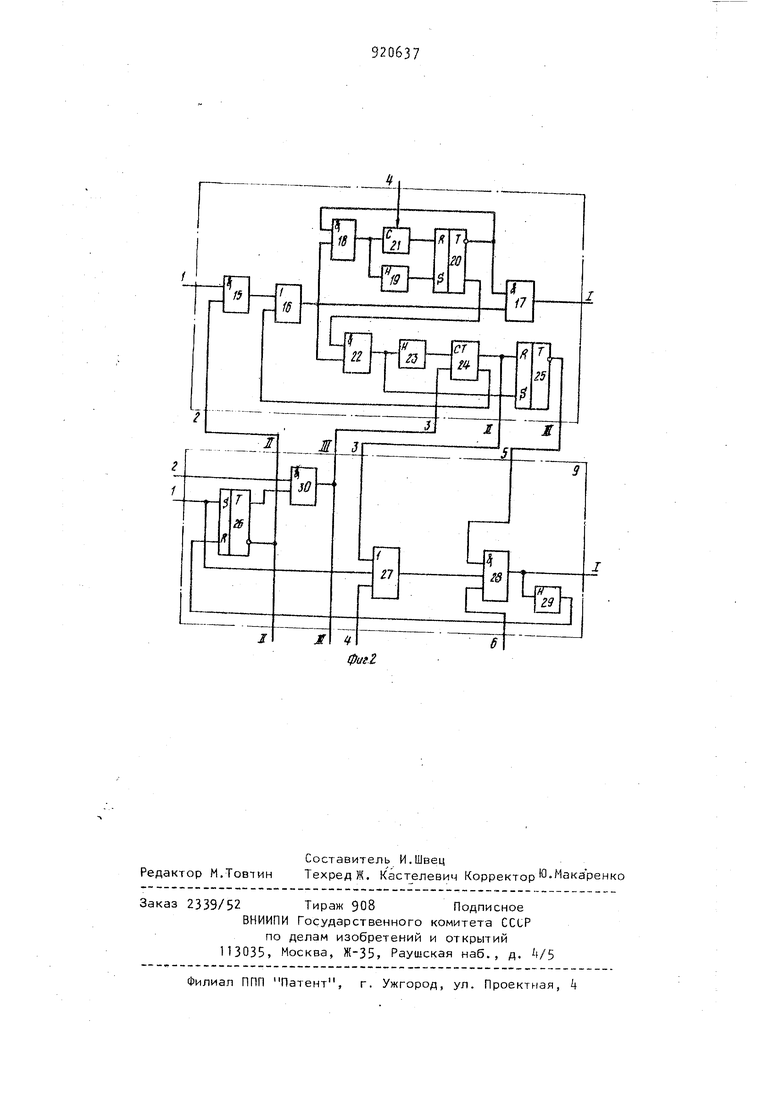

Известные устройства позволяют обрабатывать запрограммированные отрезки с заранее заданными скоростями движения исполнительного механизма. При этом величина скорости движения определяется частотой управляющих импульсов, поступающих на шаговые двигатели. Однако в режиме работы шагового двигателя под нагрузкой значение его частоты приемистости определяется характеристиками нагрузки: моментом нагрузки, моментом инерции нагрузки и т.п. Отсюда следует, что любые изменения в пррцессе работы например, подключение или отключение вспомогательных механизмов приводят к существенному изменению и значению частоты приемистости шагового двигателя. В известных устройствах данное изменение частоты приемистости учитывается только лишь программным заданием частоты управляющих импульсов отдельно для 3 каждого отрезка. Кроме того, эти устройства не позволяют независимо от программы осуществить в процессе работы изменение величины скорости движения исполнительного механизма (по обеим или одной из двух координат), необходимые для проведения различного рода наладочных операций. Таким образом, известные устройства обладают недостаточными функциональными возможностями. Цель изобретения - расширение области применения, Цель достигается тем, что в устройство для программного управления содержащее генератор импульсов, датчики нагрузки, выходами соединен ные с коммутаторами, вторые входы которых подключены к выходам пульта управления и последовательно соединенные блок ввода программы, блок декодирования и интерполятор, а также первый и второй блоки управления шаговыми двигателями, введены первый и второй блоки регулирования частоты и логический блок, первыми входами соединенный с первы ми выходами интерполятора, вторыми входами - с первыми выходами первого и второго блоков регулирования частоты, вторые выходы которых подключены соответственно ко входам первого и второго блоков управления шаговыми двигателями, первые выходы логического блока соединены с первы ми входами первого и второго блоков регулирования частоты, второй выход логического блока подключен к первым входам интерполятора и ко вх ду блока ввода программы, вторые входы первого и второго блоков регу лирования частоты соединены со вторыми выходами интерполятора, а третьи входы - с выходами коммутато ра. Блок регулирования частоты соде жит первый элемент задержки, последовательно соединенные первый элемент И, элемент ИЛИ, второй элемент второй элемент задержки, счетчик им пульсов и первый триггер, а также последовательно соединенные третий элемент И, третий элемент задержки второй триггер и четвертый элемент выходом соединенные со вторым выхо дом блока, выход элемента ИЛИ подключен к первому входу трет ьего элемента И, второй вход которого со инен с первым выходом второго три1- гера, второй выход которого подключен ко второму входу второго элемента И, выход которого соединен со вторым входом первого триггера, выходом подключенного к первому выходу блока, второй вход счетчика импульсов соединен с первым входом блока, а второй выход счетчика импульсов - со вторым входом элемента ИЛИ, выход третьего элемента И через первый элемент задержки подключен ко второму входу второго триггера, первый и второй входы пераого элемента И соединены соответственно с первыми входами блока. Кроме того, логический блок содержит последовательно соединенные триггер и элемент И, а также последовательно соединенные элемент ИЛИ, элемент И и элемент задержки, выходом подключенный к первому входу триггера, второй выход которого соединен с первым выходом блока, первый вход элемента ИЛИ соединен с первым входом блока и вторым входом три1- гера, второй и третий входы - со вторыми входами блока, а второй и третий входы второго элемента И подключены ко вторым входам блока, выход второго элемента И соединен с вы-ходом блока. На фиг.1 представлена блок-схема устройства; на фиг.2 - схемы координатного блока регулирования частоты и блока связи.. Устройство содержит блока ввода программы 1, блок декодирования 2, интерполятор 3 включающий координатные блоки буферной памяти 4, блоки 5 оперативной памяти и блок 6 делителей частоты,генератор 7 импульсов,блоки 8 регулирования частоты, логический 9 блок, блоки 10 управления шаговыми двигателями, шаговые двигатели 11, коммутаторы 12, датчики изменения 13 нагрузки и пульт 1. Блок регулирования частоты содержит (фиг.2) элемент И 15, элемент ИЛИ 1б, второй 17 и третий 18 элементы И, первый элемент задержки 19, первый триггер 20, регулируемый элемент задержки 21, четвертый элемент И 22, второй элемент задержки 23, счетчик импульсов 2 и второй триггер 25. Логический блок содержит триггер 26, элемент ИЛИ 27, первый элемент И 28, элемент задержки 29 и второй элемент И 30Устройство работает следующим о разом. Информация из блока ввода программы 1 поступает в блок декодирования 2 и затем записывается в бло км Ц буферной памяти интерполятора 3. После обработки исполнительным механизмом предыдущего перемещ ния с выхода 1 блока 9 выдается си нал Конец полной отработки, по которому информация с блока Ц посту пает в блоки 5 и вновь подключается блок ввода программы 1. Генератор импульсов 7 выдает импульсы на блок 6, который опрашивает блоки 5 Выходные сигналы данных блоков через блоки 8 поступают на блоки 10 управления шаговыми двигателями и .двигатели 11, отрабатывают заданное перемещение, по окончании отработки которого блок 9 вновь выдаёт сиг нал Конец полной отработки. В процессе выполнения заданного перемещения блоки 8 производят автоматическую регулировку частоты управляющих импульсов, поступающих на блоки 10 управления шаговыми двигат телями. Для этого импульсы, поступающие на блоки 8 с блоков 5, через элемент И 15, открытый сигналом с инверсного выхода триггера 2б логического блока, подаются на элемент ИЛИ 16. Частота х мпульсов задается равной максимальному возможному значению частоты приеми.стости шагового двигателя (или даже может быть больше этой частоты). Первый импульс с элемента ИЛИ 16 через эле мент И 17, открытый сигналом с инверсного выхода триггера 20, проходит для отработки на блок 10. Это же импульс через элемент И 18 и элемент задержки 19 (причем задержки импульса переключает триггер 20 запрещая тем самым прохождение следующих импульсов через элементы И 17 и 18, а через регулируемый элемент задержки 21, управляемый через коммутаторы 12 датчиками изменения нагрузки 13, обнуляем затем этот триггер, возвращая схему в исходное состояние. Если время включенно го состояния (от начального момента обнуления) триггера 20 меньше периода следования импульсов с блоков 5 то следующий импульс через элемент 17 вновь проходит на отработку и снова переключает триггер 20 376 Таким образом, на выход блоков 8 (выход 1} проходит частота, поступающая на входы этих блоков. В конце отработки заданного отрезка блок делителей частоты 6 вырабатывает сигнал, который через элементы ИЛИ 27 и 28, открытый инверсный выходом триггера 25, поступает на блок ввода программы 1 и блоки буферной памяти, производя смену информации . Включение и обнуление триггера 2б в этом случае несущественно. Если же в процессе отработки происходит изменение (увеличение нагрузки), то датчики 13 через коммутаторы 12 увеличивают время задержки сигнала элементами 21, т.е. и время включенного состояния триггеров 20. Когда это время становится больше периода следования импульсов с блоков 5 все импульсы, поступающие с элемента ИЛИ 16 в момент включенного состояния триггера 20, не проходят через закрытые элементы И 17 и 18, а через открытый прямым выходом триггера 20 элемент И 22 и элемент задержки 23 подаются в счетчик импульсов 2. При этом первый же из таких импульсов переключает триггер 25, запрещая прохождение сигнала с блока делителей частоты через элемент И 28. Таким образом на выход блоков 8 . поступают только те импульсы, которые подаются с элемента ИЛИ 16 в моменты выключенного состояния триггеров 20, а все остальные импульсы запоминаются в счетчиках импульсов 2. Когда на входы блоков 8 поступят все импульсы, число которых соответствует заданному перемещению, блок делителей частоты 6 выдает сигнал, прохождение которого через элемент И 28 запрещено триггером 25Этот же сигнал переключает триггер 26, запрещая прохождение импульсов с блока 5 через элемент И 15 и разрешая поступление частоты с генератора импульсов 7 уа счетчик 2 (через элемент И 30) . Счетчик 2 через элемент ИЛИ 16 начинает выдавать импульсы на элемент И 17, 18 и 22, т.е. схема работает аналогично случаю прохождения импульсов с блоков оперативной памяти. При этом импульсы, поступающие со счетчика в момент включенного состояния триггера 20, вновь запоминается в этом счетчике 7 (элемент задержки 23 исключает возможность состязаний. При последующей отработке всех импульсов, заполненных в счетчике, он вырабатывает сигнал нулевого состояния, который обнуляет триггер 25 и через элементы ИЛИ 27 и И 28 поступает как сигнал Конец полной отработки на блок ввода программы и блоки буферной памяти. Этот же сигнал обнуляет триггер 26 (через элемент задержки 29), возвращая бло ки 8 и 9 в исходное состояние. При этом еслиПО одной координате отработка всех запомненных.импульсов произошла, а по другой еще не закон чена, то сигнал Конец полной отработки появится на выходе блока 9 только в конце отработки второй координаты. Таким образом.частота на выходе блоков 8 определяется только величи ной, нагрузки (т.е. частотой приемис тости шагового двигателя), и так ка частота с блоков 5 задается равной максимально возможному значению час тоты приемистости, а опрос счетчико производится частотой генератора-им пульсов, то частота управляющих импульсов на блоки 10 соответствует максимальному текущему значению частоты приемистости. Точность позиционирования при этом сохраняетсй, так как на выход блоков 8 выдается такое же количество импульсов которое поступило на входы этих бло ков. При необходимости ручного задания частоты управляющих импульсов, управление регулируемыми элементами задержки 21 производится с пуль та U. Введение координатных блоков ре гулирования частоты, логического блока позволяет при изменениях нагрузйи повысить быстродействие уст ройства при полном исключении потери точности позиционирования, а т,йкже расширить его область применения за счет изменения частоты уп равляющих импульсов (по одной или по обеим сразу координатам) с пуль та ручного управления для проведен различного рода наладочных работ. формула изобретения 1. Устройство для программного управления, содержащее генератор 7 мпульсов, датчики нагрузки, выхоами соединенные с коммутаторами, управляющие входы которых подключены к выходам пульта управления, и последовательно соединенные блок ввода программы, блок декодирования и интерполятор, а также первый и второй блоки управления шаговыми двигателями, отличающеес я тем, что, с целью расширения Области применения устройства, в него введены первый-и второй блоки регулирования частоты и логический блок, певыми входами соединенный с первыми выходами интерполятора, вторыми входами - с первыми выходами первого и второго блоков регулирования частоты, вторые выходь которых подключены соответственно к входам первого и второго блоков управления шаговыми двигателями, первые выходы логического блока соединены с .первыми входами первого и второго блоков регулирования частоты, второй выход логического блока подключен к первым входам интерполятора и к бходу блока ввода программы, вторые входы первого и второго блоков регулирования частоты соединены с вторыми выходами интерполятора, а третьи входы - с выходами коммутатора. 2. Устройство по п. 1, о т л и чающееся тем, что блок регулирования частоты содержит первый . элемент задержки, последовательно соединенные, первый элемент И, элемент ИЛИ, второй элемент И, второй элемент задержки, счетчик импульсов и первый триггер, а также последовательно соединенные третий элемент И, третий элемент задержки, второй триггер.и четвертый элемент И, выходом соединенный с вторым выходом блока, выход элемента ИЛИ подключен к первому входу третьего элемента И, второй вход которого соединен с первым выходом второго триггера, второй выход которого подключен к второму входу второго элемента И,выход которого соединен с вторым входом первого триггера, выходом подключенного к первому выходу блока, второй вход счетчика импульсов соединен с первым входом блока, а второй выход счетчика им- . пульсов - с вторым входом элемента ИЛИ, выход третьего элемента И через первый элемент задержки подключен к второму входу второго триггера, первый и второй входы первого элемента И соединены соответственно с первыми входами блока.

Источники информации, принятые во внимание при экспертизе

fP ,кл. q 05 В 19/18,1975 прототип .

фиг:1

Авторы

Даты

1982-04-15—Публикация

1980-03-12—Подача