(54) УСТРОЙСТВО ДЛЯ ЧИСЛОВОГО ПРОГРАММНОГО УПРАВЛЕНИЯ СТАНКОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для числового программного управления станком | 1978 |

|

SU744465A1 |

| УСТРОЙСТВО ДЛЯ числового ПРОГРАММНОГОТ1:Х11/^1С.^;;-д^Е Ш5'БЛК-«Г^-д | 1979 |

|

SU826279A1 |

| Устройство стабилизации скорости резания для токарно-винтовых станков с числовым программным управлением | 1983 |

|

SU1180845A1 |

| Устройство для программного управления | 1985 |

|

SU1275373A1 |

| Система адаптивного числового программного управления металлорежущим станком | 1980 |

|

SU954945A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для кинематического дробления стружки на токарных станках с числовым программным управлением | 1981 |

|

SU1004974A1 |

| Устройство для числового программного управления | 1983 |

|

SU1124251A1 |

| Устройство для кинематического дробления стружки на токарных станках с числовым программным управлением | 1980 |

|

SU959036A1 |

I

Изобретение относится к автоматике и может быть использовано в устройствах числового программного управления (ЧПУ) металлорежущими станKai.

Известно устройство для прюграммнрго управления станками, содержащее соединенные между собой блок ввода программы, преобр азователь, блок памяти информации, интерполятор, блок управления приводом ЕЦ.

Недостатком указанного устройства является низкая точность отработки короткой серии импульсов на управляющей частоте, равной частоте приёмистости шагового двигателя и выше, за счет перебега суппорта станка в случае программирования малых перемещений отдельным кадром без разгона и торможения, ;что приводит к неисправимому браку деталей

Наиболее близким по технической сущности к предлагаемому является устройство ЧПУ, содержащее последрвательно соединенные блок ввода информации, преобразователь кода, блок буферной И бтюк рабочей памяти, интерполятор и шаговый привод с блоком управления, а также два ключа, элемент задержки, блок сравнения частоты, включающий в себя элементы И, ИЛИ, И-НЕ,.триггер, счетчик и инвертор. Один из выходов блока сравнения через первый ключ, а другой выход через блок временной залержки и второй ключ соединены с блоком преобразователя кода. Вход первого ключа и вход блока временной задержки соединены с выходом интерполятора 2 .

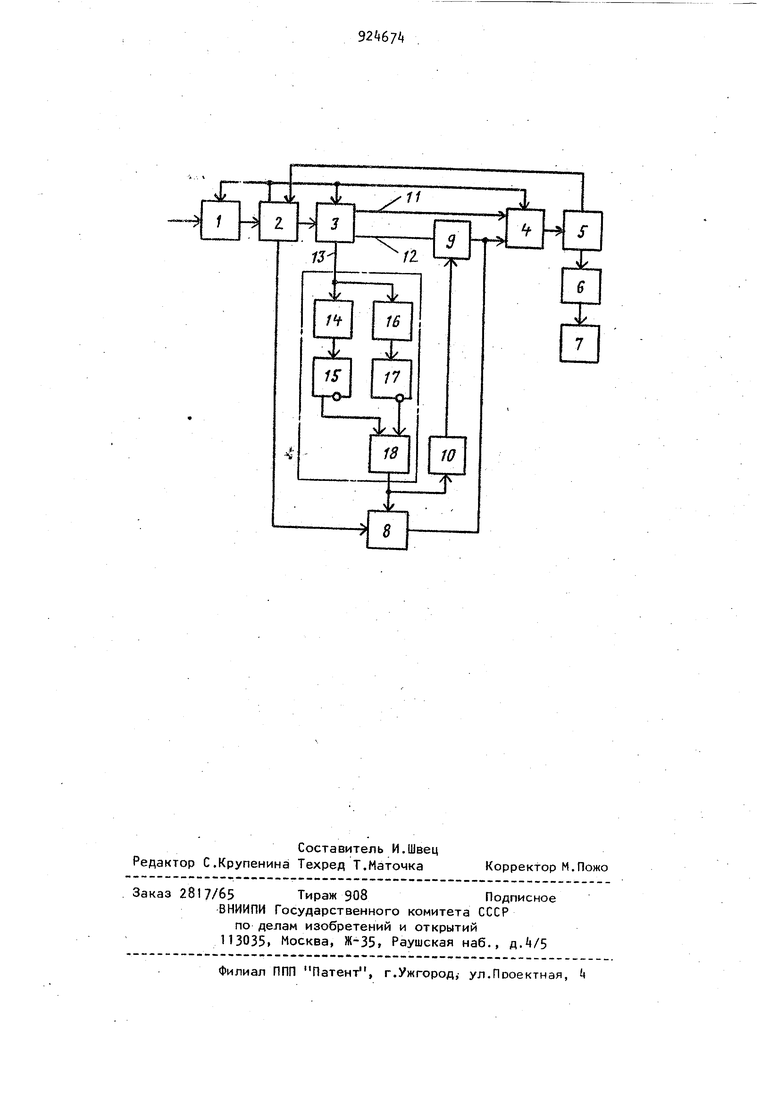

Недостатком известного устройства является также низкая точность отработки коротких серий импульсов, так как на частоте, близкой к частоте приемистости, двигатель не успевает перейти в устойчивый режим работы, вследствие чего происходит сбой в работе шагового двигателя, приводяв|ий к браку обрабатываемых деталей. Цель изобретения - исключение сбоев работы устройства при отработке коротких перемещений. Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные блок вво да информации, преобразователь кода, блок буферной памяти, блок рабочей памяти, интерполятор, блок управлени и шаговый привод, второй выход блока буферной памяти через последователь но соединенные первый счетчик импуль сов и первый триггер соединен с первым входом элемента И, второй выход преобразователя кода через первый ключ подключен к второму входу блока рабочей памяти, который .через второй ключ соединен с третьим выходом блок буферной памяти, вторым входом под, ключенного к третьему выходу преобразователя кода, к второму входу бло ка ввода информации и к третьему вхо ду блока рабочей памяти, второй выход интерполятора соединен с вторым входом преобразователя кода, введены элемент НЕ и последовательно соединенные второй счетчик импульсов и второй триггер, выходом соединенный с вторым входом элемента И, выход ко торого через элемент НЕ подключен к второму входу второго ключа, а вход второго счетчика импульсов соединен с вторым выходом блока буферной памяти . На чертеже представлена структурная схема устройства. Устройство содержит блок 1 ввода информации, преобразователь 2, блок 3 буферной памяти, блок k рабочей па мяти, интерполятор 5 и блок 6 управления шаговым приводом 7 соединенные последовательно, первый ключ 8, второй ключ 9, элемент НЕ 10, канал 11 переписи информации на величину перемещения из буферной памяти в рабочую, канал 12 переписи информации на скорость перемещения (частоту отработки) из буферной в рабочую память, канал 13 передачи информации на величину перемещения из буферной памяти, первый счетчик 14 импульсов : первый триггер 15, второй счетчик 16 импульсов, второй триггер 17 и элемент И 18. Выход преобразователя 2 кодов соединен с первым ключом 8, соединенным с вторым входом блока 4 рабочей памяти, котогэый соединен с вых.р94 дом второго ключа 9 вход которого соединен с элементом НЕ 10. Второй выход блока 3 буферной памяти соединен с входами счетчиков 1i. и 16, выходы которых соединены с входами триггеров 15 и 17 соответственно. Единичный выход триггера 15 и инверсный выход триггера 17 подключены к соответствующим входам элемента И, выход которого соединен с элементом НЕ 10 и входом ключа 8. Устройство работает следующим образом. Информация о величине и скорости перемещения с программоносителя (не показан) считывается блоком 1 ввода информации, преобразуется в последовательный двоичный код в преобразователе 2, записывается, в блок 3 буферной памяти, переписывается в блок рабочей памяти и отрабатывается в интерполяторе 5 выходной сигнал ко торого через блок 6 управляет шаговым приводом 7. Одновременно с началом отработки интерполятором 5 очередного кадра программы производится считывание и запись в блок 3 буферной памяти поЬледующего кадра. По окончании отработки кадра интерполятор 5 формирует сигнал Конец отработки кадра, по которому преобразователь 2 вырабатывает сигналы переписи информации из блока 3 буферной памяти в блок k рабочей памяти и сигнал считывания следующего кадра. Перед каждым циклом измерения (перед записью в буферную память очередного кадра) счетчики 14 и 16 и триггеры 15 и 17 установлены в нулевое состояние. При этом на единичном выходе первого триггера 15 сигнал уровнем О, на нулевом (инверсном) выходе второго триггера 17 сигнал уровнем 1, на выходе элемента И сигнал уровнем О. Сразу после записи в блоке 3 буферной памяти очередного кадра сигнал в виде последовательного двоичного кода, несущий информацию о величине перемещения, по каналу 13 записывается одновременно в счетчики 14 и 16. При поступлении четвертого импульса счетчик 14 (до 4) вырабатывает импульс переполнения, который меняет состояние первого триггера 15 на единичном выходе которого возникает

сигнал уровнем 1. При этом выполняется условие совпадения на элементе И 18, выходной сигнал которого становится равным 1,

Этот сигнал открывает первый ключ 8 и через элемент НЕ 10 закрывает второй ключ 9. При этом через открытый первый ключ 8 в блок 4 рабочей памяти переписывается информация на низкую (например 100 Гц) частоту от работки из преобразователя 2.

При поступлении последующих импульсов до пятнадцатого включительно триггеры 15 и 17 и элемент 18 не изменяют своего состояния.

При поступлении шестнадцатого импульса счетчик 16 (до 16) вырабатывает импульс переполнения, который изменяет состояние второго триггера 17 на нулевом выходе которого возникает сигнал уровнем О. Выходной сигнал элемента И 18 становится равным О и ключ 8 закрывается, а ключ 9 открывается. При этом перепись информации на скорость перемещения (частоту отработки) в блок k рабочей памяти производится по каналу 12 через открытый ключ 9Таким образом, при наличии в программе информации на перемещение короткой серии (-15) импульсов запрогграммированная частота отработки заменяется на фиксированную низкую частоту, что исключает сбои шагового привода при отработке таких перемещений.

Так как обеспечивается устойчивый режим работы шагового приво да, повышается качество обрабатываемых деталей..

Формула изобретения - Устройство для числового программного управления станком, содержащее

последовательно соедийенные блок ввода информации, преобразователь кода блок буферной памяти, блок рабочей памяти, интерполятор, блок управления и шаговый привод, второй выход блока буферной памяти через последовательно соединенные первый счетчик импульсов и первый триггер соединен с первым входом элемента И, второй выход преобразователя кода через первый ключ подключен к второму входу блока рабочей памяти, который через второй ключ соединен с третьим выходом блока буферной памяти, вторым входом подключенного к третьему выходу преобразователя кода, к второму входу блока ввода информации и к третьему входу блока рабочей памяти , второй выход интерполятора соеди|нен с вторым входом преобразователя кода, отличающееся тем, что, с целью исключения сбоев работы устройства при отработке коротких перемещений, в него введены элемент НЕ и последовательно соединенные второй счетчик импульсов и второй триггер, выходом соединенный с вторым входом элемента И, выход которого через элемент НЕ подключен к второму входу второго ключа, а вход второго счетчика импульсов соединен с вторым выходом блока буферной памяти.

Источники информ:эции, принятые во внимание при экспертизе

Авторы

Даты

1982-04-30—Публикация

1980-10-01—Подача