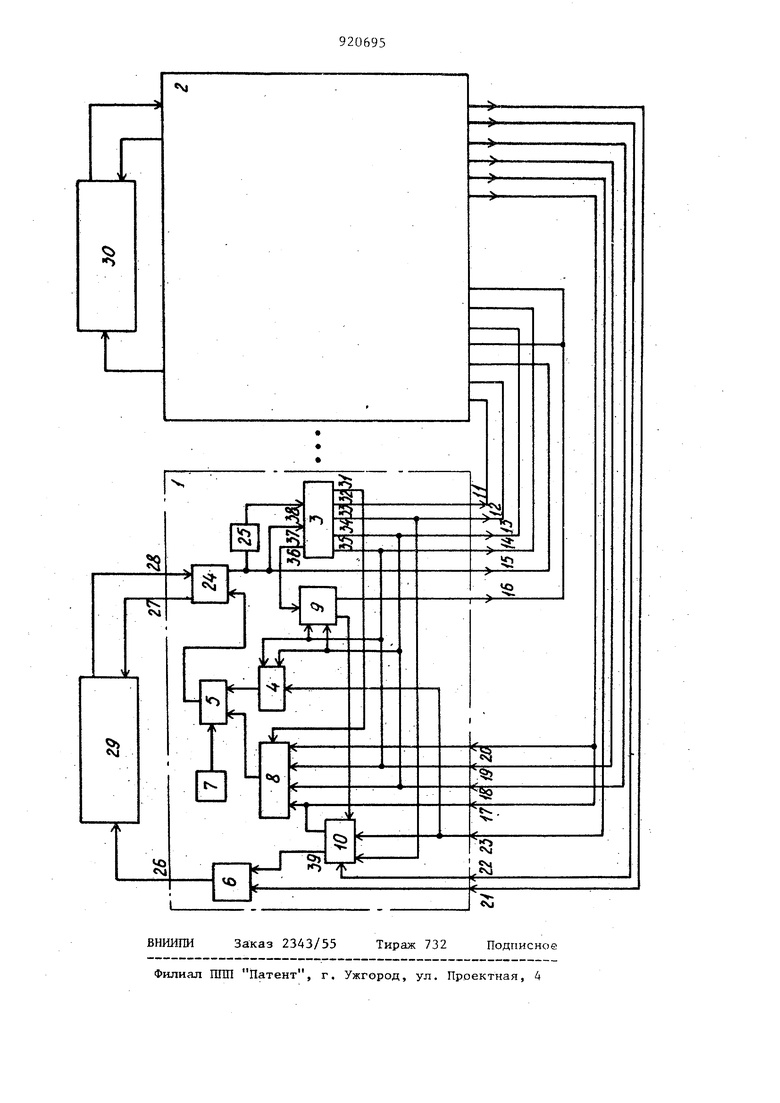

мутатор и блок усилителей, причем выходы регистра адреса вектора канала, регистра состояния канала и буферного регистра канала через коммутатор канала соединены с первым вхо™ дом блока усигчтелей канала, первый выход блока усилителей канала через деш}|фратор адреса канала соединен с разрешатадим входом дешифратора управляющих сигналов канала, с информационными входами буферных регист ров каналов и с кодовым входом деЕгн™ фратора управлягацих сигналов какала первый выход дешифратора управляющих сигналов канала соединен с управляю1ДИМ входом регистра состояния канала, первый и второй установоч1- ые входы регистра состояния соединены соответственно с вторым и третьим выходами дешифратора згправля ющих сигнал9в каналов, четвертый выход дешифратора управляющ -1х сигналов канала соединен с первыми входамиблока прерываний каналов, выход блока прерываний канала соединен со входом прерывания соответствующей ЦВМ, вторые вход и выход блока усилителей канала соединены соответственно с информадионнь ми выходом и входом соответствующей ЦВМ, второй и третий выходы дешифратора управляющих сигналов канала соединены соответственно с первым и вторым разрешающимрг входами буферного регистра канала, в каждый канал введены: триг гер синхронизации и дешифратор номера ЦВМ, причем второй, третий и пятый выходы дешифратора управляющи сигналов канала соединены соответственно с первым, вторым гасящими и с установочными входами триггера синхронизации каналаj прямой выход триггера синхронизации канала соеди нен с третьим и четвертым установоч ными входами регистров состояния каналов, шестой выход дешифратора у равляющих сигналов канала соединен первым разрешающий входом дешифра.тора номера ЦВМ канала и со вторыми разрешающими входами дешифратора но мера ЦВМ всех каналов, инверс1Я11й выход триггера синхронизации канала соединен с третьим разрешакщим входом регистра состояния канала, первый .выход блока усилителей кан-ала соединен с информационными дешифраторов номера ЦВМ всех канало а первый и второй выходы дешифратора номера ЦВМ канала соединены сответственно со аторым входом блока прарыва1мй канала и с четвертым усановочным входом регистра состояния канала. Структурная схема устройства представлена на чертеже. Многоканальное устройство обмена для многомашинной вычислительной системы содержит каналы н 2 - кшкдый из которых выполнен в виде дешифра, тора 3 управляюпшх сигналов; буферного регистра 4, коммутатора 5; блока 6 прерыванийS регистра 7 адреса вектора, регистра 8 состояли, триггера 9 синхронизации, дешифратор 10 номера ЦВМ, выходов li-sBj входов 17™23j блока 24 усшчителей, дешифра™ тор 25 адреса, выходов 26 и 27,. входа 28, Еозицняма 29 и 30 обозначень; ЦВМ, позициями 31 - 36 - выходы, позициями 37 и 38 - входы дешифратора управляющих , позици ей 39 выход деагифратора номера UBM Устройство способно работать в режиме программных операций с опросом флага или в режиме программных операций с использованием средств прерывания програ; 1м Ка -:дому режиму обмена соответствукот свои адреса обращения к устройству. Режим передачи данных из одной ма-маши} Ы во все другие посредством программных операций с опросом флага - следу ш;ий, В первом ци1сае обращения к каналу адрес устройства At проходит через блок 24 и старшие разряды адреса поступают на вход дешифратора адреса 25, Дешифратор адреса 25 разрешает работу дешифратора управляющих cariiajioB 3 по входу 38, Дешифратор управляющих сигналов 3 анализирует младшие разряды адреса АК поступающие на вход 37,, и на выходе 36 вырабатывает снгнгш, устанавливающий триггер синхронизации 9. С прямого выхода триггера синхронизации 9 во внешний интерфейс поступает выходной сигнал 16, свидетельствующий о готовности машинь к передаче информации. Информационная часть цикла обращения к каналу значения не имеет. Далее передающая машина обращается к устройству по адресу А2 в цикле Ввод, принимает содержимое .регистра состояний 8 и анализирует его первый разряд, значение которого определяется входным сигналом 16 внешнего интерфейса. AKTHBIMH уровень сигнала свидетельствует о готовности всех машин к обмену информацией. Как только все машины готовы к обмену информацией, передающая машина обращается к устройству по адресу A3 в цикле Вьш од. В информационной части цикла переда ваемые данные через блок 24 поступают во внешний интерфейс по параллельным линиям 15. Параллельно данным во внешний интерфейс с выхода 35 дешифратора управляющих сигналов 3 поступает стробирующий сигнал 14. В приемной машине данные с линий внешнего интерфейса 15 поступают на входы буферного регистра 4 ,и записываются в него по входному сигналу внешнего интерфейса 19. Одновременно сигнал с выхода 35 сбрас вает триггер синхронизации 9 и уста навливает второй разряд регистра состояний 8, активный уровенькоторого означает, что в буферный регистр 4 записаны данные. Следующее слово данных передается аналогично. Приемные машины в первом цикле Вывод обращаются к своим устройствам обмена по адресу А1 и устанавливают триггер синхронизации 9. Затем приемные машины обращаются к устройству по адресу А2 в цикле Ввод, при нимают содержимое регистра состояний 8 и анализируют его второй разряд. В случае, если эТот разряд установлен, приемные, машины в цикле Ввод по адресу A3 обращаются к устройству и принимают данные из бу ферного регистра 4. При этом сигнал с выхода 31 дешифратора управляющих сигналов 3 сбрасывает второй и трети разряды регистра состояний 8. Следующее слово данных принимается аналогично. Передача команды из одной машины во все другие посредством программных операций с опросом флага проходит аналогично передаче данных, но в третьем цикле передающая машина вместо адреса A3 обращается к уст ройству по адресу А4. При этом на вы ходе 34 дешифратора управлякицих сигналов 3 вырабатывается выходной сигнал 13. В устройствах приемных машин сигнал 18 стробирует запись-ко манды в буферный регистр 4, сбрасывает триггер синхронизации 9 и устанавливает третий разряд регистра 956 состояний 8, информируя приемную машину о том, что в буферном регистре 4 хранится команда. При обмене информацией только между двумя маши- нами многомашинного вычислительного комплекса передающая машина в первом цикле Вывод обращается к устройству по адресу АЗ, и на выходе 33 дещифратора управлякщих сигналов 3 вырабатывается сигнал 12. В информационной части во внеш1шй интерфейс передается номер приемной машины по линиям 15. В устройстве адресуемой машины со стороны внешнего интерфейса на номер машины поступает на-вход 23 и на информационный вход дешифратора номера машины 10, сигнал 22 разрешает работу дешифратора 10, и если в адресуемой ЦВМ взведен триггер синхронизации 9, во внешний интерфейс поступает сигнал 16. В устройстве передающей машины сигнал 17 устанавливает 4-й разряд регистра состояний 8, свидетельствующий о готовности приемной ЦВМ к обмеггу информацией. Передающая машина вводит содержимое регистра состояний 8 и анализирует его 4-й разряд. Если разряд установлен, передающая машина выводит передаваемую информацию по адресу A3. Следующее информационное слово передается аналогично. Устройство приемной ма1ш{ны работает аналогично случаю передачи информации во все машины комплекса. Обмен информацией может проходить посредством программьсых операций с использовагшем средств прерывания программы. Логика прерыватшя выраба- тывает в. ЦВМ сигнал требова(шя прерывания программы в двух случаях. В первом случае передающая машина, требуя прерывагще программы во всех приемных машинах, обращается к своему устройству по адресу А5 и на выходе 32 дешифратора управляюцщх сигналов 3 вырабатывается во внешний интерфейс сигнал i . Во всех приемных машинах входной сигнал 21 инициирует работу блока прерывания 6 независимо от состояния триггера синхронизации 9. Изобретение позволяет сократить исло программных операций и повыить быстродействие вычислительноо комплекса при обмене ииформагу й между двумя машинами. 7 Формула изобретения Многоканальное устройство обмена для многомашинной вычислительной системы, содержа дее в кaждo канале блок прерываний, дешифратор адреса, де иифратор управляющих сигналов, ретистр состояния, буферный регистр, регистр вектора, коммутатор и блок усилителей., причем выходы регистра адреса вектора канала, регистра состояния канала и буферного регистра канала через коммутатор кагтала соединень с первь м входом блока усилителей канала, первый выход блока усилитепей канала через дешифратор адреса канала соединен с разрешающим входом дешифратора управляющих сигналов канала с информационными входами буферных, регистров каналов и с кодовым входом дешифратора .управляющих сигналов канала, .первый выход дешифратора упра ляюяу-гх сигналов канала соединен с унраЕляютшм входом регистра состояния канала, первый и второй установ ные входы регистра состояния канала соединены соответственно с, вто и третьим выходами дешифратора управля ощих сигналов каналов, четвертый выход дешифратора yпpaвляюш x с налов канала соединен с первыми вхо дами блока прерываний каналов, выхо С5лока прерываний канапа соединен с входом прерыв 1ния соответствующей ЦВМ, вторые вход и выход блока усил телей канала соединены соответствен но с информационными выходом и входом соответствукхцей ЦВМ, второй и третий выходы дешифратора управляющих сигналов канала соединены соот9ветственно с первым и вторым разрешакядими входами буферного регистра канала, отличающееся тем, что, с целью повышеш1я быстродействия, оно содержит в каждом канале триггер синхронизации и дешифратор номера ЦВМ, причем второй, третий и пятый выходы дешифратора управляющих сигналов канала соединены соответственно с первьгм, вторым гасящими и с установочными входами триггера синхронизации канала, прямой выход триггера синхронизации канала соединен с третьим и четвертымустановочными входами регистров состояния каналов, шестой выход дегиифратора управляющих сигналов канала соединен с первым разрешающим входом дешифратора номера ЦВМ канала и с вторыми разрешающими входами дешифратора номера ЦВМ всех каналов, инверсный выход триггера синхронизации канала соединей с третьим разрешающим входом регистра состояния канала, первый выход блока усилителей канала соединен с информационнь ми входами дешифраторов номера ЦВМ всех каналов, а первый и второй выходы дешифратора номера ЦВМ канала соединены соответственно со вторым входом блока прерываний канала и с четвертым установочным входом регистра состояния канала. I Источники информации, принятые во внимание при экспертизе 1.Патент CDJA № 4004279, кл. G Об F 3/04, опублик.1977. 2.Microcomputer handbook. Каталог фирмы Digital Equipment Corporation 1976, p. 16, f-I о 1-3 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Авторы

Даты

1982-04-15—Публикация

1980-05-22—Подача