(54) yCTPOActBO ДЛЯ ПРОВЕРКИ ПОЛНОТЫ ТЕСТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностического контроля выполнения проверок | 2016 |

|

RU2631989C1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Способ диагностики отказов динамических объектов и устройство для его осуществления | 1990 |

|

SU1718190A1 |

| Устройство для автоматического контроля блоков памяти | 1976 |

|

SU610180A1 |

| Устройство для контроля генератора случайных чисел | 1983 |

|

SU1087993A1 |

| Устройство для формирования тестов | 1974 |

|

SU477413A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| УСТРОЙСТВО И СПОСОБ КОНТРОЛЯ ЦЕЛОСТНОСТИ СИСТЕМЫ | 2020 |

|

RU2752811C1 |

1

Изобретение относится к вычислительной технике и может быть использовано для составления тестов сложных цифровых систем.

Известно устройство для контроля цифровых модулей и проверки качества тестов, модель объекта контроля, блок сравнения, эталонный блок, счетчики обнаруженных и вводимых неисправностей, блок управления, блок ввода неисправностей 1.

Недостатком данного устройства является большое время, требуемое для оценки полноты тестов, обусловленное необходимостью перебора множества заданных неисправностей.

Наиболее близким к предложенному является устройство формирования тестов, содержащее генератор случайных чисел, счетчики тактов, блок управления 2.

Недостатком такого-устройства является также большое время формирования оптимального теста, связанное со случайным перебором большого количества

различных вариантов тестов и последующей их оценкой по всему шожеству неисправностей.

Цель изобретения - сокращение времени проверки.

Эта цель достигается тем, что в устройство для проверки полноты тестов, содержащее генератор тестов, выходы которого подключены к информационным входам модели объекта контроля и эта10лонного объекта контроля, выходы модели объекта контроля и эталонного объекта контроля соединены с соответствующими входами схемы сравнения, въкод которой соединен со входом счетчика

15 числа обнаруженных неисправностей и первым входом блока управления, первый, второй выходы и второй вход которого соединенъ с соответствующими входами и выходом генератора тестов, второй

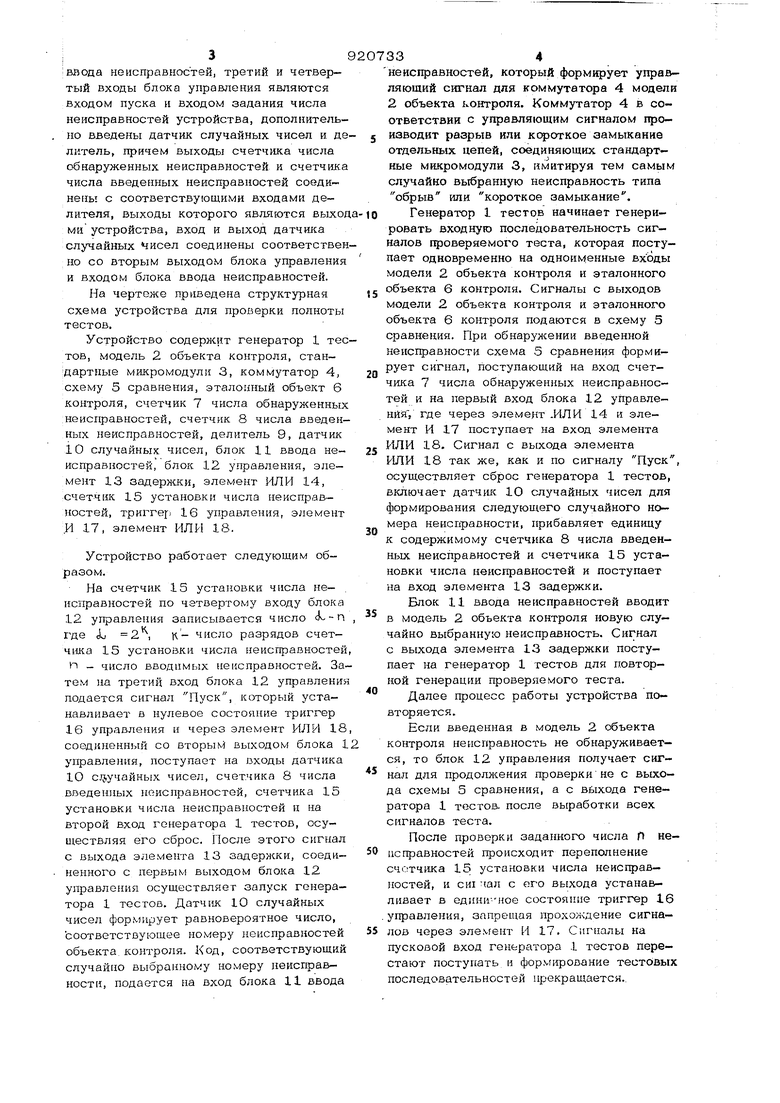

20 выход блока управления соединен со Входом счетчика числа введенных неисправностей, управляющий ВХОД; модели объекта контроля соединен с выходом блока ввода неисправностей, третий и четвертый входы блока управления являются входом пуска и входом задания числа неисправностей устройства, дополнитель}ю введены датчик случайных чисел и де литель, причем выходы счетчика числа обнаруженных неисправностей и счетчик.а числа введенных неисправностей соединены с соответствующими входами делителя, выходы которого являются выхо ми устройства, вход и выход датчика случайных Чисел соединены соответствен но со вторым выходом блока управления и входом блока ввода неисправностей. На чертеже приведена структурная схема устройства для проверки полноты тестов. Устройство содержит генератор I тес тов, модель 2 объекта контроля, стандартные микромодули 3, коммутатор 4, схему 5 сравнения, эталонный объект 6 контроля, счетчик 7 числа обнаруженных неисправностей, счетчик 8 числа введенных неисправностей, делитель 9, датчик 10 случайных чисел, блок 11 ввода неисправностей, блок 12 управления, элемент 13 задерл ки, элемент ИЛИ 14, счетчик 15 установки числа неисправностей, триггер 16 управления, элемент И 17, элемент ИЛИ 18. Устройство работает следующим образом. На счетчик 15 установки числа неисправностей по четвертому входу блока 12 управления записывается число L-n где iL 2, к- число разрядов счетчшса 15 установки числа неисправностей tn число вводимых неисправностей. За тем на третий вход блока 12 управления подается сигнал Пуск, который устанавливает в нулевое состояние триггер 16 управления н через элемент ИЛИ 18 соединенный со вторым выходом блока 1 управления, поступает на входы датчика 1О cJ}yчaйныx чисел, счетчика 8 числа введенных неисправностей, счетчика 15 установки числа неисправностей и на второй вход генератора 1 тестов, осуществляя его сброс. После этого сигнал с выхода элемента 13 задержки, соединенного с первым выходом блока 12 управления осуществляет запуск генератора 1 тестов. Датчик 10 случайных чисел формирует равновероятное число, соответствующее номеру неисправностей объекта, контроля. Код, соответствующий случайно выбранному номеру неисправности, подается на вход блока 11 ввода ненсправностей, который формирует управляющий сигнал для коммутатора 4 модели 2 объекта контроля. Коммутатор 4 в соответствии с управляющим сигналом производит разрыв или Kt OTKoe замыкание отдельных цепей, соединяющих стандартные микромодули 3, имитируя тем самым случайно выбранную неисправность типа обрыв или короткое замыкание. Генератор 1 тестов начинает генерировать входную последовательность сигналов проверяемого теста, которая поступает одновременно на одноименные входы модели 2 объекта контроля и эталонного объекта 6 контроля. Сигналы с выходов модели 2 объекта контроля и эталонного объекта 6 контроля подаются в схему 5 сравнения. При обнаружении введенной неисправности схема 5 сравнения формирует сигнал, поступающий на вход счетчика 7 числа обнаруженных неисправностей и на первый вход блока 12 управления, где через элемент .ИЛИ 14 и элемент И 17 поступает на вход элемента ИЛИ 18. Сигнал с выхода элемента ИЛИ 18 так же, как и по сигналу Пуск, осуществляет сброс генератора 1 тестов, включает датчш 1О случайных чисел для формирования следующего случайного номера неисправности, прибавляет единицу к содержимому счетчика 8 числа введенных неисправностей и счетчика 15 установки числа неисправностей и поступает на вход элемента 13 задержки. Блок 11 ввода неисправностей вводит в модель 2 объекта контроля новую случайно выбранную неисправность. Сигнал с элемента 13 задержки поступает на генератор 1 тестов для повторной генерации проверяемого теста. Далее процесс работы устройства повторяется. Если введенная в модель 2 объекта контроля неисправность не обнаруживается, то блок 12 управления получает сигнал для продолжения проверкине с выхода схемы 5 сравнения, а с выхода генератора 1 тестов- после выработки всех сигналов теста. После проверки заданного числа П не- исправностей происходит переполнение счситчика 15 установки числа неисправностей, и СИ1иал с его выхода устанавливает в едини-ное состояние триггер 16 управления, запрещая прохолчдение сигна- лов через элемент И 17. СИГЕШЛЫ на пусковой вход генератора 1 тестов перестают поступать и формирование тестовых последовательностей прекращается.. 5 К этому времени иа счетчике 7 числ обнаруженных неисправностей записано число .ТТЛ обнаруженных неисправностей, на счетчике 8 числа введенных неисправ ностей - общее число л введенных неисправностей, на делителе 9 - относитель число ( mjf обнаруженных неисг завностей, определяющее полноту теста формула изобретения Устройство для проверки полноты тес тов, содержащее генератор тестов, выхо ды которого подключены к информационным входам модели объекта контроля и эталонного объекта контроля, выходы модели объекта контроля и эталонного объекта контроля соединены с соответст вующими входами схемы сравнения, выхо которой соединен со входом счетчика числа обнаруженных неисправностей и первым входом блока управления, первый втчрой выходы и второй вход которого соединены с соответствующими входами и выходом генератора тестов, второй 33 выход блока управления соединен со Входом счетчика числа введенных неисправностей, управляющий вход модели объекта контроля соединен с выходом блока ввода неисправностей, третий и четвертый входы блока управления являются входом пуска и входом задания числа неисправностей устройства) отличающееся тем, что, с целые сокращения времени гфоверки, в него введены датчик случайных чисел и делитель, причем выходы счетчика числа обнаруженных неисправностей и счетчика числа введенных неисправностей соединены с соответствующими входами делителя, выходы которого являются выходами устройства, вход и выход датчика случайных чисел соединены соответственно со вторым выходом блока управления и входом блока ввода неисправностей. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 519713, кл. е 06 F 11/00, 1977. 2.Авторское свидетельство СССР № 477413, кл. О-06 F 11/00, 1976.

Авторы

Даты

1982-04-15—Публикация

1980-04-04—Подача