1

Изобретение относится к области вычислительной техники. Оно может быть использовано в системах автоматического контроля цифровых интегральных схем, а также блоков и устройств средств вычислительной техники ири их производстве и эксплуатации.

Известны устройства для формирования проверочных тестов, входящие в системы функциональной проверки сложных интегральных схем и содержащие задающий генератор, счетчик тактов, генератор случайных чисел (на базе сдвигового регистра с линейной обратной связью), выходной регистр и формирователь уровней (генераторы ступенек) .

Выход задающего генератора через сдвигающий регистр подключен к управляющим входам генератора случайных чисел, выходы которого соединены с информационными входами выходного регистра, управляющие входы этого регистра связаны с выходами сдвигающего регистра, а управляющие входы последнего подключены к входу счетчика тактов, выходы выходного регистра соединены с формирователем уровней.

Однако известные устройства обладают рядом недостатков. Один из них заключается в том, что для распределения во времени информации, поступающей из генератора случайных чисел на входы выходного регистра,

используется сдвиговый регистр, число разрядов которого должно быть равно числу входов объекта контроля. Аналогичное число разрядов должен иметь и генератор случайных

чисел. Это приводит к большим затратам оборудования в случаях контроля объектов с большим числом входов (например, печатных плат с интегральными схемами, где число входов может достигать нескольких сотен).

Другой недостаток известных устройств состоит в ограниченности функциональных возможностей. В частности, устройства не имеют средств для задания программы синхронизации объекта контроля, средств для

приложения произвольных (детерминированных) тестов к объекту контроля, а также средств изменения псевдослучайных тестов как по виду, так и по длине. Отсутствие возможностей задания программы синхронизации

и тактов этой программы, в которые разрешается лодача псевдослучайных тестов на логические входы объекта контроля, либо приводит к существенному увеличению времени, необходимого для проверки синхронных объектов, либо снижает эффективность проверки объектов на псевдослучайных тестах.

Невозможность задания произвольных (детерминированных) тестов в комбинации с псевдослучайными делает известные устройства непригодными для объектов, имеющих

длинные последовательности начальной установки (т. е. последовательности, приводящие объект Б известное начальное состояние), которые не могут быть заданы вручную и должны прикладываться к объекту от внешней программируемой апнаратуры.

Отсутствие средств для изменения псевдослучайных тестов не позволяет использовать известные устройства для целей выбора и проверки качества тестов на основе аппаратного моделирования неисправностей объекта контроля.

Предлагаемое изобретение устраняет указанные недостатки.

Целью его является сокращение оборудования и расширение класса формируемых тестов.

Сущность изобретения заключается в том, что в устройство введены дешифратор адреса, дешифратор выходов синхронизации, регистр начальных условий, коммутатор, схемы сравнения и счетчик логических выходов, счетчик выходов синхронизации, счетчик тактов синхронизации, управляющие входы которых и управляющий вход счетчика тактов соединены с соответствующими выходами блока управления, выходы упомянутых счетчиков подключены к первым входам соответствующих схем сравнения, выходы которых соединены с соответствующими входами блока управления, вторые входы подключены к соответствующим выходам регистра начальных условий, вход которого через коммутатор соединен со входом устройства, выход коммутатора подключен к информационному входу генератора случайных чисел, выход счетчика логических выходов через дешифратор адреса соединен с управляющим входом выходного регистра, выход счетчика выходов синхронизации через дешифратор выходов синхронизации подключен ко второму входу формирователя уровней, управляющий вход дешифратора выходов синхронизации подключен к соответствующему выходу блока управления, соединенного с соответствующими входом и выходом устройства.

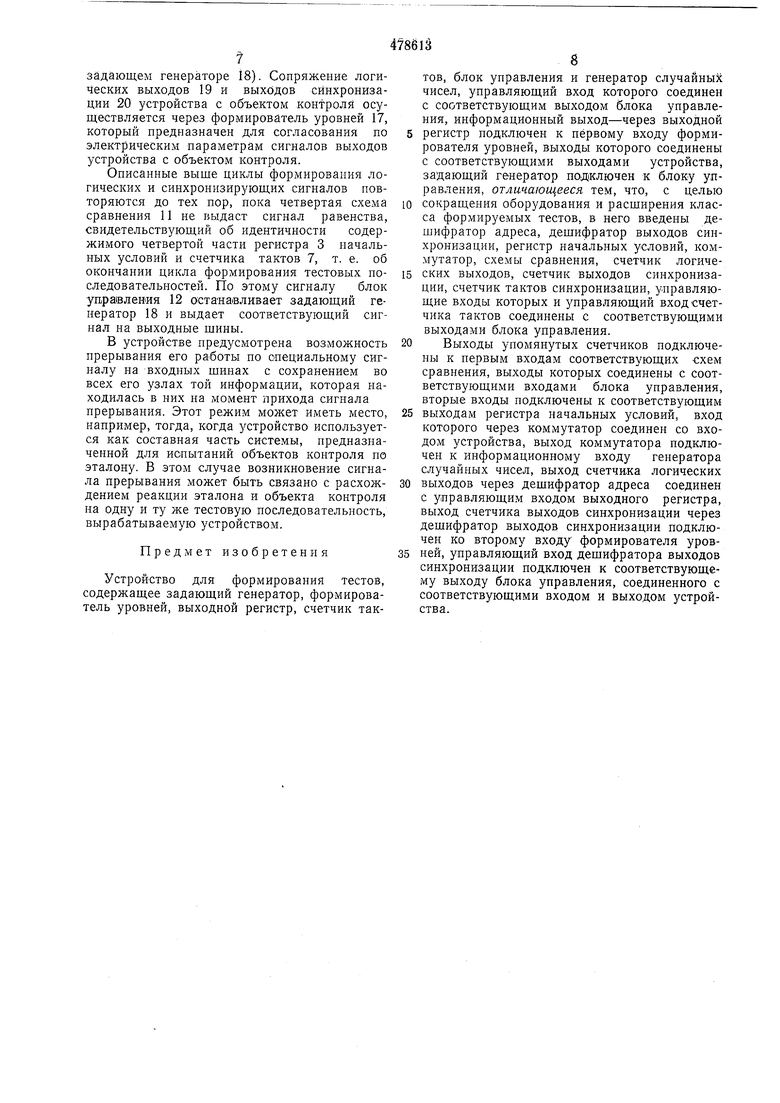

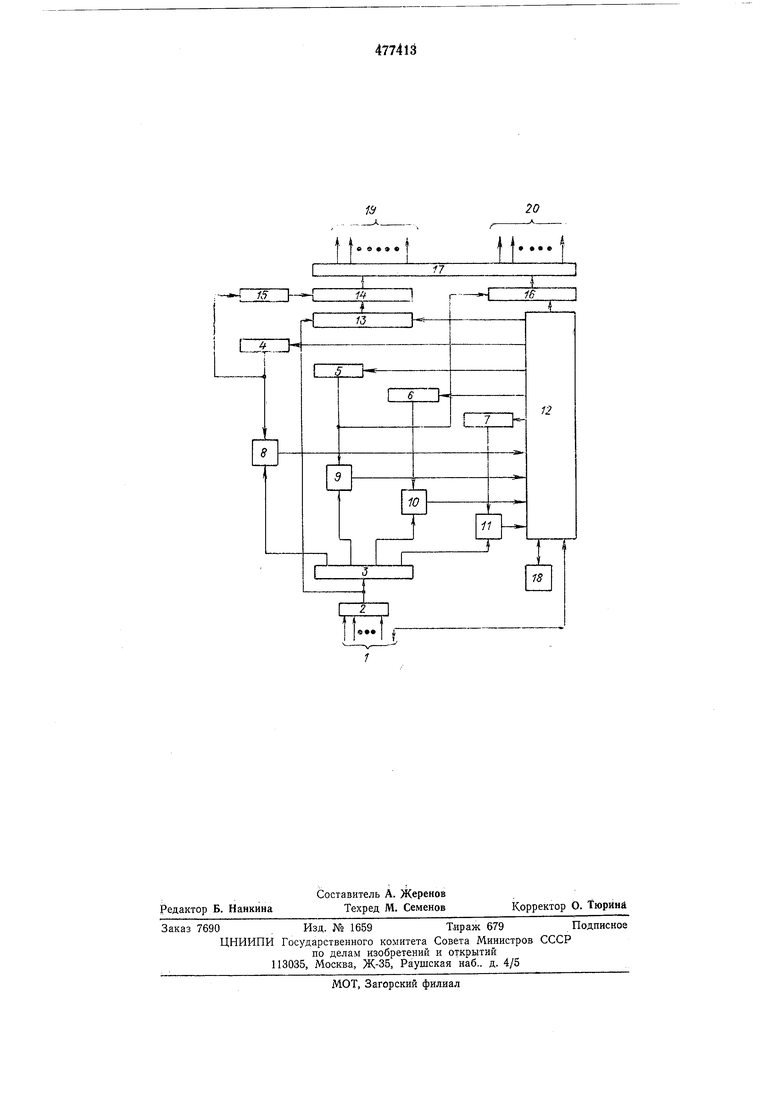

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит: вход 1, связывающий его (при необходимости) с внешним программируемым источником тестов и начальных условий (например, ЦВМ); коммутатор 2, распределяющий поступающую по входным шинам информацию в определенные группы разрядов регистра 3 начальных условий, который хранит эту информацию в процессе работы, тем самым давая возможность внешнему программируемому источнику данных решать в это время другие задачи; счетчик 4 логических выходов, счетчик 5 выходов синхронизации, счетчик 6 тактов синхронизации и счетчик тактов 7, задачами которых соответственно являются образование адресов логических выходов и выходов синхронизации, связанных с одноименными входами объекта контроля.

Подсчет числа импульсов синхронизации и числа тактов проверки (где под тактом проверки подразумевается однократное приложение ко всем входам объекта контроля как логических сигналов, так и всех сигналов синхронизации, обеспечивающих работу объекта контроля в соответствии с существующими в

это время на его входах логическими сигналами); четыре схемы сравнения 8, 9, 10 и 11, которые сравнивают содержимое отдельных групп разрядов регистра 3 начальных условий и соответствующих счетчиков 4, 5, б и 7

и в случае их равенства выдают сигнал (равенства) на блок управления 12, выходы которого связаны с управляющими входами всех счетчиков 4, 5, 6 и 7 и генератора 13 случайных чисел (выполненного на базе сдвигающего регистра с линейной обратной связью), который либо генерирует псевдослучайную тестовую последовательность, либо получает информацию с выхода коммутатора 2 для формирования произвольной (детерминированной) тестовой последовательности.

Выход генератора 13 случайных чисел

связан со входом выходного регистра. 14,

предназначенного для компоновки тестовой

последовательности, длина которой определяется счетчи1ком 4 логических выходов с .помощью дешифратора адреса 15, выходы которого подключены к лправляющему входу выходного регистра 14. Дешифратор 16 выходов синхронизации управляется

выходами счетчика 5 выходов синхронизации и блока управления 12. Выходы дешифратора 16 выполняют функции выходов синхронизации устройства, которые так же, как выходы регистра 14 подаются на выводы

(входы) объекта контроля через формирователь уровней 17. В состав устройства входит также задающий генератор 18, функцией которого является синхронизация работы всего оборудования устройства для формирования

тестов через блок управления 12, который может управляться от внешнего программируемого источника по входу 1.

Работа устройства определяется содержимым регистра 3 начальных условий, информация в который заносится либо вручную с пульта (автономный режим работы, либо по входу 1 (централизо-ванный .режи(м), когда устройство находится под управлением внешнего .программируемого оборудования, например ЦВМ. Для упрощения связи с внешним оборудованием шины, подключаемые ко входу 1, организованы аналогично шинам стандартного сопряжения ЦВМ. В их число входят информационные, адресные и управляющие шины. Данные с информационных шин через коммутатор 2, управляемый адресными шинами, при наличии соответствующего сигнала на управляющих шинах поступают как в регистр 3 начальных условий, так и в генератор 13 случайных чисел (в случае формирования произвольных тестовых последовательностей) Содержимое регистра 3 определяет следующие параметры устройства для формирования тестов; число логических выходов - первая часть регистра, число выходов синхронизации - вторая часть, число импульсов синхронизации, которое должно быть приложено к выходам синхронизации в каждом такте проверки,-третья п число тактов проверки-четвертая часть регистра.

Один такт .проверки предусматривает установку сигналов па всех используемых логических выходах и выдачу полного цикла синхронизации. После этого вручную или по сигналу с управляющих шин запускаются задающий генератор 18 и блок управления 12, который вырабатывает ряд сигналов управления. По первому из них, если отсутствует сигнал равенства на выходе первой схемы сравнения 8, содержимое старшего разряда генератора 13 случайных чисел записывается в определенный (к-й) разряд выходного регистра 14, адрес которого определен счетчиком 4 логических выходов, управляющим дешифратором адреса 15. Затем блок управления 12 увеличивает содержимое счетчика логических выходов на единицу и вырабатывает сигнал сдвига на один разряд содерл имого генератора 13 случайных чисел, значение старшего разряда которого теперь будет записано в следующий разряд выходного регистра. Аналогичные действия производятся блоком управления 12 до тех пор, пока первая схема сравнения 8 не выработает сигнал, указывающий на окончание логических выходов, который заставит блок управления 12 перейти к анализу содержимого второй части регистра 3 начальных условий. Если это содержимое равно нулю, что соответствует отсутствию входов синхронизации у объекта контроля (это может иметь место, например, при проверке комбинационных объектов), то блок управления 12 увеличит па единицу содержимое счетчика тактов 7, сбросит счетчик 4 логических выходов п значение старшего разряда генератора 13 случайных чисел вповь запишется в /с-й разряд выходного регистра 14. Этот цикл будет повторяться до тех пор, пока четвертая схема сравнения 11 не выдаст сигнал равенства, который указывает блоку управления 12 об окончании цикла формирования тестовых последовательностей. Как уже указывалось, генератор 13 случайиых чисел выполнен на базе сдвигающего регистра с линейной обратной связью, который способен вырабатывать псевдослучайную последовательность с максимальным периодом повторения 2 -1, где п - числоразрядов в сдвигающем регистре.

Линейная обратная связь осуществляется с помощью сумматора по модулю два содержимого старшего разряда сдвигающего регистра и специально подобранного разряда. В описываемом устройстве используется 25-разрядный сдвигающий регистр, обратная связь

у которого снимается с 25-го и либо с 3-го, либо с 7-го разрядов, что дает возможность вырабатывать с его помощью тестовую последовательность с максимальным периодом

7 33554431 и с изменяемым законом распределения.

Таким образом, первая часть регистра 3 начальных условий, первая схема сравнения 8, счетчик 4 логических выходов и дешифратор адреса 15 составляют ту часть оборудования устройства, которая позволяет поочередно вырезать из последовательности с максимальным периодом случайные числа (входные наборы сигналов для объекта контроля), имеющие длину, определяемую содержимым первой части регистра 3 начальных условий и которая выбирается равной числу логических входов объекта контроля. Если содержимое второй, третьей и четвертой частей регистра начальных условий не равно пулю, то блок управления 12 переходит к формированию цикла синхронизации.

По специальному сигналу блока управления сигнал задающего генератора 18 через дешифратор 16 /выходов синхронизации попадает 1на выход синхронизации, адрес которого определяется содерж1И1мьш счетчика 5 выходов синхраниз.адки. Выдача сигнала синхронизации сапройождается увеличением на едивиду содержимого счетчика 6 тактов синхронизации.

Затем блок управления 12 увеличивает па единицу содержимое счетчика 5 выходов синхронизации, что обеспечивает подачу следующего сигнала задающего генератора 18 через дешифратор 16 выходов синхронизации па следующий выход синхронизации и очередное увеличение на единицу содержимого счетчика 6 тактов синхронизации. Этот процесс

повторяется до тех пор, пока третья схема сравнения 10 не выр-аботает сигнал, свидетельствующий о том, что требуемое число импульсов синхронизации выдано.

По этому сигналу блок управления 12

увеличит на единицу содерлсимое счетчика тактов 7, сбросит счетчик 6 тактов синхропизацпи, счетчик 5 выходов синхронизации и выдаст сигнал сдвига в генератор 13 случайных чисел, т. е. запустится оборудование,

формирующее сигнал па логических Bbixcv дах 19 устройства.

Вторая и третья части регистра 3 начальных условий, счетчик 5 выходов синхронизации, счетчик 6 тактов синхронизации, вторая и третья схемы сравнения 9 и 10, дешифратор 16 выходов синхронизации и задающий генератор 18 образуют ту часть оборудования, в задачу которой входит формирование цикла синхронизации объекта контроля.

Реализация этой части оборудования позволяет варьировать как числом выходов сипхронизации и числом импульсов синхронизации на каждом выходе, так и такими их параметрами, как полярность, длительность п

период (за счет специальных регулировок в

задающем генераторе 18). Сопряжение логических выходов 19 и выходов синхронизации 20 устройства с объектом контроля осуществляется через формирователь уровней 17, который предназначен для согласования по электрическим параметрам сигналов выходов устройства с объектом контроля.

Описанные выще циклы формирования логических и синхронизирующих сигналов повторяются до тех пор, иока четвертая схема сравнения И не выдаст сигнал равенства, свидетельствующий об идентичности содержимого четвертой части регистра 3 начальных условий и счетчика тактов 7, т. е. об окончании цикла формирования тестовых последовательностей. По этому сигналу блок угьравления 12 останавливает задающий генератор 18 и выдает соответствующий сигнал на выходные щины.

В устройстве предусмотрена возможность прерывания его работы по специальному сигналу на входных шинах с сохранением во всех его узлах той информации, которая находилась в них на момент прихода сигнала прерывания. Этот режим может иметь место, например, тогда, когда устройство используется как составная часть системы, предназначенной для испытаний объектов контроля по эталону. В этом случае возникновение сигнала прерывания может быть связано с расхождением реакции эталона и объекта контроля на одну и ту же тестовую последовательность, вырабатываемую устройством.

Предмет изобретения

Устройство для формирования тестов, содержащее задающий генератор, формирователь уровней, выходной регистр, счетчик тактов, блок управления и генератор случайных чисел, управляющий вход которого соединен с соответствующим выходом блока управления, информационный выход-через выходной

регистр подключен к первому входу формирователя уровней, выходы которого соединены с соответствующими выходами устройства, задающий генератор подключен к блоку управления, отличающееся тем, что, с целью

сокращения оборудования и расщирения класса формируемых тестов, в него введены дешифратор адреса, дещифратор выходов сиихронизации, регистр начальных условий, коммутатор, схемы сравнения, счетчик логических выходов, счетчик выходов синхронизации, счетчик тактов синхронизации, управляющие входы которых и управляющий вход счетчика тактов соединены с соответствующими выходами блока управления.

Выходы упомянутых счетчиков подключены к первым входам соответствующих схем сравнения, выходы которых соединены с соответствующими входами блока управления, вторые входы подключены к соответствующим

выходам регистра начальных условий, вход которого через коммутатор соединен со входом устройства, выход коммутатора подключен к информационному входу генератора случайных чисел, выход счетчнка логических

выходов через дещифратор адреса соединен с управляющим входом выходного регистра, выход счетчика выходов синхронизации через дещифратор выходов синхронизации подключен ко второму входу формирователя уровней, управляющий вход дешифратора выходов синхронизации подключен к соответствующему выходу блока управления, соединенного с соответствующими входом и выходом устройства.

20

11

е е

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

Авторы

Даты

1975-07-15—Публикация

1974-02-11—Подача