случайный тест могут оказаться различными даже если контролируемый объект полностью исправлен. Возможно, также, что изза критических состязаний в эталонном объекте его реакция совпадает с реакцией неисправного объекта. В результате исправный объект может быть неверно забракован, а неисправный объект признан годным.

Наиболее близким техническим решением является устройство для автоматического контроля цифровых объектов, содержащее генератор тестов, блок формирования входных сигналов, эталонный блок, дискриминатор выходных сигналов, блок сравнения блок блокировки, счетчик тактов, блок управления, причем первый, второй, третий и четвертый выходы блока управления соединены соответственно со входом генератора тестов, с первым входом блока формирования входных сигналов, с первым входом блока блокировки, со входом счетчика тактов, первый вь1ход генератора тестов соединен со вторым входом блока формирования входных сигналов, третий вход которого соединен с первым выходом блока блокировки, выход блока формирования входных сигналов соединен со входом эталонного блока и с выходом устройства, вход устройства соединен со входом дискриминатора выходных сигналов, выход которого соединен с первым входом блока сравнения второй и третий входы которого соединены соответственно с выходом эталонного блока, со вторым выходом блока блокировки, выход блока сравнения соединен со входом блока управления 3.

Недостатком устройства-прототипа является большие затраты оборудования. Для каждого проверяемого объекта требуется создание своей троичной модели, в которой вместо обычных двоичных элементов используются специальные элементы, работающие в троичной логике Эйхельбергера. Сложность такой модели превышает стоимость моделируемого объекта.

Другой недостаток известного устройства состоит в том, что для многих типов объектов троичное моделирование по Эйхельбергеру дает неверный результат. В конечном счете это приводит к ложной фиксации неопределенного состояния на многих выходах объекта почти на любом тесте, что по существу, исключает возможность проверки таких объектов на псевдослучайных тестах. Более точные методы обнаружения критических состязаний и риска в цифровых схемах требуют соответственно и более сложного (например восьмиричного) моделирования, которое может быть реализовано лишь программно на ЭВМ, т. е. затраты оборудования в соответствующих моделях превышают разумные пределы.

Указанный недостаток троичного моделирования приводит к тому, что известное

устройство оказывается применимым для сравнительно узкого класса объектов.

Целью изобретения является упрощение известного устройства.

Поставленная цель достигается введением блока памяти, блока ввода, блока выбора адреса, причем пятый и щестой выходы блока управления соединены соответственно с первым входом блока выбора адреса и с первым входом блока памяти, первый,

второй, и третий выходы которого соединены соответственно со вторым входом блока выбора адреса, со вторым входом генератора тестов, со вторым входом блока блокировки, выход блока ввода соединен со вторым

входом блока памяти, выход счетчика, тактов соединен с третьим входом блока выбора адреса, выход которого соединен с третьим входом блока памяти.

Информация, которая вводится в указанный блок памяти, получается на основе программного моделирования объекта с помощью ЭВМ на выбранном псевдослучайном тесте. При этом может использоваться любой наиболее подходящий для данного объекта метод моделирования, обеспечивающий

обнаружение критических состязаний при реально возможных в объекте сочетаниях задержки элементов.

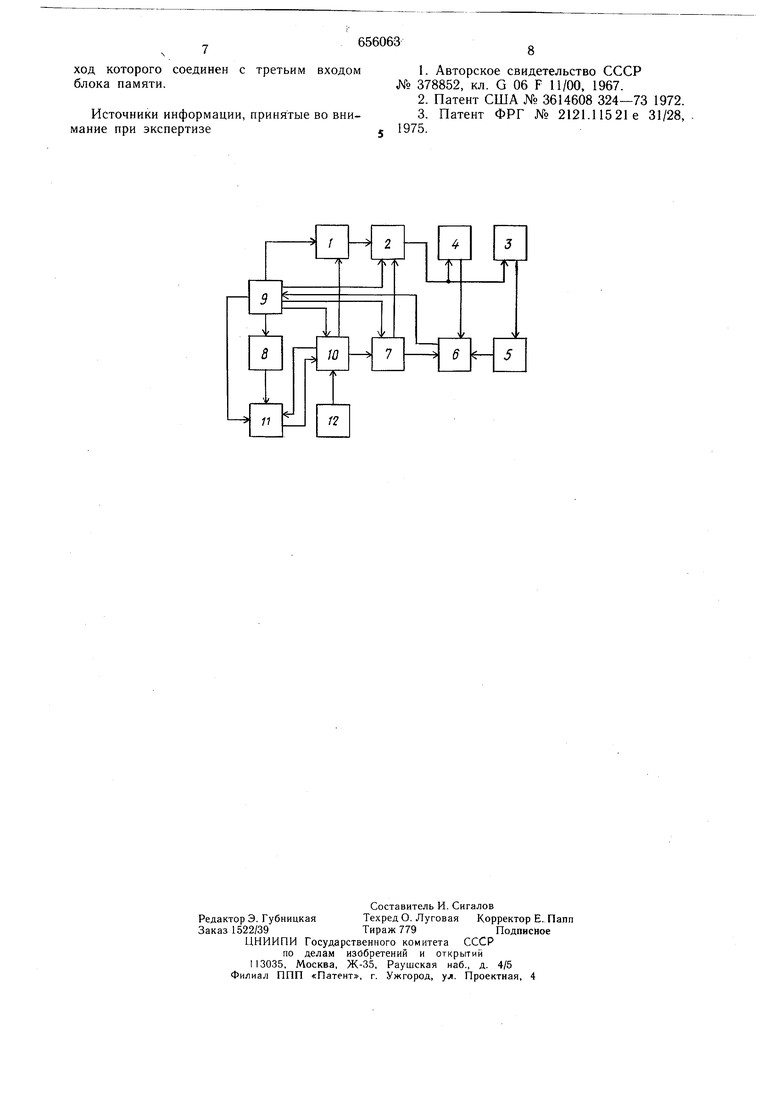

На чертеже приведена блок-схема предлагаемого устройства.

Устройство контроля цифровых объектов

содержит генератор тестов 1, соединенный с ним блок формирования входных сигналов 2, имеющий выходы для подключения ко входам контролируемого 3 и эталонного 4 блока и предназначенный для запоминания

логических значений сигналов, прикладываемых ко входам объектов и формирования соответствующих этим сигналам потенциалов, дискриминатор выходных сигналов 5, обеспечивающий контроль выходных потенциалов контролируемого объекта на соответствие потенциалам логических значений «1 и «О, соединенный с выходами дискриминатора 5 и эталонного блока 4, блок сравнения 6, который служит для обнаружения логического неравенства выходных сигналов контролируемого и эталонного блоков, блок блокировки 7, запрещающий блоку срав нения 6 учитывать при сравнении выходы, состояние которых является неопределенным счетчик тактов 8, фиксирующий номер текущего такта проверки, блок управления 9,

блок памяти 10, обеспечивающий хранение информации о состоянии выводов в соответствующих тактах проверки и соединенный с блоком выбора адреса 11, который обеспечивает прием, хранение и выдачу информации

в блок управления 9 о норме следующего такта, в котором разрещено (или нет) сравнение выходных реакций на соответствующих выводах, блок ввода 12, соединенный с блоком памяти 10. Устройство работает следующим образом. С помощью блока ввода 12 в блок памяти 10 записывается информация, определяющая, в какие такты и на каких контактах необходимо (или нет) обеспечить сравнение выходных реакций. Выходы контролируемого 3 и эталонного 4 блоков подключаются параллельно ко входам формирователя входных сигналов 2. Выходы контролируемого объекта (в том числе и все доступные его выходы интегральных схем) соединяются со входом дискриминатора выходных сигналов 5, а выходы эталонного блока (в том числе и доступные выходы его интегральных схем) - со входами блока сравнения. После ручного запуска блок управления 9 приводит в исходное состояние все блоки устройства. Включается генератор тестов 1. Псевдослучайная последовательность сигналов, вырабатываемая этим генератором поступает на формирователь входных сигналов 2, который образует и подает на входы контролируемого 3 и эталонного 4 блоков последовательность наборов потенциальных сигналов. После установки на входах объектов набора потенциалов, соответствующего текущему такту теста, блок управления 9 увеличивает на единицу содержимое счетчика тактов 8 (при условии, что в первом такте сравнение реакций осуществляется на всех входах). Сигналы на выходах контролируемого объекта анализируются дискриминатором выходных сигналов 5, который определяет логическое значение сигнала на каждом выходе, а также фиксирует все случаи отклонения выходных потенциалов объекта за пределы допусков для «1 и «О. Выходные сигналы дискриминаторов выходных сигналов 5 сравниваются блоком сравнения 6 с выходными сигналами эталонного блока. После окончания первого такта проверки блок управления 9 обеспечивает прием из блока памяти 10 в блок выбора адреса 11 информации о номере следующего такта, а также о номерах выводов объектов в этих тактах, на которых запрещено сравнение реакций. Кроме того, в блоке выбора адреса 11 по сигналам счетчика тактов 8 блока управления 9, а также в соответствии с информацией, хранимой в блоке памяти 10, вырабатываются сигналы, поступающие в блок сравнения 6. По этим сигналам те выводы объектов, на которых возможно появление состояния неопределенности в результате состязаний в процессе проверки, игнорируются и не сравниваются. При обнаружении неравенства на не запрещенных выводах блок сравнения 6 выдает соответствующий сигнал в блок управления, который выключает генератор и сигнализирует (с помощью элементов индикации) о неисправности контролируемого объекта. Введение в предлагаемое устройство вместо преобразователей двоичных сигналов в троичные и наоборот, а также вместо троичной модели проверяемого объекта блока памяти, блока выбора адреса и блока ввода с новыми связями позволяет уменьщить объем оборудования, упростить устройство, снизить затраты на проверку и обеспечивает контроль асинхронных логических схем, в том числе тех, для которых оказывается не эффективным троичное моделирование. По сравнению с программно управляемыми устройствами контроля предложенное устройство требует меньщий объем памяти за счет отсутствия программно задаваемых тестов и эталонных реакций. Формула изобретения Устройство для автоматического контроля цифровых объектов, содержащее генератор тестов, блок формирования входных сигналов, эталонный блок, дискриминатор выходных сигналов, блок сравнения, блок блокировки, счетчик тактов, блок управления, причем первый, второй, третий и четвертый выходы блока управления соединены соответственно со входом генератора тестов, с первым входом блока формирования входных сигналов, с первым входом блока блокировки, со входом счетчика тактов, первый выход генератора тестов соединен со вторым входом блока формирования входных сигналов, третий вход которого соединен с первым выходом блока блокировки, выход блока формирования входных сигналов соединен со входом эталонного блока и с выходом устройства, вход устройства соединен со входом дискриминатора выходных сигналов, выход которого соединен с первым входом блока сравнения, второй и третий входы которого соединены соответственно с выходом эталонного блока, со вторым выходом блока блокировки, выход блока сравнения соединен со входом блока управления, отличающееся тем, что, с целью упрощения устройства, оно содержит блок памяти, блок ввода, блок выбора адреса, причем пятый и щестой выходы блока управления соединены соответственно с первым входом блока выбора адреса и с первым входом блока памяти, первый, второй и третий выходы которого соединены соответственно со вторым входом блока выбора адреса, со вторым входом генератора тестов, со вторым входом блока блокировки, выход блока ввода соединен со вторым входом блока памяти, выход счетчика тактов соединен с третьим входом блока выбора адреса, выход которого соединен с третьим входом блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 378852, кл. G 06 F 11/00. 1967.

2.Патент США № 3614608 324-73 1972.

3.Патент ФРГ № 2121.115 21 е 31/28,

1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля цифровых объектов | 1980 |

|

SU888123A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля объектов дискретного действия | 1987 |

|

SU1439602A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для автоматическогоКОНТРОля бОльшиХ иНТЕгРАльНыХ CXEM | 1978 |

|

SU798841A1 |

| Устройство для контроля цифровых модулей и проверки качества тестов | 1974 |

|

SU519713A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

Авторы

Даты

1979-04-05—Публикация

1977-02-09—Подача