(54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Цифровое устройство управления трехфазным мостовым инвертором | 1985 |

|

SU1312740A1 |

| Преобразователь частота-код | 1983 |

|

SU1129543A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности может быть использовано в цифровых синтезаторах частоты.

Известен делитель частоты с перейенным коэффициентом деления, содержащий счетчик младшего разряда, счетчик старших разрядов, шину кода управления младшим разрядом, шину кода управления старшими разрядами и двухпозиционный счетчик с двумя возможными коэффициентами пересчета 1,.

Однако недостатком делителя частоты является то, что для повышения быстродействия требуется существенно ограничивать набор реализуемых коэффициентов деления.

Кроме того, необходимы дополнительные затраты на формирование специфических кодов управления, а также присуща девиация фазы выходного сигнала, определяемая дрейфом задержки счетчика старшитс разрядов и весьма нежелательная при построении си-нтезаторов частоты.

Целью изобретения является расширение функциональных возможностей при одновременном уменьшении девиации фазы выходного сигнала при сохранении быстродействия.

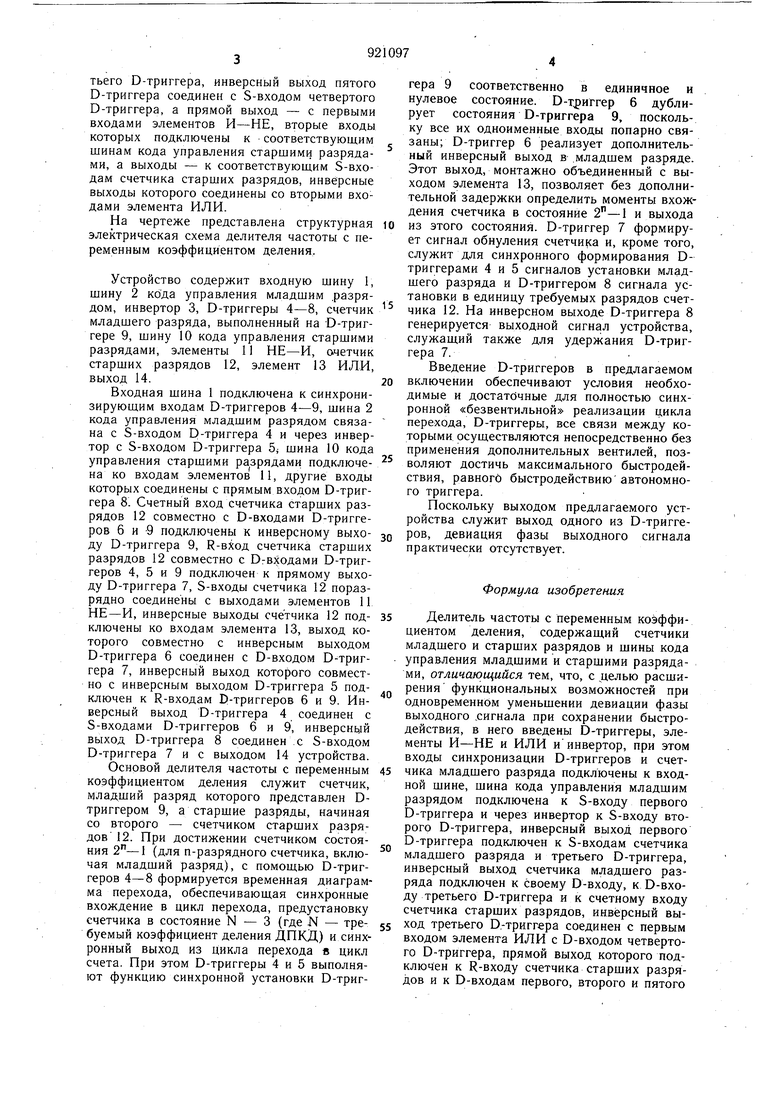

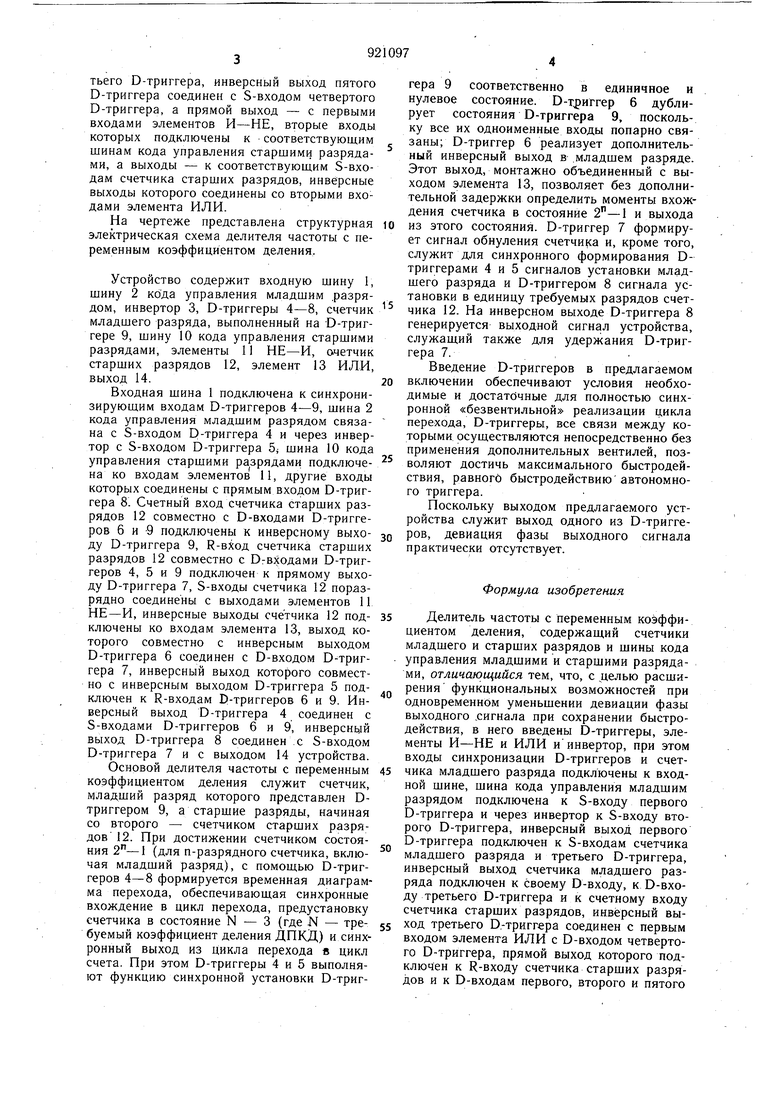

Поставленная цель достигается тем, что в делитель частоты с переменным коэффициентом деления, содержащий счетчики младшего и старшего разрядов и шины кода управления младшим и старшими разрядами, введены D-триггеры, элементы И-НЕ и ИЛИ и инвертор, при этом входы синхронизации D-триггеров и счетчика младшего разряда подключены к входной шине, шина кода управления младшим разрядом подключена К S-входу первого D-триггера и че10рез инвертор к S-входу второго D-триггера, инверсный выход первого D-триггера подключен KS-входам счетчика младшего разряда и третьего D-триггера, инверсньш выход счетчика младшего разря.да подключен к своему D-входу, к D-входу третьего D-триг15гера и к счетному входу счетчика старших разрядов, инверсный выход третьего D-триггера соединен с первым входом элемента ИЛИ и с D-входом четвертого D-триггера, прямой выход которого подключен к R-BXO20ду счетчика старших разрядов и к D-входам первого, второго и пятого D-триггеров, а инверсный выход объединен с инверсным выходом второго D-триггера и подключен к R-BxtaaM счетчика младшего разряда и третьего D-триггера, инверсный выход пятого D-триггера соединен с S-входом четвертого D-триггера, а прямой выход - с первыми входами элементов И-НЕ, вторые входы которых подключены к соответствующим шинам кода управления старшими разрядами, а выходы - к соответствующим S-входам счетчика старших разрядов, инверсные выходы которого соединены со вторыми входами элемента ИЛИ. На чертеже представлена структурная электрическая схема делителя частоты с переменным коэффициентом деления. Устройство содержит входную шину 1, шину 2 кода управления младшим .разрядом, инвертор 3, D-триггеры 4-8, счетчик младшего разряда, выполненный на D-триггере 9, шину 10 кода управления старшими разрядами, элементы 11 НЕ-И, очетчик старших разрядов 12, элемент 13 ИЛИ, выход 14. Входная шина 1 подключена к синхронизирующим входам D-триггеров 4-9, шина 2 кода управления младшим разрядом связана с S-входом Р-триггера 4 и через инвертор с S-входом D-триггера 5( шина 10 кода управления старшими разрядами подключена ко входам элементов 11, другие входы которых соединены с прямым входом D-триггера 8. Счетный вход счетчика старших разрядов 12 совместно с D-входами D-триггеров б и -9 подключены к инверсному выходу D-триггера 9, R-вХод счетчика старших разрядов 12 совместно с Ргвходами D-триггеров 4, 5 и 9 подключен к прямому выходу D-триггера 7, S-входы счетчика 12 поразрядно соединены с выходами элементов 11 НЕ-И, инверсные выходы счетчика 12 подключены ко входам элемента 13, выход которого совместно с инверсным выходом D-триггера 6 соединен с D-входом D-триггера 7, инверсный выход которого совместно с инверсным выходом D-триггера 5 подключен к R-входам D-триггеров 6 и 9. Инверсный выход D-триггера 4 соединен с S-входами D-триггеров б и 9, инверсный выход D-триггера 8 соединен с S-входом D-триггера 7 и с выходом 14 устройства. Основой делителя частоты с переменным коэффициентом деления служит счетчик, младший разряд которого представлен Dтриггером 9, а старшие разряды, начиная со второго - счетчиком старших разрядов 12. При достижении счетчиком состояния (для п-разрядного счетчика, включая младший разряд), с помощью D-триггеров 4-8 формируется временная диаграмма перехода, обеспечивающая синхронные вхождение в цикл перехода, предустановку счетчика в состояние N - 3 (где N - требуемый коэффициент деления ДПКД) и синхронный выход из цикла перехода в цикл счета. При этом D-триггеры 4 и 5 выполняют функцию синхронной установки D-триггера 9 соответственно в единичное и нулевое состояние. D-триггер 6 дублирует состояния D-триггера 9, поскольку все их одноименные входы попарно связаны; D-триггер 6 реализует дополнительный инверсный выход в .младшем разряде. Этот выход, монтажно объединенный с выходом элемента 13, позволяет без дополнительной задержки определить моменты вхождения счетчика в состояние и выхода из этого состояния. D-триггер 7 формирует сигнал обнуления счетчи са и, кроме того, служит для синхронного формирования Dтриггерами 4 и 5 сигналов установки младшего разряда и D-триггером 8 сигнала установки в единицу требуемых разрядов счетчика 12. На инверсном выходе D-триггера 8 генерируется выходной сигнал устройства, служащий также для удержания D-триггера 7., Введение D-триггеров в предлагаемом включении обеспечивают условия необходимые и достаточные для полностью синхронной «безвентильной реализации цикла перехода, D-триггеры, все связи между которыми осуществляются непосредственно без применения дополнительных вентилей, позволяют достичь максимального быстродействия, равного быстродействию автономного триггера. Поскольку выходом предлагаемого устройства служит выход одного из D-триггеров, девиация фазы выходного сигнала практически отсутствует. Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий счетчики младшего и старших разрядов и шины кода управления младшими и старшими разрядами, отличающийся тем, что, с делью расширения функциональных возможностей при одновременном уменьщении девиации фазы выходного .сигнала при сохранении быстродействия, в него введены D-триггеры, элементы И-НЕ и ИЛИ и инвертор, при этом входы синхронизации D-триггеров и счетчика младшего разряда подключены к входной шине, шина кода управления младшим разрядом подключена к З-входу первого D-триггера и через инвертор к S-входу второго D-триггера, инверсный выход первого D-триггера подключен к S-входам счетчика младшего разряда и третьего D-триггера, инверсный выход счетчика младшего разряда подключен к своему D-входу, к D-BXOду третьего D-триггера и к счетному входу счетчика старших разрядов, инверсный выход третьего D,-тpиггepa соединен с первым входом элемента ИЛИ с D-входом четвертого D-триггера, прямой выход которого подключен к R-входу счетчика старших разрядов и к D-входам первого, второго и пятого D-триггеров, а инверсный выход объединен с инверсным выходом второго D-триггера и подключен к R-входам счетчика младшего разряда и третьего D-триггера, инверсный выход пятого D-триггера соединен с S-BXOдом четвертого Ь-триггера, а прямой выход - с первыми входами элементов И-НЕ, вторые входы которых подключены к соответствующим шинам кода управления старшими разрядами, а выходы - к соответствующим S-входам счетчика старщих разрядов, инверсные выходы которого соединены с вторыми входами элемента ИЛИ. Источники информации, принятые во внимание прл экспертизе 1. Манасеевич В. Синтезаторы частот (Теория и проектирование). М., «Связь, 1979, с. 262-263, рис. 6.27 (прототип).

Авторы

Даты

1982-04-15—Публикация

1980-07-02—Подача