(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1980 |

|

SU922722A2 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство для ввода информации | 1987 |

|

SU1539761A1 |

| Устройство для регистрации информации | 1983 |

|

SU1115074A1 |

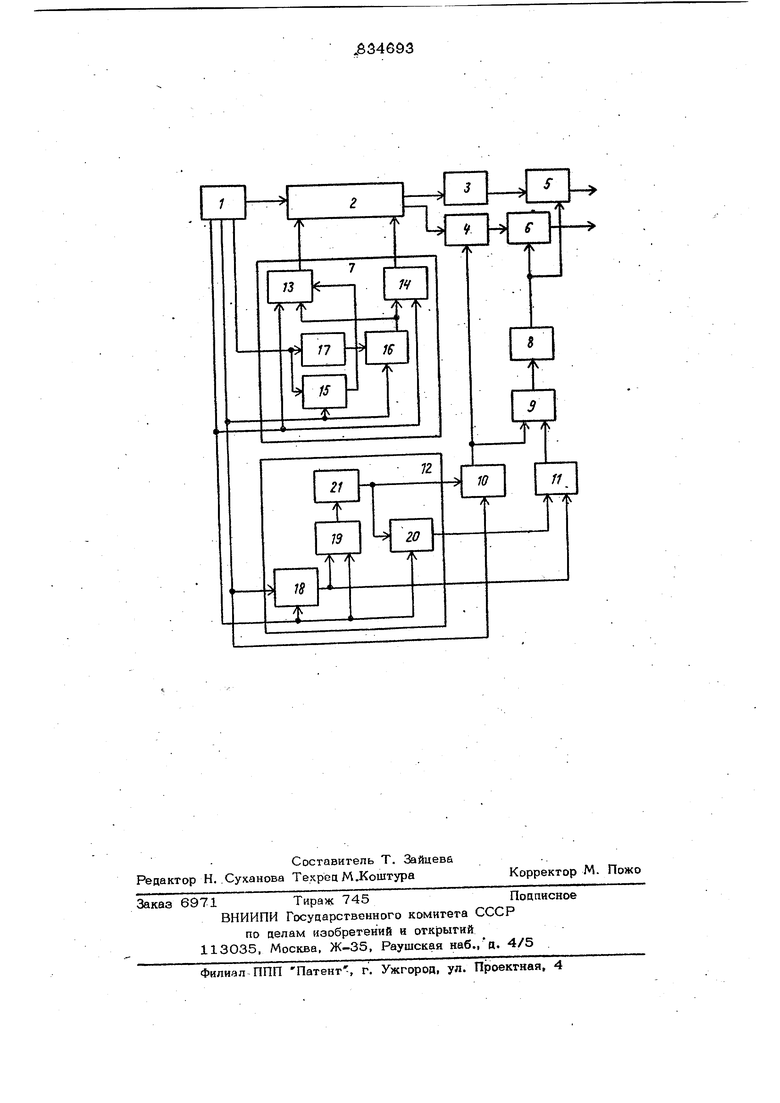

Изобретение относится к области вычислительной техники. Известен преобразователь конов, содер жащий накопители на магнитных цисках и лентах, причем запись информации осуществляется при помощи программных инструкций llНедостатком такого преобразователя является его низкое быстроаействие. Наиболее близким техническим решением к изобретению является преобразователь кодов, который содержит датчик информации, выход которого подключен к входу кодирующего блока, и буферный запоминающий блок, связанный как с кодирующим блоком, так и с выходными усилителями, причем запись информации в буферный запоминающий блок осуществляется последовательно с нулевого адреса и по заполнению буферного запоминающег блока или в случае реакции на выставленный запрос происходит считывание в ма - гистраль накопленной информации, причем считанный массив соответствует объему буферного запоминающего блока 12 . Недостатком этого преобразователя является низкое быстродействие вследствие необходимости считывать и перезаписывать весь объем информации, накопленной в буферном запоминающем блоке, а также сложность преобразователя. Целью изобретения является повышение бьютродействия и упрощение преобразователя кодов. Это достигается тем, что в преобразователь кодов,-фрержащий датчик кодов, коммутатор, регистр числа, регистр адреса и усилители, причем первый вход коммутатора соединён с первым выходом датчика кодов, а первый и второй выходы подключены соответственно к первым входам регистра числа и регистра адреса, выходы которых соединены соответственно с первыми входами усилителей, выходы которых являются выходами преобразователя кодов, введены блок ан-лпизя приэиа- ков, распределитель сигналов, элемент ИЛИ, первый и второй элементы И и пер вый элемент зааержки, причем первый вхоц блока анализа признаков соединен с вторым выходом датчика кодов, второй вкод - с первыми входами распределитепя сигна/юв и первого элемента И и третьим выходом датчика кодов, а третий вход - с вторым входом распределителя сигналов и четвертьп выходом датчика кодов, первый и второй выходы блока анализа признаков подключены соответственно к вто рому и третьему входам коммутатора, первый выход распределителя сигналов сое динен с вторым входом первого элемента И, а второй и третий выходы распредепителя сигналов соединены соответственно с первым и вторым входами второго элемента И, выход первого элемента И подключен к второму входу регистра адреса и первому входу элемента ИЛИ, а выход второго элемента И - к второму входу элемента ИЛИ, выход которого соединен С входом первого элемента задержки, выход которого подключен к вторым входам усилителей. При этом блок анализа признаков целесообразно выполнить содержащим первый и второй триггеры, третий и четвёртый элементы И и элемент НЕ, выход которого соединен с первым входом четверо тога элемента И, выход третьего элемента И подключен к первому входу первого триггера, а выход четвертого элемента ИSвторому входу первого триггера и первому входу второго триггера, вход элемента НЕ и первый вход третьего элемента И соединены Ъ явлгяются нервьтм входом блока анализа признаков, вторые входы третьего и четвертого элементов И соединены и являются вторым входом блока анализа признаков, третий вход первого триггера и второй вход второго триггера объединены и являются третьим входом блока анализа при знаков, выходы первого к лорого триггеров явл5потся соответстветсно. первым н вторым выходами блока анализа признаков, а распределитель сигналов целесообразно выполнить содержащим счетчик, третий и четвертый триггеры и второй элемент задержки, причем первый и второй входы счетчика являются соответственно первым и вторым входами распределителя сигналов, второй вход счетчика соединен с первыми входами третьего и четвертог триггеров, а выход счетчика подключен к второму входу третьего триггерй, выход которого соединен с входом второго элемента задержки, выход которого подключен к второму входу четвертого триггера, выходы счетчика, четвертого триггера в второго элемента задержки являются соответственно третьим, вторым и первым выходами распределителя сигналов. На чертеже изображена функциональная схема предложенного преобразователя кодов. Преобразователь кодов содержит датчик кодов 1, коммутатор 2, регистр числа 3, регистр адреса 4, первый 5 и второй 6 усилители, блок анализа признаков 7, первый элемент задерноси 8, элемент ИЛИ 9, первый 10 и второй 11 элементы И и распределитель сигналов 12. Первый вход -коммутатора 2 соединен с первым выходом датчика кодов 1, а первый и второй выходы подключены соот- ветственно к первым входам регистра числа 3 и регистра адреса 4, выходы которых соединены соответетвенно с первыми входами первого 5 и второго 6 усилителей, выходы которых являются выходами преобразователя кодов. Первый вход блока анализа признаков 7 соединен с вторым выходом датчика кодов 1, второй вход - с первыми входами распределителя сигналов 12 и первого элемента И Ю и третьим выходом датчика кодов 1, а третий вход - с вторым входом распределителя сигналов 12 и четвертым выходом датчика кодов 1. Первый и второй выходы блока анализа признаков 7 подключены соответственно к второму и третьему входам коммутатора 2. Первый выход распределителя сигналов 12 соединен с вторым входом первого элемента И 1О. Второй и третий выходы распределителя сигналов 12 соединены соответственно с первым и вторым входами второго элемента И 11. Выход первого элемента И 1О подкл1б чен к второму входу регистра адреса 4 и первому входу элемента ИЛИ 9. Выход второго элемента И 11 подключен к второму входу-элемента ИЛИ 9, выход которого, соединен с входом первого элемента зацераоси 8, выход которого подключен к вторым входам первого 5 и второго 6 усилителей. Блок анализа признаков 7 выполнен содержащим первый 13 и второй 14 триггеры, третий 15 и четвертый 16 элементы И и элемент НЕ 17, выход которого соединен с первым входом четвертого элемента И 16. Выход третьего элемента И 15 подключен к первому входу первого триггера 13, а выход четвертого элемен- та И 16 - к второму входу первого триг гера 13 и первому вхоцу второго триггера 14. Вкод элемента НЕ 17 и первы вход третьего элемента И 15 соединены и являются первым входом блока анализа признаков 7.Вторые входы третьего 15 и четвертого 16 элементов И соединены и являются вторым входом блока ана лиза признаков 7. Третий вход первого триггера 13 и второй вход второго триггера 14 объединены и являются третьим входом блока анализа признаков 7- Выхо ды первого 13 и второго 14 триггеров являются соответственно первым и вторым выходами блока анализа признаков 7. Распределитель сигналов 12 выполнен содержащим счетчик 18, третий 19 и чет вертый 20 триггеры и второй элемент за держки 21. Первый и второй входы счетчика 18 являются соответственно первым и вторым входами распределителя сигналов 12. Второй вход счетчика 18 соединен с первыми входами третьего 19 и четвертого 20 триггеров. Выход счетчика 18 подключен к второму входу третьего триггера 19, выход которого соединен с входом второго элемента задержки 21,вы ход которого подключен к второму входу четвертого триггера 20. Выходы счетчика 18, четвертого триггера 20 и второго элемента задержки 21 являются соответственно третьим, вторым и первым выходами распределителя сигналов 12. Преобразователь кодов работает следующим образом. Информация, представленная в двоичном коде, с выхода датчика кодов 1 поступает на первый вход коммутатора 2, который по сигналам из блока анализа признаков 7 производит ее распределение на адресную и числовую. Каждое информационное слово, приходящее на первый вход коммутатора 2, сопровождается синхроимпульсом, формируемым в цатчике кодов 1 и снимаемым с третьего его выхода. При этом перед первым и после последнего передаваемого слова датчиком кодов 1 вы рабатываются соответствующие сигналы Начало и Конец. Эти сигналы снимаются с второго и четвертого выходов дат чика кодов 1. . В исходном состоянии перед началом поступления очередной части массива информации, вырабатываемой датчиком кодов 1,с выходов блока анализа признаков 7 и первого и второго выходов распределителя сигналов 12 поступают в коммутатор 2 и на элементы И 10 и 11 потенциалы, запрещающие прохождение информации черва коммутатор 2 и синхроимпульсов черва первый 10 и второй 11 эпеменгы И, а о третьего выхода распределителя сирналов 12поступает разрешающий потенциал. При появлении на втором выходе датчика 1 сигнала Начало на первом входе блока анализа признаков 7 формируется разрешающий потенциал, на втором входе запрещающий. В результате при наличии iftepBoro синхроимпульса первый триггер 13изменяет свое состояние, и на второй вход коммутатора 2 поступает разрешение на прохождение слова от датчика кодов 1 на регистр адреса 4. Перед выдачей второго слова от датчика кодов 1 сигнал Начало на первом входе блока анализа признаков 7 снимается, соответственно этому второй синхро-. импульс пройдет через четвертый элемент И 16. В результате первый 13 и второй 14триггеры изменят свое состояние, и на , втором входе коммутатЪра 2 будет выработан запрет, а на третьем входе - разрешение. При-этом передача слова от датчика кодов 1 произойдет на регистр числа 3. Одновременно от второго синхроимпульса на выходе счетчика- 18 формируется импульс, который благодаря наличию разрешающего потенциала на третьем выходе распределителя сигналов 12 пройдет через второй элемент И 11 схемы, элемент ИЛИ 9 и первый элемент задержки 8 на вторые входы усилителей 5 и 6. В результате числовая и адресная информация с регистров 3 и 4 через усилители 5 и 6 поступит на выход устройства. Импульс, сформированный на выходе .счетчика 18, изменит также состояние третьего триггера 19, в результате через некоторый интервал времени, определяемый вторым лэментом задержки 21, до прихода очередного синхроимпульса изменит свое состояние четвертый триггер 2О, и на входах первого 10 и второго 11 элементов И сформируются соответственно потенциалы разрешения и запрета прохождекшо импупь- сов. При поступлении третьего и последуюих слов и сопровождающих их синхромпульсов состояние блока анализа признаов 7 и распределителя сигналов 12 не еняется. В результате произойдет переача третьего и последующих слов от датика кодов 1 на регистр числа 3. Одноременно каждый сопровождающий слово инхроимпульс с третьего выхода датчика 783 кодов 1 через первый влемен И 10 пройдег на второй вход регисгра адреса 4 что вызовет увеличение ацреса на единицу, и через элемент ИЛИ 9 и первый эле мент задержки 8 на вторые входы усилителей 5 а 6. В результате происходит передача адреса и числа с регистров адреса 4 и числа 3 на выход устройства. После поступления последнего слова массива информации на четвертом выходе датчика койов 1 вырабатьгеается сигнал Конец приводящий устройство в исходное состояние. Технйко-экономическое преимущество описываемаго преобразователя кодов заключается в том, что он п)1 аволяет исключить программное формирование адресной информации и аппаратурными средствами ускорить формирование адресно-числовбй информации, аа счет чего повысить быстродействие и упростить преобразователь кодов. ормула изобретения 1. Преобразователь кодов, содержащий датчик кодов, коммутатор, регистр числа, регистр адреса и усилители, причем первый вкоц коммутатора соединен с первым выхоцом датчика .кодов, а первый и второй выходы подключены соответственно к первым вхоаам регистра числа и регист ра адреса, выходы которых соединены со- ответсгвенно с аервыми входами усилителей, вых.оаы которых являются выходами преобразователя кодов, отличающийся тем, что, с целью повышения быстродействия и упрощения преобразователя KoaoBt он содержит блок анализа при знаков, распределитель сигналов, элемент ИЛИ, первый к втЪрой элементы И и первый элемент задержки, причем первый вход блока анализа признаков соединен с вторым выходом датчика кодов, второй вход с первыми входами распределителя сигналов и первого элемента И и третьим выходом датчика кодов, а третий вход с вторым .входом распределителя сигналов и четвертым выходом датчика кодов, первый и второй выходы блока анализа признаков подключены соответственно к второму т третьему входам коммута тора, первый выход распределителя сигналов соединен с вторым входом первого элемента И, а второй и третай выходы распределителя сигналов соединены соот8ветственно с первым и вторым входами второго элемента И, выкод первого 8лемента и подключен к второму входу регистра адреса и первому входу элемента ИЛИ, а выход второго элемента И - Е вто рому входу элемента ИЛИ,выкоД KtwoporoT соединен с входом первого элемента задержки, выход которого подключен к вторым входам усилителей. 2.Преобразователь кодов по п. 1, о т л и ч а ю щ и и с я тем, что блок анализа признаков содержит первый и второй триггеры, третий и четвертый элементы И и элемент НЕ, выход которого соединен с первым входом, четвертого элемента И, выход третьего элемента И подключен к первому входу первого триггера, а выход четвертого элемента И-- к второму входу первого триггера и первому входу второго триггера, вход эл„емента НЕ и первый вход третьего элемента И соединены и являются первым входом блока анализа признаков, вторые входы третьего и четвертого элементов И соединены и являют- ся вторым входом блока анализа признаков, третий вход первого триггера и второй вход второго триггера объединены и являются третьим входом блока анализа признаков, выходы первого и второго триг- геров являются соответстЕгенно первым и вторым выходами блока анализа признаков, 3.Преобразователь кодов по пп, 1 и 2, отличающийся тем; что распределитель сигналов содержит счетчик, третий и четвертый триггеры и второй элемент задержки, причем первый и второй входы счетчика являются соответственно первым и вторым входами распределителя сигналов, второй вход счетчика соединен с первыми входами третьего и четвертого триггеров, а выход счетчика подключен к второму входу третьего триггера, выход которого соединен с входом второго элемента задержки, выход которого подключен к второму входу четвертого, триггера, выходы счетчика, четвертого триггера и второго элемента задержки являются соответственно третьим, вторым и первым выходами распределителя сигналов. Источники информации, принятые во внимание при экспертизе 1.Флорес. Внешние устройства ЭВМ. М., Мир, 1976, с. 153. 2.Авторское свидетельство СССР № 542240, кл. Q Об F 3/00, 1975 (прототип).

Авторы

Даты

1981-05-30—Публикация

1979-07-11—Подача