ваемого базового адреса устройства соединен с информационным входом регистра присвоенного базового адреса, выход которого соединен с вторым входом четвертого элемента И, выходы третьего и четвертого

1161944

элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ , выход кото рого соединен с входами старших разрядов счетчика адре сов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1987 |

|

SU1465887A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1985 |

|

SU1282140A1 |

| Преобразователь кодов | 1979 |

|

SU834693A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Преобразователь кодов | 1980 |

|

SU922722A2 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для управления памятью | 1979 |

|

SU943726A1 |

| Устройство для межмашинного обмена | 1985 |

|

SU1298756A1 |

УСТРОЙСТВО ДЛЯ.МОДИФИКАЦИИ АДРЕСА ЗОН ПАМЯТИ ПРИ ОТЛАДКЕ ПРОГРАММ, срдержащее коммутатор, регистр числа, счетчик адреса, первый и второй блоки элементов И, блок анализа признаков, распределитель импульсов, первьй и второй элементы И, элемент задержки и первый элемент ИЛИ, причем информационный вход и вход начальной установки устройства соединены соответственно с информационHbiM входом коммутатора и установочным входом блока анализа признаков, первый и второй выходы KdTOporo соединены с управляющими входами коммута-. тора, тактовый вход устройства соединен с тактовым входом блока анализа признаков, с тактовым входом распределителя импульсов и первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ и входом Плюс единица счетчика адреса, вход признака.коица массива записываемой информации устройства соединен с входом начальной установки блока анализа признаков и входом останова распределителя импульсов, первьй, второй и третий выходы которого соединены соответственно с вторым входом первого элемента И, с первым и вторым входами второго элемента И, выход второго элемента И соединен с вторым входом первого элемента -ШШ, выход которого через элемент задержки соединен с первыми входами первого и второго блоков элементов И, первый Ивторой выходы коммутатора сгединены соответственно с информационным входом регистра числа и входом младших разрядов счетчика адреса, выходы регистра числа и счетчика адреса соединены соответственно с вторыми входами первого (Л и второго блоков элементов И, выходы которых являются соответственно числовым и адресным выходами устройства, о тличающееся тем что, с целью уменьшения объема блока отладочной памяти, в устройство введены регистр исходного базоОд вого адреса, регистр фиксированного базового адреса, регистр присвоенно$ го базового адреса, схема сравнения, третий и четвертый элементы И и вто4 4 рой элемент ИЛИ, причем третий выход коммутатора соединен с входом регистра исходного базового адреса, выход которого соединен с первым входом схемы сравнения и первым входом третьего элемента И, вьрсод регистра фиксированного базового адреса соединен с вторым входом схемы сравнения, выходы равенства и неравенства которой соединены соответственно с первым входом четвертого элемента И и вторым входом третьего элемента И, вход установки присваи

1

Изобретение относится к вычислительной технике и может быть использовано для формирования адресночисловой информации, фиксируемой в блоке памяти.

Известно устройство, вьфабатывающее информацию, которая в дальнейшем записывается в отладочные блоки памяти, причем запись информации осуществляется с помощью программных инструкций СО.

Недостатком таких устройств является низкое быстродействие, обусловленное большим временем реализации программы с помощью ЭВМ.

Известно устройство , которое содерзкит датчик информации, кодирующий блок.и буферный запоминающий блок, причем запись информации в буферный запоминающий блок осуществляется последовательно с нулевого адреса 2 J

Недостатками этого устройства являются низкое быстродействие вследствие необходимости считывать и перезаписывать весь объем информации, накопленный в буферном блоке памяти, а также значительная сложность устройства, связанная с наличием в его составе буферного блока памяти.

Наиболее близким к предлагаемому по технической сущности является .преобразователь кодов, когорьш содержит коммутатор, регистр числа, регистр адреса, усилители, блок анализа признаков, распределитель сигналов, элементы И, ИЛИ, элементы задержки. Он обеспечивает формирование адресной информации аппаратными средствами, врезультате чего ускоряется формирование адресно-числовых данных для блока памяти. Следствием этого является повьшение быстродействия и упрощение преобразователя кодов Сз.

В некоторых случаях, например при отладке программ задач специализированных ЦВМ, возникает необходимость переадресации массивов передаваемой информации, т.е. записи информации в отладочные блоки памяти не в соответствии с исходным базовым адресом, подготовленным на входе коммутатора, а в другую, например

0 свободную,зону, т.е. в соответствии с базовым адресом, назначенным оператором. При этом исходная адресная информация, подготовленная на входе коммутатора должна оставаться неизменной.Переадресация массива информации при записи в произвольные зоны отладочной памяти расширяет функциональные возможности устройства и позволяет сократить информационную емкость отладочной памяти.

Известное устройство не обеспечивает реализацию такого режима переадресации, что в ряде случаев при отладке программ задач ограничивает его функциональные возможности.

Цель изобретения - уменьшение объема блока отладочной памяти.

Поставленная цель достигается тем,

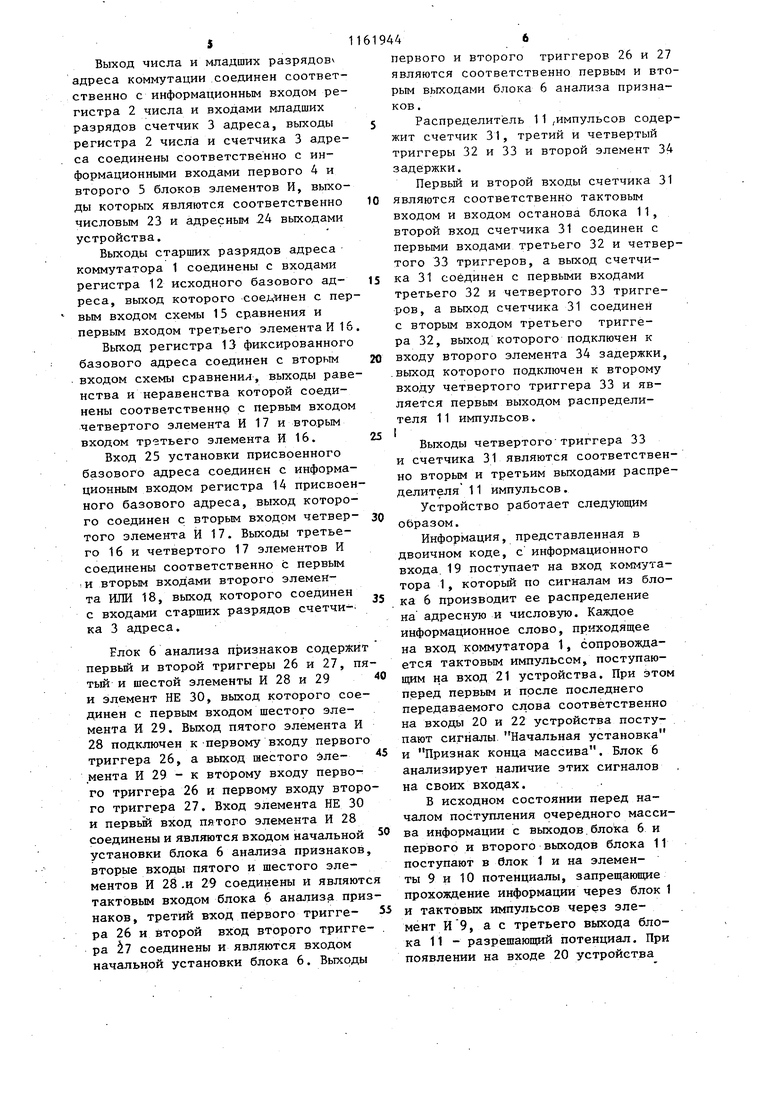

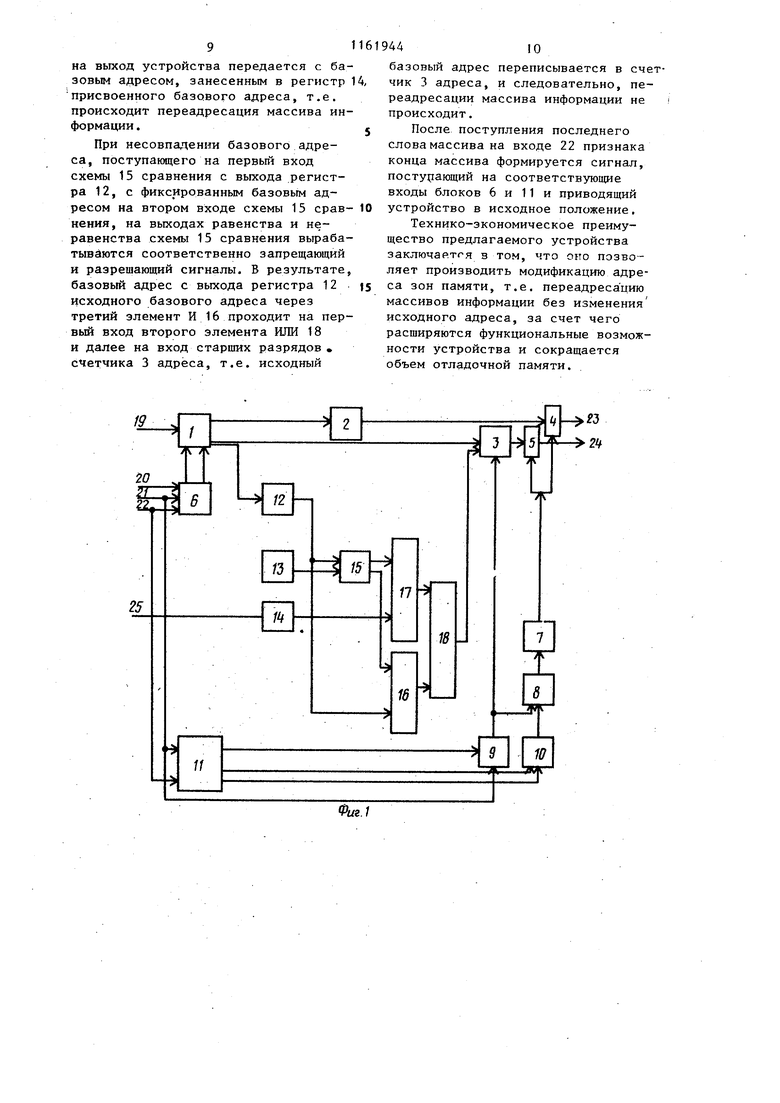

Q что в устройство для модификации адреса зон памяти при отладке программ, содержащее коммутатор, регистр числа, счетчик адреса, первый и второй блоки элементов И, блок анализа признаков, распределитель импульсов, первьй и второй элементы И, элемент задержки и первьй элемент ИЛИ, причем информа. ционный вход и вход начальной усц тановки устройства соединены соответственно с информационным входом коммутатора и установочным входом блока анализа признаков, первый и второй выходы которого соединены с управляющими входами коммутатора, тактовый вход устройства соединен с тактовым входом блока анализа признаков, с тактовьгм входом распределителя импульсо.в и первым входом первого элемента И, вьгход которого соединен с первым входом первого элемента ИЛИ и входом Плюс единица счетчика адреса, вход признака конца массива записываемой информации устройства соединен с входом начальной установки блока анализа признаков и входом останова распределителя импульсов, первый, второй и третий выходы которого соединены соответственно с вторым входом первого элемента И, с первым и вторым входами второго .элемента И, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, вы ход которого через элемент задержки соединен с первыми входами первого и второго блоков элементов И, первы и второй выходы коммутатора соедине ны соответственно с информационным входом регистра числа и входом младших разрядов счетчика адреса, выходы регистра числа и счетчика адреса соединены соответственно с вторыми входами первого и второго блоков элементов И, выходы которых являются соответственно числовым и адресным выходами устройства, введены регистр исходного базового адреса, регистр фиксированного базового адреса, регистр присвоенного базового адреса, схема сравнения, третий и четвертый элементы И и вто рой элемент ИЛИ, причем третий выход коммутатора соединен с входом регистра исходного базового адреса выход которого соединен с первь1М входом схемы сравнения и первым вхо дом третьего элемента И, выход регистра фиксированного базового адре са соединен с вторым входом схемы сравнения, выходы равенства и неравенства которбй соединены соответст .венно с первым входом четвертого элемента И и вторым входом третьего элемента И, вход установки присвоен ного базового адреса устройства сое динен с информационным входом регис ipa присвоенного базового адреса, выход которого соединен с вторым входом четвертого элемента И, выход третьего и четвертого элементов И . соединены соответственно с первым и вторым входами второго элемен- . 444 .та ИЛИ, выход которого соединен с входами старших разрядов счетчика адресов. На фиг. 1 представлена блок-схема предлагаемого устройства для модификации адреса зон памяти, на фиг. 2 и 3 - соответственно блок-схема блока анализа признаков и распределения импульсов. Устройство содержит коммутатор 1, регистр 2 числа, счетчик 3 адреса, первый и второй блоки элементов И 4 и 5, блок 6 анализа признаков, первый элемент 7 задержки, первый элемент ИЛИ 8, первый 9 и второй 10 элементы И, распределитель 11 импульсов, регистр 12 исходного базового адреса, регистр 13 фиксированного базового адреса, регистр 14 присвоенного базового адреса, схему 15 сравнения, третий 16 и четвертый 17 элементы И, второй элемент ИЛИ 18. Каждый- из регистров 12, 13 и 14 конструктивно представляет собой, например, набор триггеров, количество которьгх определяется разрядностью базового адреса. . Информационный вход 19 устройства соединен с информационным входом коммутатора 1, вход 20 начальной установки устройства соединен с установочным входом блока 6 анализа признаков, первый и второй выходы которого соединены с управляющими входами коммутатора 1. Тактовый вход 21 устройства соединен с тактовым входом блока 6 анализа признаков, тактовым входом распределителя 11 импульсов и первым входом первого элемента И 9, выход которого соединен с первым входом первого элемента ИЛИ 8 и входом Плюс единица счетчика 3 адреса. Вход 22 признака конца массива записываемой информации соединен с входом начальной установки блока 6 анализа признаков и входом останова распределителя 11 импульсов, первый, второй и третий выходы которого соединены соответственно с вторым входом первого элемента И 9, первьм и вторым входами второго элемента И 10. Выход второго элемента И 10 соединен с вторым входом первого элемента ИЛИ 8, выход которого через элемент 7 задержки соединен с управляющими входами первого 4 и второ- го 5 блоков элементов И;

51

Выход числа и младших разрядов адреса коммутации соединен соответственно с информационным входом регистра 2 числа и входами младших разрядов счетчик 3 адреса, выходы регистра 2 числа и счетчика 3 адреса соединены соответственно с информационными входами первого 4 и второго 5 блоков элементов И, выходы которых являются соответственно числовым 23 и адресным 24 выходами устройства.

Выходы старших разрядов адреса коммутатора 1 соединены с входами регистра 12 исходного базового адреса, выход которого соединен с первым входом схемы 15 сравнения и первым входом третьего элемента И 15,

Выход регистра 13 фиксированного базового адреса соединен с вторым входом схемы сравнения, выходы равенства и неравенства которой соединены соответственнр с первым входом четвертого элемента И 17 и вторым входом третьего элемента И 16.

Вход 25 установки присвоенного базового адреса соединен с информационным входом регистра 14 присвоенного базового адреса, выход которого соединен с вторым входом четвертого элемента И 17. Выходы третьего 1 6 и четвертого 17 элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ 18, выход которого соединен с входами старших разрядов счетчика 3 адреса.

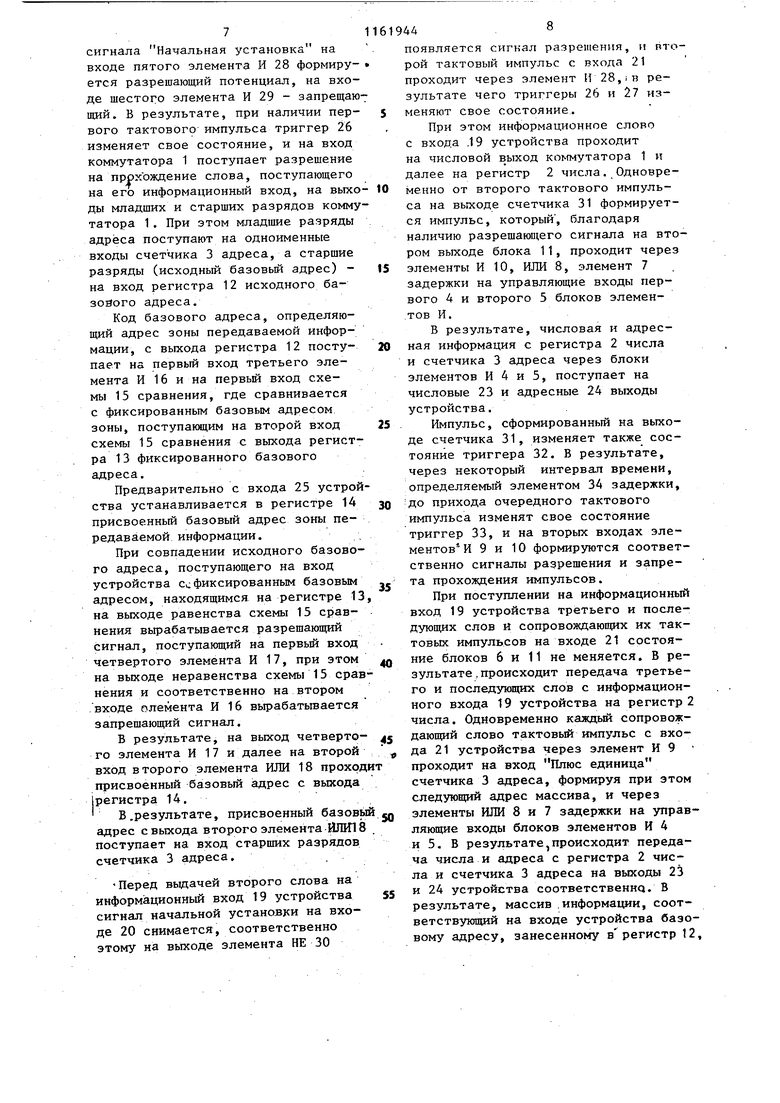

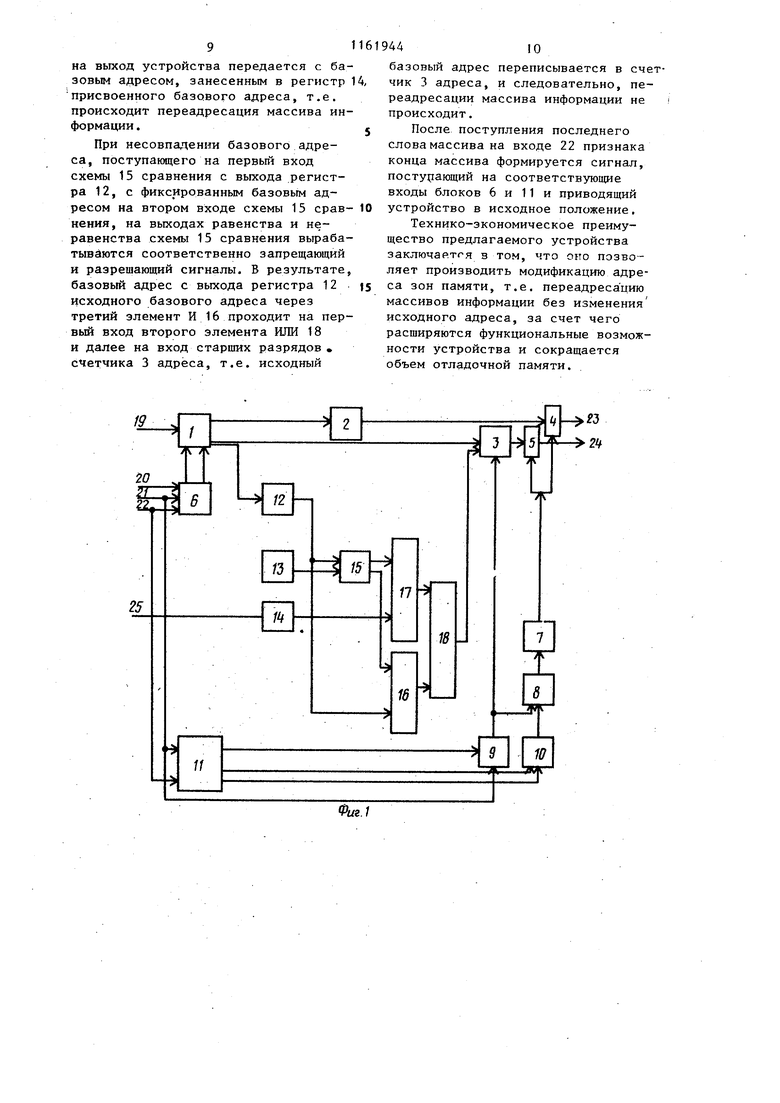

Елок 6 анализа признаков содержит первьй и второй триггеры 26 и 27, пятый и шестой элементы И 28 и 29 и элемент НЕ 30, выход которого соединен с первым входом шестого элемента И 29. Выход пятого элемента И 28 подключен к-первому входу первого триггера 26, а выход шестого элемента И 29 - к второму входу первого триггера 26 и первому входу второго триггера 27. Вход элемента НЕ 30 и первый вход пятого элемента И 28 соединены и являются входом начальной установки блока 6 анализа признаков, вторые входы пятого и шестого элементов И 28 .и 29 соединены и являютс тактовым входом блока 6 анализа признаков, третий вход первого триггера 26 и второй вход второго триггера 7 соединены и являются входом начальной установки блока 6. Выходы

446

первого и второго триггеров 26 и 27 являются соответственно первым и вторым выходами блока 6 анализа признаков .

Распределитель 11 ,импульсов содержит счетчик 31, третий и четвертый триггеры 32 и 33 и второй элемент 34 задержки.

Первьй и второй входы счетчика 31 являются соответственно тактовым входом и входом останова блока 11, второй вход счетчика 31 соединен с первыми входами третьего 32 и четвертого 33 триггеров, а выход счетчика 31 соединен с первыми входами третьего 32 и четвертого 33 триггеров, а выход счетчика 31 соединен с вторым входом третьего триггера 32, выход которого подключен к входу второго элемента 34 задержки, выход которого подключен к второму входу четвертого триггера 33 и является первым выходом распределителя 11 импульсов. I

Выходы четвертоготриггера 33

и счетчика 31 являются соответственно вторым и третьим выходами распределителя 11 импульсов.

Устройство работает следующим образом.

Информация, представленная в двоичном коде, с информационного входа. 19 поступает на вход KOMi-jyTaтора 1, которьй по сигналам из блока 6 производит ее распределение на адресную и числовую. Каждое информационное слово, приходящее на вход коммутатора 1, сопровождается тактовым импульсом, поступающим на вход 21 устройства. При этом первым и после последнего передаваемого слова соответственно на входы 20 и 22 устройства поступают сигналы. Начальная установка и Признак конца массива. Блок 6 анализирует наличие этих сигналов , на своих входах.

В исходном состоянии перед началом поступления очередного массива информации с выходов. блoka 6 и первого и второго выходов блока 11 поступают в блок 1 и на элементы 9 и 10 потенциалы, запрещающие прохождение информации через блок 1 и тактовых импульсов через элемент И 9, а с третьего выхода блока 11 - разрешающий потенциал. При появлении на входе 20 устройства

7

сигнала Начальная установка на входе пятого элемента И 28 формируется разрешающий потенциал, на входе шестого элемента И 29 - запрещаю щий. В результате, при наличии первого тактового импульса триггер 26 изменяет свое состояние, и на вход коммутатора 1 поступает разрешение на прохождение слова, поступающего на его информационный вход, на выхо ды младших и старших разрядов коммутатора 1. При этом младшие разряды адреса поступают на одноименные входы счетчика 3 адреса, а старшие разряды (исходный базовый адрес) на вход регистра 12 исходного базов(ого адреса.

Код базового адреса, определяющий адрес зоны передаваемой информации, с выхода регистра 12 поступает на первый вход третьего элемента И 16 и на первый вход схемы 15 сравнения, где сравнивается с фиксированным базовым адресом зоны, поступающим на второй вход схемы 15 сравнения с выхода регистра 13 фиксированного базового адреса.

Предварительно с входа 25 устройства устанавливается в регистре 14 присвоенный базовый адрес зоны передаваемой информации.

При совпадении исходного базового адреса, поступающего на вход устройства ссфиксированным базовым адресом, находящимся на регистре 13 на выходе равенства схемы 15 сравнения вырабатывается разрешающий сигнал, поступающий на первый вход четвертого элемента И 17, при этом на выходе неравенства схемы 15 сравнения и соответственно на втором

.входе олемента И 16 вырабатьгеается запрещающий сигнал.

В результате, на выход четвертого элемента И 17 и далее на второй вход второго элемента ИЛИ 18 проход присвоенный базовый адрес с зыхокл

|регистра 14.

В .результате, присвоенный базовь адрес с выхода второго элемента ЙШП 8 поступает на вход старших разрялов счетчика 3 адреса.

Перед выдачей второго слова на информационный вход 19 устройства сигнал начальной установки на входе 20 снимается, соответственно этому на выходе элемента НЕ 30

8

появляется сигнал разрешения, и второй тактовый импульс с входа 21 проходит через элемент И 28, ITS результате чего триггеры 26 и 27 изменяют свое состояние.

При этом информационное слово с входа .19 устройства проходит на числовой выход KONfMyTaTOpa 1 и далее на регистр 2 числа. Одновременно от второго тактового импульса на выходе счетчика 31 формируется импульс, который , благодаря наличию разрешающего сигнала на втором выходе блока 11, проходит через элементы И 10, ИЛИ 8, элемент 7 задержки на управляющие входы первого 4 и второго 5 блоков элементов И.

В результате, числовая и адресная информация с регистра 2 числа и счетчика 3 адреса через блоки элементов И 4 и 5, поступает на числовые 23 и адресные 24 выходы устройства.

Импульс, сформированный на выходе счетчика 31, изменяет также состояние триггера 32. В результате, через некоторый интерватт времени, определяемый элементом 34 задержки, :до прихода очередного тактового импульса изменят свое состояние триггер 33, и на вторых входах элементов И 9 и 10 формируются соответственно сигналы разрешения и запрета прохождения импульсов.

При поступлении на информационный вход 19 устройства третьего и последующих слов и сопровождающих их тактовых импульсов на входе 21 состояние блоков 6 и 11 не меняется. В результате , происходит передача третьего и последующих слов с информационного входа 19 устройства на регистр числа. Одновременно каждый сопровождающий слово тактовый импульс с входа 21 устройства через элемент И 9 проходит на вход Плюс единица счетчика 3 адреса, формируя при этом следующий адрес массива, и через элементы ИЛИ 8 и 7 задержки на управляющие входы блоков элементов И 4 и 5. В результате,происходит передача числа и адреса с регистра 2 числа и счетчика 3 адреса на выходы 23 и 24 устройства соответственно. В результате, массив .информащ1и, соответствующий на входе устройства базовому адресу, занесенному в регистр 1

9

на выход устройства передается с базовым адресом, занесенным в регистр присвоенного базового адреса, т.е. происходит переадресация массива информации.

При несовпадении базового адреса, поступающего на первьш вход схемы 15 сравнения с выхода регистра 12, с фиксированным базовым адресом на втором входе схемы 15 сравнения, на выходах равенства и неравенства схемы 15 сравнения вырабатываются соответственно запрещающий и разрешающий сигналы. В результате, базовый адрес с выхода регистра 12 исходного базового адреса через третий злемент И 16 проходит на первый вход второго элемента ИЛИ 18 и далее на вход старших разрядов . счетчика 3 адреса, т.е. исходный

94410

базовый адрес переписывается в счечик 3 адреса, и следовательно, переадресации массива информации не происходит.

После поступления последнего слова массива на входе 22 признака конца массива формируется сигнал, постуцающий на соответствующие входы блоков 6 и 11 и приводящий устройство в исходное положение.

Технико-экономическое преимущество предлагаемого устройства заключар.тгя в том, что око позволяет производить модификацию адреса зон памяти, т.е. переадресацию массивов информации без изменения исходного адреса, за счет чего расширяются функциональные возможности устройства и сокращается объем отладочной памяти.

Фиг. 2

Фигд

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Флорес И | |||

| Внешние устройства ЭВМ | |||

| М., Мир, 1975, с | |||

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для считывания информации | 1975 |

|

SU542240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кодов | 1979 |

|

SU834693A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-15—Публикация

1983-04-08—Подача