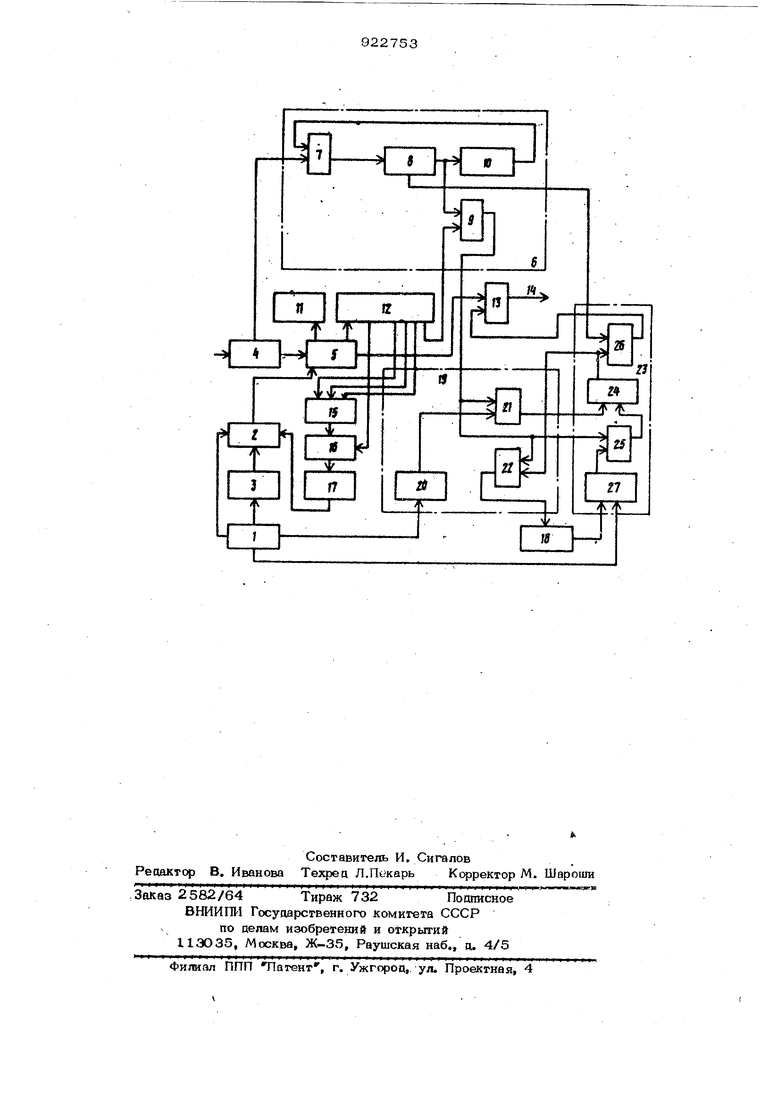

I Изобретение относится к вычислительной техшке и гфедназнач о аля отлапки программ специализированных цифровых вычислительных устройств. Известны устройства шга отлаокн грограмм, соаержаише индексной регистр, совигакнций регистр, накопительный и коммутационный элемент, логический элемент, устройртво ввооа-вывопа накопитель щля командных слов, уг|) блок с тактовым генератором, преобразователь ннформации в сигналы для инцикации ttlHt }. Недостаток этих устройств - невозможность имитировать сбои программнымi способом. Наиболее близким к изобретению по . технической сущности является устройстВо для отладки программ, сод пкашее блок , 1фиема инфс мации, блок контроля, два элёгйевта ИЛИ,блок анализа Кода команд, сови;Ровые регистры команд и ивформации,блок ,управлени % блок индикации, передающий блок в котором для повышения прстзводиТельаости отладки введено наборное поле команд и блок управления передачей ивформации З 3 Недостатком известного устройства является низкая производительность фв вмв ташш искажения информационных staocHBOB, выдаваемьсс в ЭВМ, так как в атом cityчае необходимо предварительно перед вь дачей информации набирать иа панели управления с наборным полем искаженную информацию. Цель изобретения - увешчение быстродействия при отладке щ ограмм. Поставлшная цель достигается тем, что в устройство для отладки программ, содержащее наборное поле, дешифратор адреса, блок памяти, регистр обмена, блок сопряжения с системой, блок индикация, дешифратор запросов, шифратор адреса счетчик а|фесов, второй дешифратор аиреса и блок син:(ронизации, причем «ход устройства соединен с входом бло ка сопряжения с системой, я второй выходы которого соединены соответ сгвшно с входом блока сишфонизация н с первым вхоаом регистра обмена, первый и втфой выходы регистра обмена соешшопы соответствеино с входом блока ИНШ1КОЦИИ и цешифратором запросов, первый, второй, третий, четвертый и пятый выхопы аешифратора запросов соеоине ны соответс твеш1о с первым, вторым и трегьим входом шифратора адреса, со счетным входом счетчкка адреса и вторым входом блока синхронизации, первый и второй выходы набранного поля соединены соответственно с первым входом блока памяти и входом первого дешифратора адреса, выход Которого соединен с вторым входом блока памяти, выход шифратора соединен с информацио1шым входом рчетчика адресов, выход которого соединен с входом второго дешифратора адреса, выход второго дешифратора адреса соединен с третьим входом блока памяти, выход которого соеш1нен с вторым входом регистра обмена, введены блок управлени режимом, счетчик сбоев, элемент Ни блок формирсшания сбоев, состоядий из первого и второго элементов И, триггера и схемы сравнения, причем третий и четвертый выходы наборного поля соединены соответственно с первым входбм блока управления режимом, с первым входом схемы сравнения блока формирования сбоев, первый и второй выходы блока yi равления режимом соединены соответственно со счетным входом счетчика сбоев и еди1шчным входом триггера блока формирования сбоев, выход счетчика сбоев соединен со вторым входом схемы сравнения блока формирования сбоев, выход схемы сравнения блока формирования сбоев соединен с первым входом элемента И, выход которого соединен с нулевым входом триггера, выход которого соединен с первым входом второго элемента И и является первым выходом блока формирования сбоев, выход второго элемента И блока формирования сбоев является вто рым выходом блока формирования сбоев, третий выход регистра обмена соединен с первым входом элемента И, выход которо го является выходом устройства, первый и второй выходы блока формирования сбоев соединены соответствогао с втфым входом блока управления режимом и вторым, входом элемента И, первый выход блока синхронизации соединен с третьим входом блока управления режимом и вторым входом первого элемента И блока бормировакия сбоев, второй выход блока 1-инхрониаацни соединен с вторым входом вго рг тоэломентч И(Злокяформировпния сбоев. 922 Кроме того, блок управле1тя режимом содержит формирователь одиночных им- пульсда, первый и второй элементы И, причем первый вход блока соединен с входом формирователя одиночных; импульсов, выход которого соединен с первым входом первого элемента И, второй вход блока соединен с первым входом второго элемента И, выход которого является первым выходом блока, третий вход блока соединен с вторыми входами первого и второго элементов И, выход первого элемента И является вторым выходом блока. На чертеже представлена блоксхема усгройства цля отладки программ. Наборное поле I используется для набора кода информа1шо шйх слов и кода адреса, соединено первьгм выходом с первым входом блока 2 памяти и через дешифратор 3 адреса вторым выходом зоединено с вторым входом блока памяти. Принимаемая служебная информация через блок 4 сопряжения с системой записывается в регистр 5 обмена, второй вход которого соединеян с выходом блока памяти. Для синхронизации работы устройства используется блок 6 синхронизации, содержащий элемент ИЛИ 7, счетчик 8 тактов с дешифратором, элемент И 9 и тактовый генератор 10, вход которого соединен с первым вькодом счетчика 8 и первым входом элемента И 9, выход тактового генератора 10 с первым входом элемента ИЛИ 7, второй вход которого соединен с первым выходом блока 4 сопряжения с системой, а выход - с входом счетчика 8. Содержимое регистра обмена вьювечивается с помощью блока 11 индикации, соеднн«1ного с первым выходом регистра обмена. Для анализа служебной информации, записанной в регистр обмена, используется дешифратор 12 запросов, вход которого соединен с вторым выходом регистра обмена, третий выход которого, через элементы И 13 соединен с выходом 14 устройства. С информационных выходов дешифратора запросов (число информационных выходов соответствует количеству массивов и MokeT быть любым, в предлагаемом случае их 3) признаки запросе массивов подаются на информационные входы шифратфа 15 адреса, выход которого соешшен с информационным входом счетчика 16 оцресоп, счетный 562 вход которого соецинеи с четвертым выхоцом цешифратора запросов, а выхоц с входом второго дешифратора 17 адреса, выход которого соединен с третьим входом блока памяти. Пятый выход дешифратора запросов соединен с вторым входом блока 6 синхронизации . Счет сбойных массивов информации, шсло которых задается с помощью наборного поля, осуществляется счетчиком 18 сбоев, управление которым производится блоком 19 управления режимом, содфжашим формирователь 20 одиночного импульса и два элемента И 21 и 22, а сигнал сбой в определенные временные интервалы формируется в блоке 23 формирования сбоев, третий и четвертый выходы наборного поля соешшены с первым блока 19 и с первым входом блока 23 формирования сбоев, содержащим триг гер 24, два элемента И 25 и 26 и схему 27 сравнения, первый и второй входы которой соединены соответственно с выходом счетчика 18 и четвертым выходом наборного поля, а выход через первый элемент И 25 блока 23 соединен с обнуляющим входом триггера 24, выход которого соединен с первым входом второго элемента И 26 блока 19 управления режимом, подключенной к счетчи- ку 18 сбоев и через второй элемент И 2 блока 23, соединенного вторым входом с вторым выходом блока синхрсжизации, соединен с вторым входом элемента И 13 а единичный вход триггера - с выходом первого элемента И 2 I блока 19 управления режимом, третий вход которого соединен с выходом блока 6 синхронизации, вторым входом второго элемента И блока 19 управления режимом и вторым входом первого элемента И блока 23, а первый вход первого элемента И блока 19 через формирователь одиночных импульсов - с третьим выходом наборного поля. Устройство работает следующим образом. Перед началом работы массивы информационных слов, устанавливаемые с .помощью наборного поля I по адресам, которые задаются тем же и дешифрируются де1йифратором 3 адреса, заносятся в блок 2 памяти. Устройство осуществляет поием, расшифровку 8-и разрядной служебной информации (запрос выдачи массивов и слов в смассиве) и выдачу запрашиваемого массива информационных слов, занесенных в блок 2 памяти с наборного поля I. 536 Обмете информацной гх;у1|1оствп-лется acinixpoinio с прт1уш1тош:,иой ззсшсью инфсрмации на частоте той же системы, которая выдает информацию. Входная служебная информация через блок 4 сопряжения записывается в регистр 5 обмена. Выделяемые в блоке 4 Синхроимпульсы используются для загшси приН11маемой информации в регистр 5 обмена (на чертеже не показано), а также подаются в блок 6 С1шхр0 газации, содержаший элемент ИЛИ 7, счетчик 8 тактов с деилифратором, элемент И 9 и тактовый генератор 1О. Поступающие в блок 6 синхронизащш импульсы через элемент ИЛИ ; 7 подаются на счегчик 8, который осушествляет счет этих импульсов. Восьмым тактом со счетчика 8, т.е. после приема служебной информации, запускается так- товый генератор 10, выходные импульсы которого через элемент ИЛИ 7 также поступают на вход счетчика 8, который продолжает счет импульсов, организуя заданный цикл приема-выдачи информации, после чего обнуляется. Тактовый генератор Ю выдает, кроме того, послецовательность импульсов, необходимых для синхронизации отдельных узлов устройства (связи синхроимпульсов не показаны). После приема и записи в регистр 5 обмена служебной информации дешифратором 12 анализируется содержимое регистра 5 обмена и формируются признаки запроса требуемого массива информационных слов (на первом, втором и третьем выходах), признак запроса слова в массиве (четвертый выход) и признак запроса любого массива (пятый выход). При запросе массива устройство выдает только первое слово массива, каждое последующее слово в массиве выдается по запросу слова. По сформированному признаку запрашиваемого массива в шифратфе 15 форм1фуется код, соответствующий адресу первого слова данного массива, который заносится в счетчик 16 и дешифрируется вторым дешифратором 17. Полученный адрес поступает в блок 2 памяти, схгкуда в соответствии с полученным адресом с тисывается в регистр 5 обмена информация. Из регистра 5 обмена 1Шформации через элемент И 13 i выход 14 поступает в отлаживаемую сис1ему . Выдаваемая из регистра обмена информация высвечивается с помощью блока II 1шаиксш1ш. При расшифровке деш1фратором 12 признака запроса слоьа счетчик KJ приП.чпдяот

еоиницу, формируя новый адрес следующего списываемого из блока 2 памяти слова запрашиваемого массива. При не обходимосги введенияВ выдаваемую ин ффмаиию. искажений на наборном поле ус танавш1Вается требуемое число сбойных массивов информации. Цри нажатии KHOtiки сбой число сборных массивов подается на схему 27 сравнения, а формирователь 2О одиночных импульсов формиру- ет импульс, который три наличии признака запроса массива в восьмом такте с выхода элементов И блока синхрониза;ции бС апрос начала массива ) через первый элемент И 21 блока 19 запускает триггер 24, выходной сигнал которого через второй элемент И 26 блока 23 при наличии признака определенного временного интервала, в котором нужно произвести искажение инффмации, по даваемо го с выхода 8 блока 6 синхро,низации запрещает прохождение информации через элемент И 13 на выход 14 устройства. При срабатывании триггера 24 через втфой элемент И 22 блока 19 при наличии сигпала Запрос начала массива с выхода элемента И блока 6 сингфонизации запускается счетчик 18 t6oев, котфый осуществляет счет сигналов Запрос начала массива до момента ера- внения показания счетчика 18 сбоев с числом сбойных массивов, заданным на наборном поле I. После выработки схемой 27 сражения сигналов сравнения и при наличии 1ризнака Запрос начала мае сива с выхода элемента И блока 6 синхронизации через первый элемент И 25 блока 23 триггер 24 обнуляется и снова разрешает прохожиение. на выход информации из регистра 5 обмена.

Таким образом, предлагаемое ycTpoitetво для отладки.: программ за счет введения счетчика сбоев, блока управления режимом, блока формирования сбоев и элемента И, соединенных соответствующим образом между собой с наборным полем блоком синхронизации и регистром обмена, позволяет легко и.быстро путем управления с наборного поля в гаобой момент огладгси программ осуществлять внесение сбоев любого количества массивов информационных слов, выдаваемых из ycTpoita.TBa, без предварительного занесения их в блок памяти, что существенно увеличивает быстродействие при от- лацке программ. Формула изобретения

Усзройство для отладки программ, сод эжащее наборное поле, дешифратор адреса, блей памяти, регистр обмена, блок сопряжения с системой, блок индикации, дешифратор заг эосов, шифратор адреса, счетчик адресе, второй дешифратф адреса и блек синхронизации, причем вход устройства соединен с входом блс«са сопряжения с системой, первый и второй выходы Которого соединены соо№етствея но с входом блока синхронизации и с первым входом регистра обмена, первый и второй выходы регистра обмена соединены соответственно с входом блока индикации и дешифратором зафосов, первый, второй, трещи, четвертый и пятый вы ходы дешифратора запросов соединены соответственно, с первым, вторым и третьим входом шифратфа афеса, со счетным входом счетчика адреса и вторым входом блока синхронизации, первый и второй выходы наборного поля соединены соответственно с первым входом блока памяти и входом первого дешифратора адреса, выход Которого соединен с вторым входом блока памяти, выход шифратора соединен с информационным вхсм дом счетчика адресов, выход которого соединен с входом второго дешифратора адреса, выход второго дешифратора ад- реса соединен с третьим входом блока памяти, выход которого соединен с вторым входом регисора обмена, отличающееся тем, что, с целью увеличения бьютродействия при отладке, в него введены блок управления режимом, счетчик сбоев, элемент И и блок формирования сбоев, состоящий из первого и второго элементов И, триггера и схемы сравнения, причем третий и четвертый выходы наборного поля соединены соответственно с первым входом блока управления режимом, с первым входом схемы сравнения блока ффмирования сбоев, первый и второй выходы блока управления режимом соединены соответственно со счетным входом счетчика сбоев и единичным входом триггера блока формирования сбоев, вьосод счетчика сбоев соединен с вторым входом схемы сравнения блока фсрмировавия сбоев, выход схемы сравнения блока формирования сбоев соединен с первым входом элемента И, вызазд Которого соединен с нулевым входом триггера, которого соединен с первым входом второго элемента И ц является первым выходом блока формированвя сбоев, выход второго элемента И блока формирования сбоев является вторым выходом блока формирования сбоев, трети выход регистра обмена соединен

с первым вхоцом элемента И, выхоа которого является выхоцом устройства, первый и второй выхоаы блока формиро- вания сбоев с оеоинены соответственно с вторым вхоаом блока управления режимом и вторым вхоаом элемента И, .первый выход блока синхронизации соеоинен с третьим вхоцом блока управления режимом и вторым BxocioM первого элемента И блока формирования сбоев, второй выход блока синхронизации соединен с вторым входом второго элемента И блока формирования сбоев.

2. Устройство по п. I, о т л и ч а ю щ е е с я тем, что блок управления режимом содержит формирователь одиночных импульсов, первый и второй элементы И причем первый вход блока соединен

С входом формирователя одиночных импульсов, выход которого соединен с первым входом первого элемента И, второй вход блока соединен с первым входом второго элемента И, выход которого является первым выходом блока, третий вход блока с.оединен-; с вторыми входами первого и .второго элементов И, выход первого элвмеНта И является вторым выходом блока.

Источники информации, принятые во внимание ПРИ экспеотизе

1.Заявка ФРГ Mi 22О1754 42Х, опублик. 26.04.73.

2.Заявка ФРГ N 22О7О94 42X, опублик. 12.12.74.

5

3.Авторское свидетельство СССР J 382472, кл. Q 06 F 9/06,

11.II.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1399751A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

Авторы

Даты

1982-04-23—Публикация

1980-07-08—Подача