Изобретение относится к вычисхш- тельной технике и может быть использовано для сопряжения модулей вычислительной системы с интерфейсом Об- щая шина.

Целью изобретения является повышение пропускной способности устройств при обмене массивами данных.

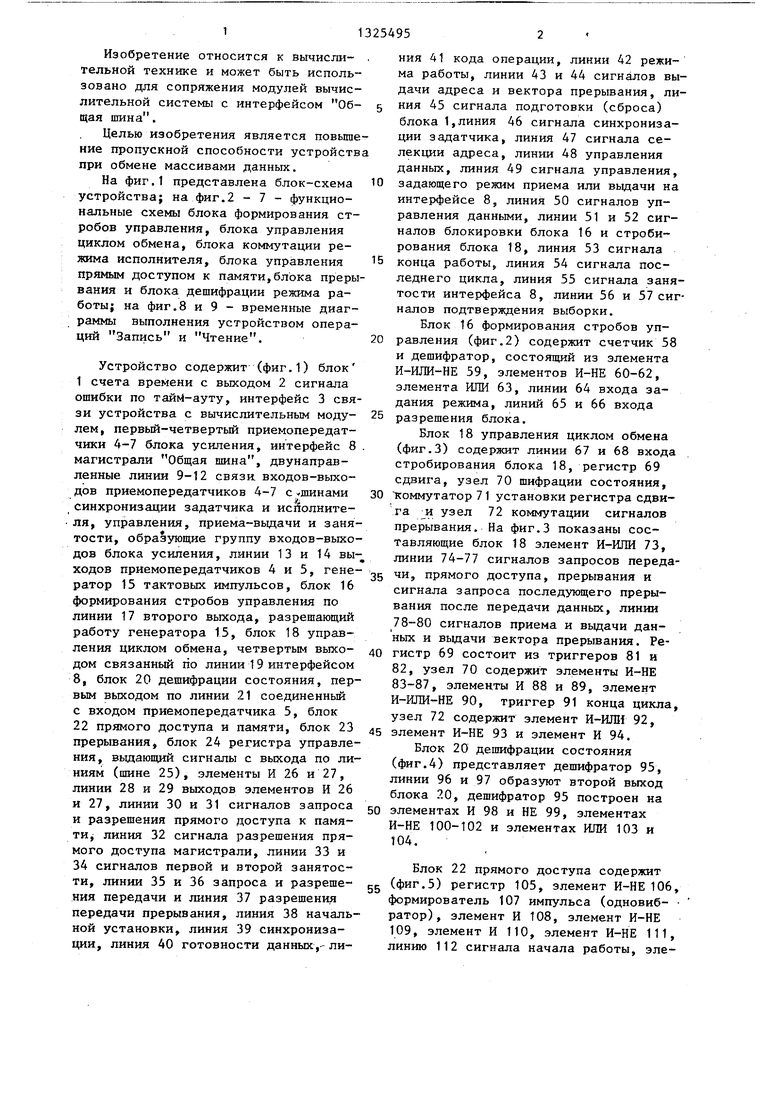

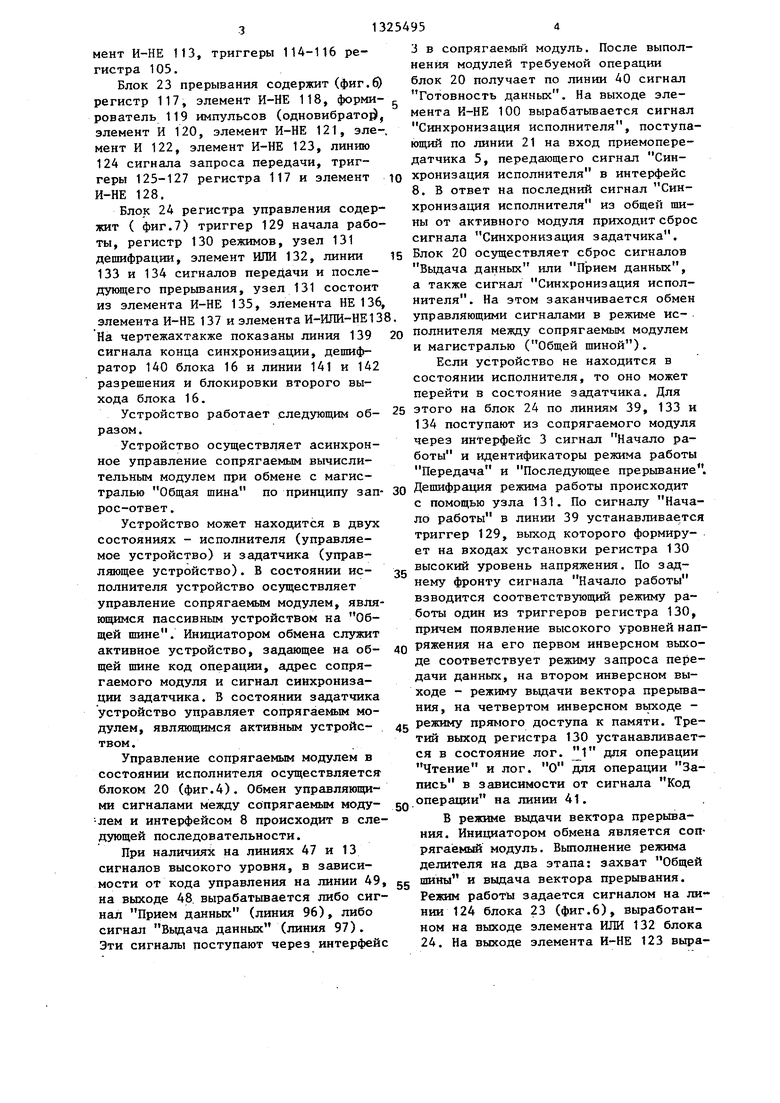

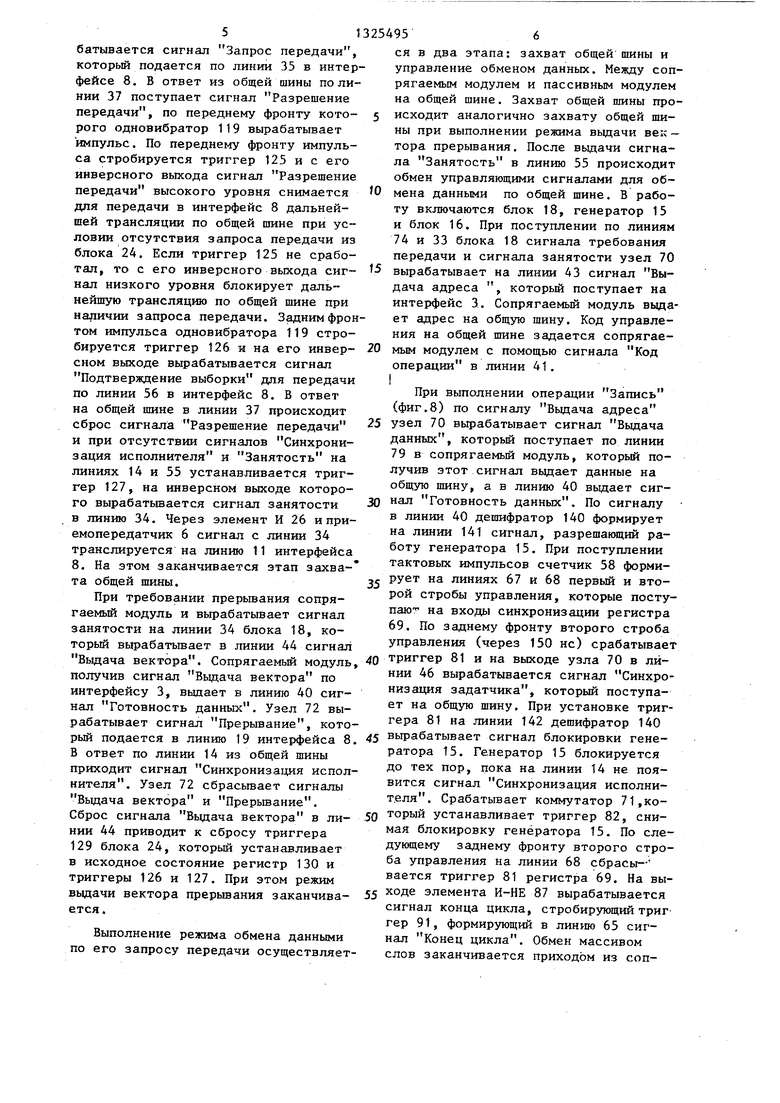

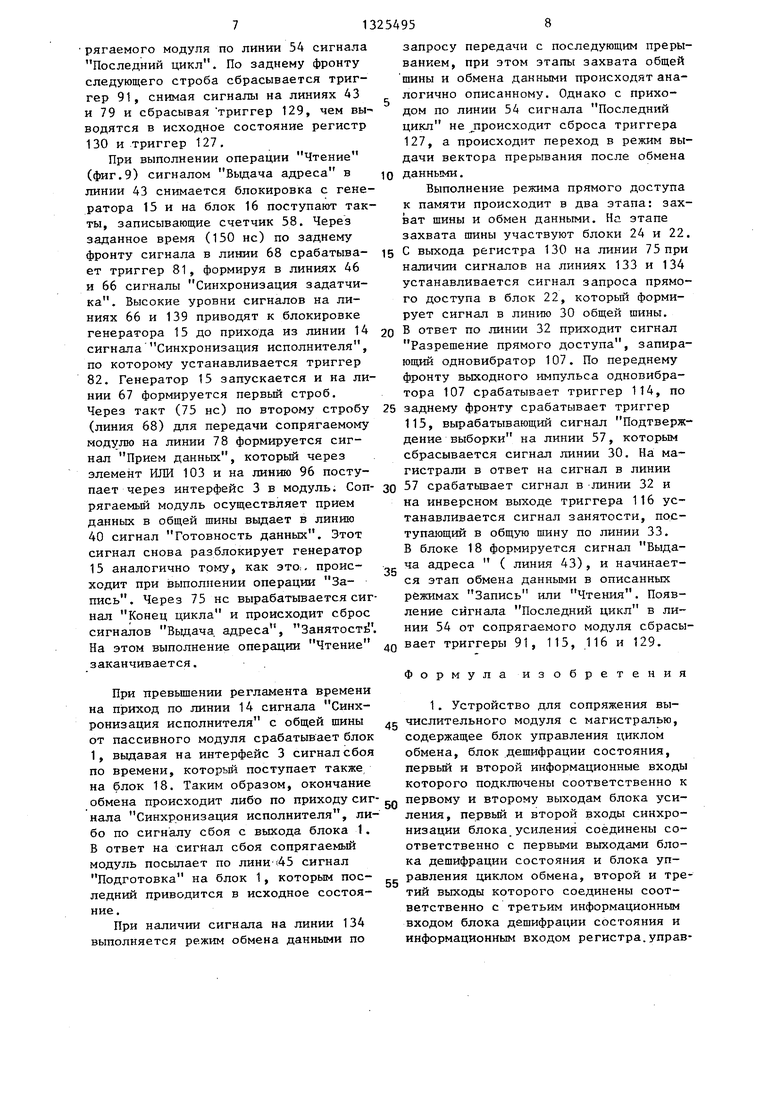

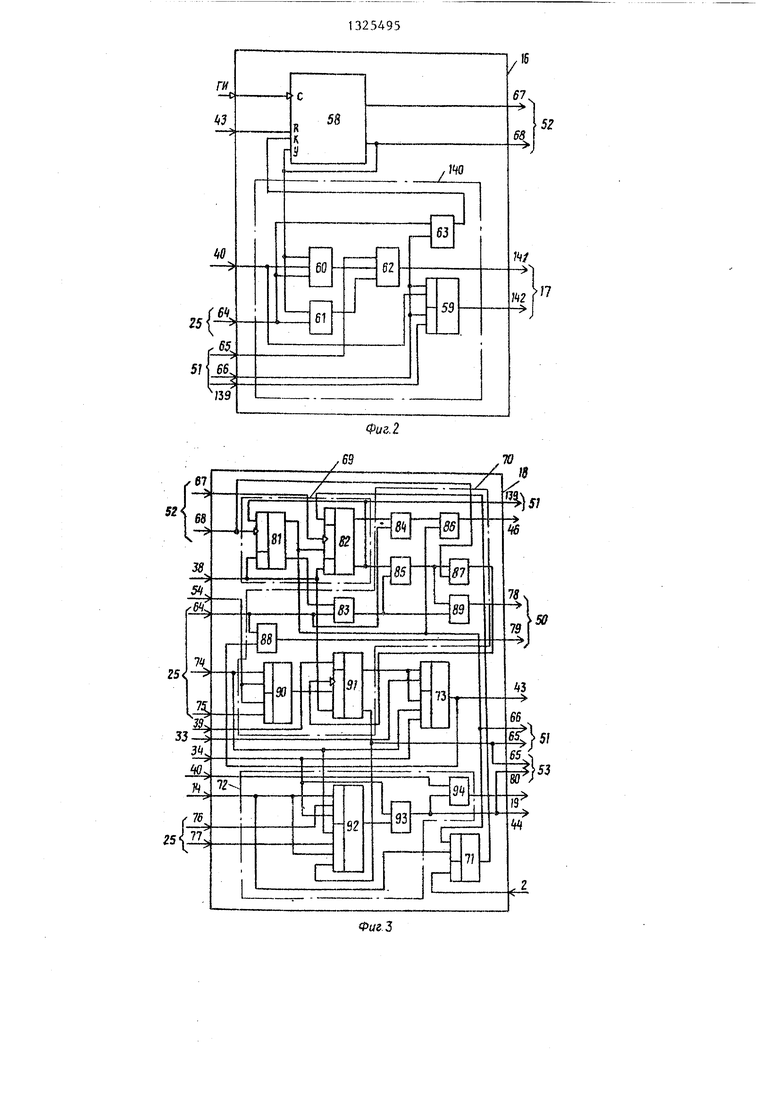

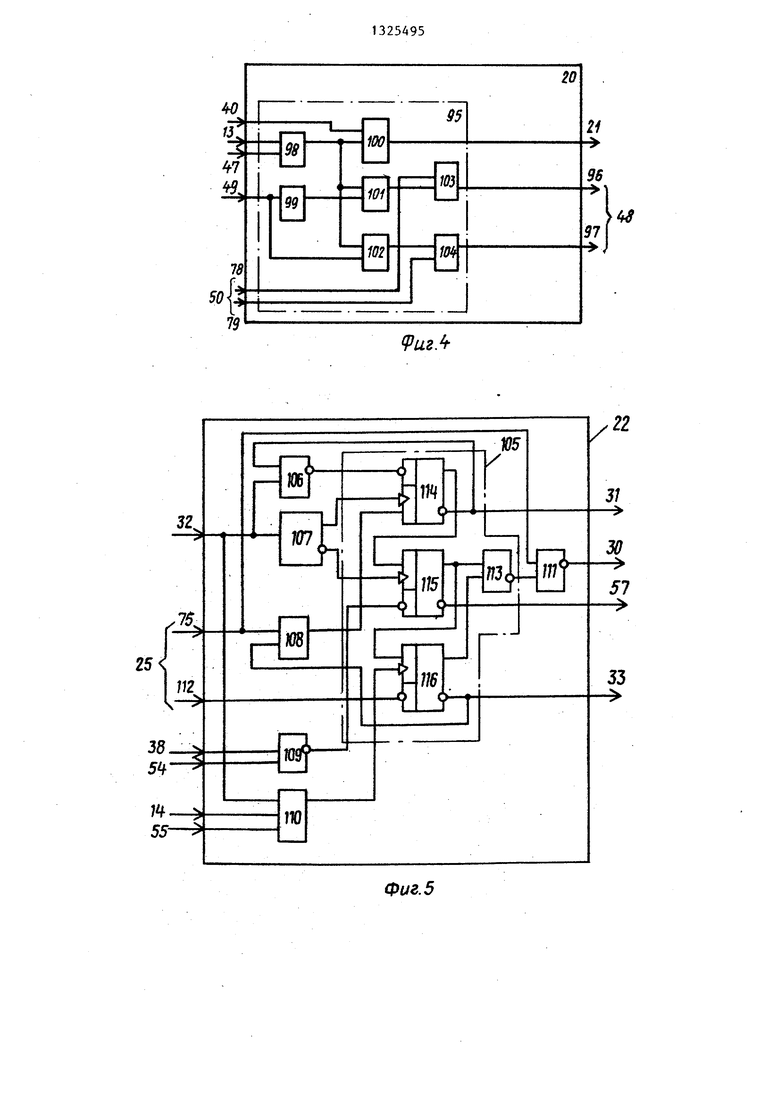

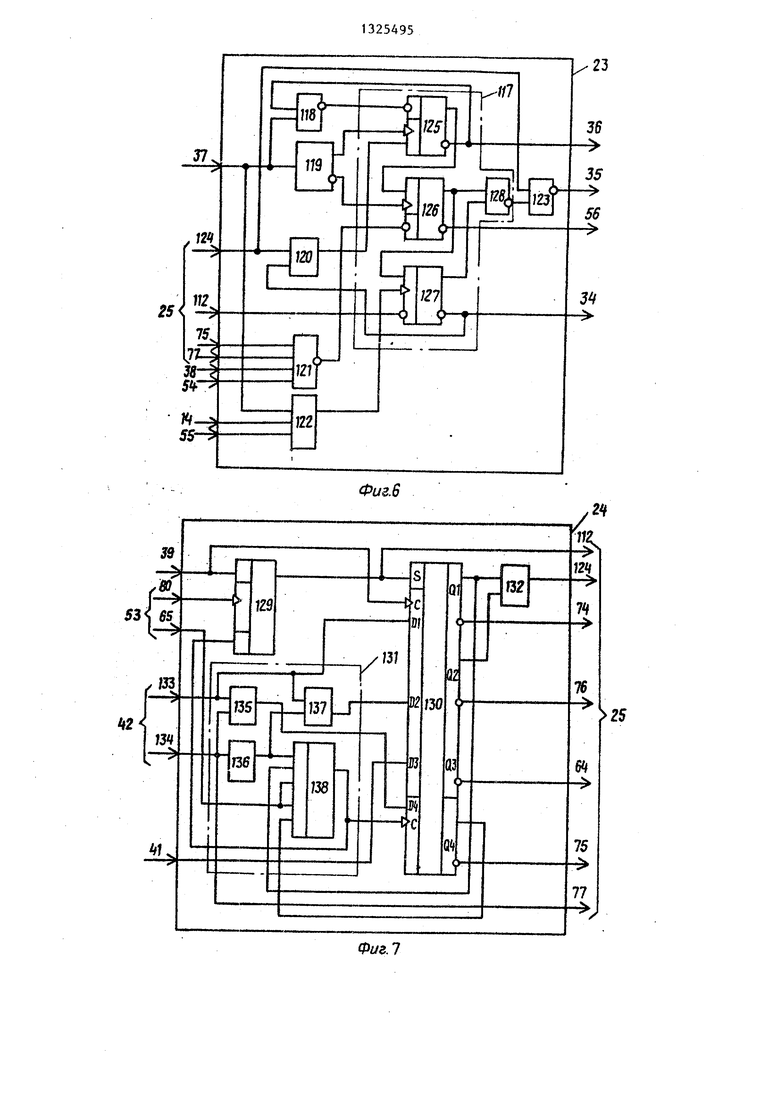

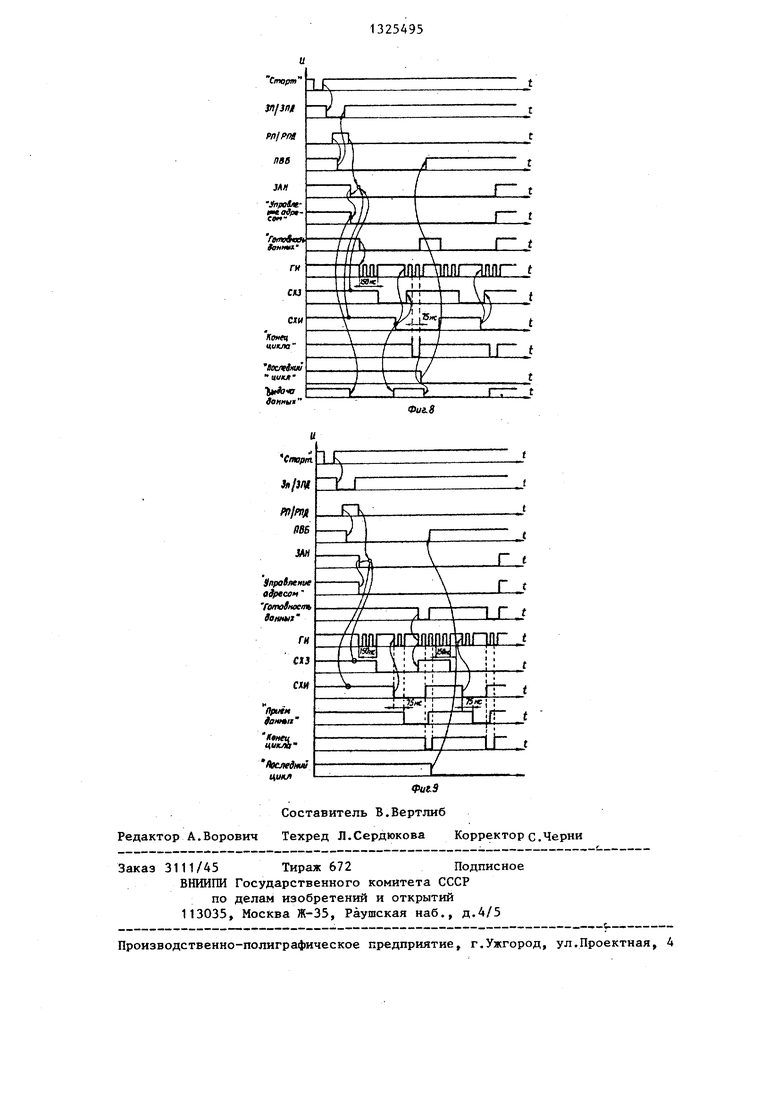

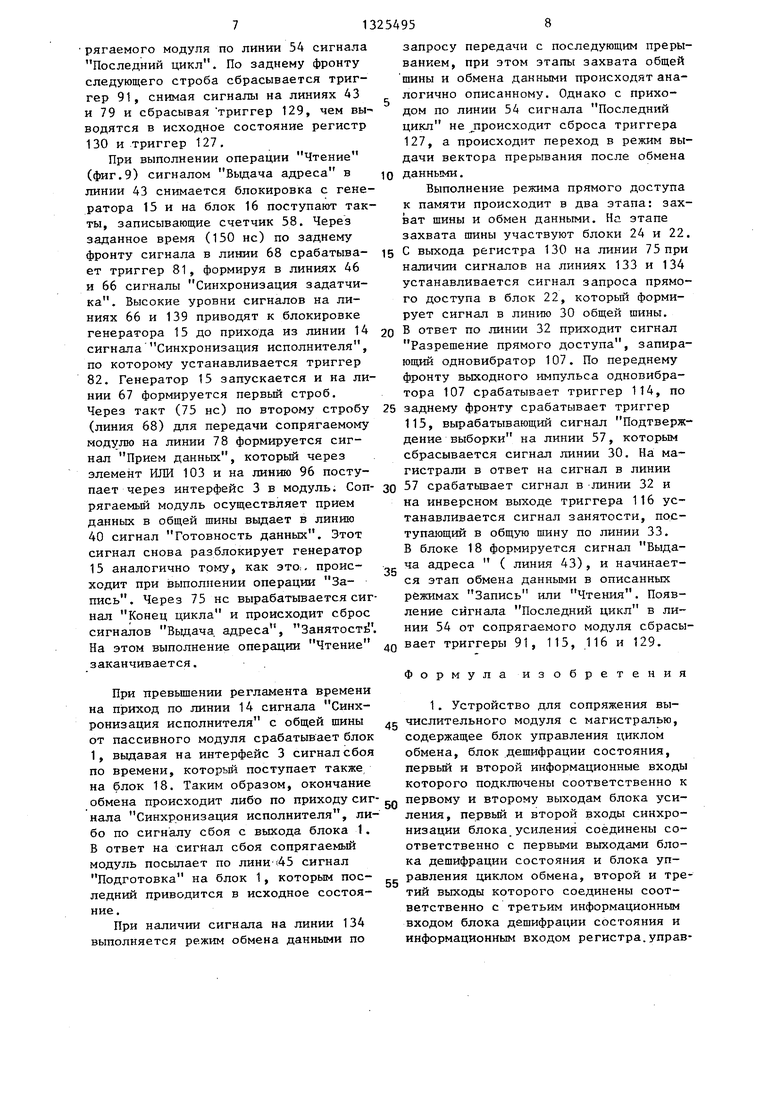

На фиг.1 представлена блок-схема устройства; на фиг.2 - 7 - функциональные схемы блока формирования стробов управления, блока управления циклом обмена, блока коммутации режима исполнителя, блока управления прямым доступом к памяти,блока прерывания и блока дешифрации режима работы; на фиг.8 и 9 - временные диаграммы выполнения устройством операций Запись и Чтение.

Устройство содержит (фиг.1) блок 1 счета времени с выходом 2 сигнала ошибки по тайм-ауту, интерфейс 3 связи устройства с вычислительным моду- лем, первый-четвертый приемопередатчики 4-7 блока усиления, интерфейс 8 магистрали Общая шина, двунаправленные линии 9-12 связи входов-выходов приемопередатчиков 4-7 с шинами синхронизации задатчика и исйолните- ля, управления, приема-выдачи и занятости, образующие группу входов-выходов блока усиления, линии 13 и 14 выходов приемопередатчиков 4 и 5, гене- ратор 15 тактовых импульсов, блок 16 формирования стробов управления по линии 17 второго выхода, разрешающий работу генератора 15, блок 18 управления циклом обмена, четвертым выхо- дом связанный по линии 19 интерфейсом 8, блок 20 дешифрации состояния, первым выходом по линии 21 соединенный с входом приемопередатчика 5, блок 22 прямого доступа и памяти, блок 23 прерывания, блок 24 регистра управления, вьщающий сигналы с выхода по линиям (шине 25), элементы И 26 и 27, линии 28 и 29 выходов элементов И 26 и 27, линии 30 и 31 сигналов запроса и разрешения прямого доступа к памя- тиj линия 32 сигнала разрешения прямого доступа магистрали, линии 33 и 34 сигналов первой и второй занятости, линии 35 и 36 запроса и разреше- НИН передачи и линия 37 разрешения передачи прерывания, линия 38 начальной установки, линия 39 синхронизации, линия 40 готовности данных,- линия 41 кода операции, линии 42 режима работы, линии 43 и 44 сигналов выдачи адреса и вектора прерывания, линия 45 сигнала подготовки (сброса) блока 1,линия 46 сигнала синхронизации задатчика, линия 47 сигнала селекции адреса, линии 48 управления данных, линия 49 сигнала управления, задающего режим приема или выдачи на интерфейсе 8, линия 50 сигналов управления данными, линии 51 и 52 сигналов блокировки блока 16 и строби- рования блока 18, линия 53 сигнала конца работы, линия 54 сигнала последнего цикла, линия 55 сигнала занятости интерфейса 8, линии 56 и 57 сигналов подтверждения выборки.

Блок 16 формирования стробов управления (фиг.2) содержит счетчик 58 и дешифратор, состоящий из элемента И-ИЛИ-НЕ 59, элементов И-НЕ 60-62, элемента ИЛИ 63, линии 64 входа задания режима, линий 65 и 66 входа разрешения блока.

Блок 18 управления циклом обмена (фиг.З) содержит линии 67 и 68 входа стробирования блока 18, регистр 69 сдвига, узел 70 шифрации состояния, коммутатор 7 1 установки регистра сдвига и узел 72 коммутации сигналов прерывания. На фиг.З показаны составляющие блок 18 элемент И-ИЛИ 73, линии 74-77 сигналов запросов передачи, прямого доступа, прерывания и сигнала запроса последующего прерывания после передачи данных, линии 78-80 сигналов приема и вьщачи данных и вьщачи вектора прерывания. Регистр 69 состоит из триггеров 81 и 82, узел 70 содержит элементы И-НЕ 83-87, элементы И 88 и 89, элемент И-ИЛИ-НЕ 90, триггер 91 конца цикла узел 72 содержит элемент И-ИЛИ 92, элемент И-НЕ 93 и элемент И 94.

Блок 20 дешифрации состояния (фиг.4) представляет дешифратор 95, линии 96 и 97 образуют второй выход блока 20, дешифратор 95 построен на элементах И 98 и НЕ 99, элементах И-НЕ 100-102 и элементах ИЛИ 103 и 104.

Блок 22 прямого доступа содержит (фиг.5) регистр 105, элемент И-НЕ 106 формирователь 107 импульса (одновиб- ратор), элемент И 108, элемент И-НЕ 109, элемент И 110, элемент И-НЕ 111 линию 112 сигнала начала работы, эле

мент И-НЕ 113, триггеры 114-116 регистра 105.

Блок 23 прерывания содержит (фиг.© регистр 117, элемент И-НЕ 118, форми- рователь 119 импульсов (одновибрато элемент И 120, элемент И-НЕ 121, элемент И 122, элемент И-НЕ 123, линию 124 сигнала запроса передачи, триггеры 125-127 регистра 117 и элемент И-НЕ 128,

Блок 24 регистра управления содержит ( фиг.7) триггер 129 начала работы, регистр 130 режимов, узел 131 дешифрации, элемент ИЛИ 132, линии 133 и 134 сигналов передачи и после- дукнцего прерьтания, узел 131 состоит из элемента И-НЕ 135, элемента НЕ 136 элемента И-НЕ 137 и элемента И-ИЛИ-НЕ13 На чертежахтакже показаны линия 139 сигнала конца синхронизации, дешифратор 140 блока 16 и линии 141 и 142 разрешения и блокировки второго выхода блока 16.

Устройство работает следующим образом .

Устройство осуществляет асинхронное управление сопрягаемым вычислительным модулем при обмене с магистралью Общая шина по принципу рос-ответ.

Устройство может находится в двух состояниях - исполнителя (управляемое устройство) и задатчика (управляющее устройство). В состоянии исполнителя устройство осуществляет управление сопрягаемым модулем, являющимся пассивным устройством на Общей шине. Инициатором обмена служит активное устройство, задающее на общей шине код операции, адрес сопрягаемого модуля и сигнал синхронизации задатчика. В состоянии задатчика устройство управляет сопрягаемым модулем, являющимся активным устройством .

Управление сопрягаемым модулем в состоянии исполнителя осуществляется блоком 20 (фиг.4). Обмен управляющими сигналами между сопрягаемым моду- лем и интерфейсом 8 происходит в следующей последовательности.

При наличиях на линиях 47 и 13 сигналов высокого уровня, в зависимости от кода управления на линии 49, на выходе 48. вырабатывается либо сигнал Прием данных (линия 96), либо сигнал Вьодача данных (линия 97). Эти сигналы поступают через интерфейс

зап-

25

, ю

8. 20 gg

3 в сопрягаемый модуль. После выполнения модулей требуемой операции блок 20 получает по линии 40 сигнал Готовность данных. На выходе элемента И-НЕ 100 вырабатывается сигнал Синхронизация исполнителя, поступающий по линии 21 на вход приемопередатчика 5, передающего сигнал Синхронизация исполнителя в интерфейс 8. В ответ на последний сигнал Синхронизация исполнителя из общей тины от активного модуля приходит сброс сигнала Синхронизация задатчика. 5 Блок 20 осуществляет сброс сигналов Выдача данных или Прием данных, а также сигнал Синхронизация исполнителя. На этом заканчивается обмен управляющими сигналами в режиме ис- полнителя между сопрягаемым модулем и магистралью (Общей шиной).

Если устройство не находится в состоянии исполнителя, то оно может перейти в состояние задатчика. Для этого на блок 24 по линиям 39, 133 и 134 поступают из сопрягаемого модуля через интерфейс 3 сигнал Начало работы и идентификаторы режима работы Передача и Последующее прерывание, 30 Дешифрация режима работы происходит

с помощью узла 131. По сигналу Начало работы в линии 39 устанавливается триггер 129, выход которого формиру- ет на входах установки регистра 130 высокий уровень напряжения. По заднему фронту сигнала Начало работы взводится соответствующий режиму работы один из триггеров регистра 130, причем появление высокого уровней нап- 4Q ряжения на его первом инверсном выходе соответствует режиму запроса передачи данных, на втором инверсном выходе - режиму вьщачи вектора прерьгаа- ния,

35

50

, на четвертом инверсном выходе - g режиму прямого доступа к памяти. Третий выход регистра 130 устанавливается в состояние лог. М дпя операции Чтение и лог. О для операции Запись в зависимости от сигнала Код операции на линии 41.

В режиме выдачи вектора прерывания. Инициатором обмена является сопрягаемый модуль. Выполнение режима делителя на два этапа: захват Общей шины и выдача вектора прерывания. Резким работы задается сигналом на ли НИИ 124 блока 23 (фиг.6), выработанном на выходе элемента ИЛИ 132 блока 24. На выходе элемента И-НЕ 123 вырабатывается сигнал Запрос передачи, который подается по линии 35 в интерфейсе 8, В ответ из общей шины по линии 37 поступает сигнал Разрешение передачи, по переднему фронту которого одновибратор 119 вырабатывает импульс. По переднему фронту импульса стробируется триггер 123 и с его инверсного выхода сигнал Разрешение передачи высокого уровня снимается для передачи в интерфейс 8 дальнейшей трансляции по общей шине при условии отсутствия запроса передачи из блока 24. Если триггер 125 не сработал, то с его инверсного выхода сигнал низкого уровня блокирует дальнейшую трансляцию по общей шине при наличии запроса передачи. Задним фронтом импульса одновибратора 119 стробируется триггер 126 и на его инверсном выходе вырабатывается сигнал Подтверждение выборки для передачи по линии 56 в интерфейс 8. В ответ на общей шине в линии 37 происходит сброс сигнала Разрешение передачи и при отсутствии сигналов Синхронизация исполнителя я Занятость на линиях 14 и 55 устанавливается триггер 127, на инверсном выходе которого вырабатьшается сигнал занятости в линию 34. Через элемент И 26 и приемопередатчик 6 сигнал с линии 34 транслируется на линию 11 интерфейса 8. На этом заканчивается этап захва- та общей шины.

При требовании прерывания сопрягаемый модуль и вьфабатывает сигнал занятости на линии 34 блока 18, который вырабатьшает в линии 44 сигнал Выдача вектора. Сопрягаемый модуль, получив сигнал Вьщача вектора по интерфейсу 3, выдает в линию 40 сигнал Готовность данных. Узел 72 вырабатывает сигнал прерывание, котося в два этапа: захват общей шины и управление обменом данных. Между соп рягаемым модулем и пассивньм модулем на общей шине. Захват общей шины про

5 исходит аналогично захвату общей щи- ны при выполнении режима вьщачи век - тора прерывания. После вьщачи сигнала Занятость в линию 55 происходит обмен управляющими сигналами для об 0 мена данными по общей щине. В работу включаются блок 18, генератор 15 и блок 16. При поступлении по линиям 74 и 33 блока 18 сигнала требования передачи и сигнала занятости узел 70

5 вырабатывает на линии 43 сигнал Выдача адреса , которьй поступает на интерфейс 3. Сопрягаемый модуль выда ет адрес на общую шину. Код управления на общей шине задается сопрягае20 мым модулем с помощью сигнала Код операции в линии 41.

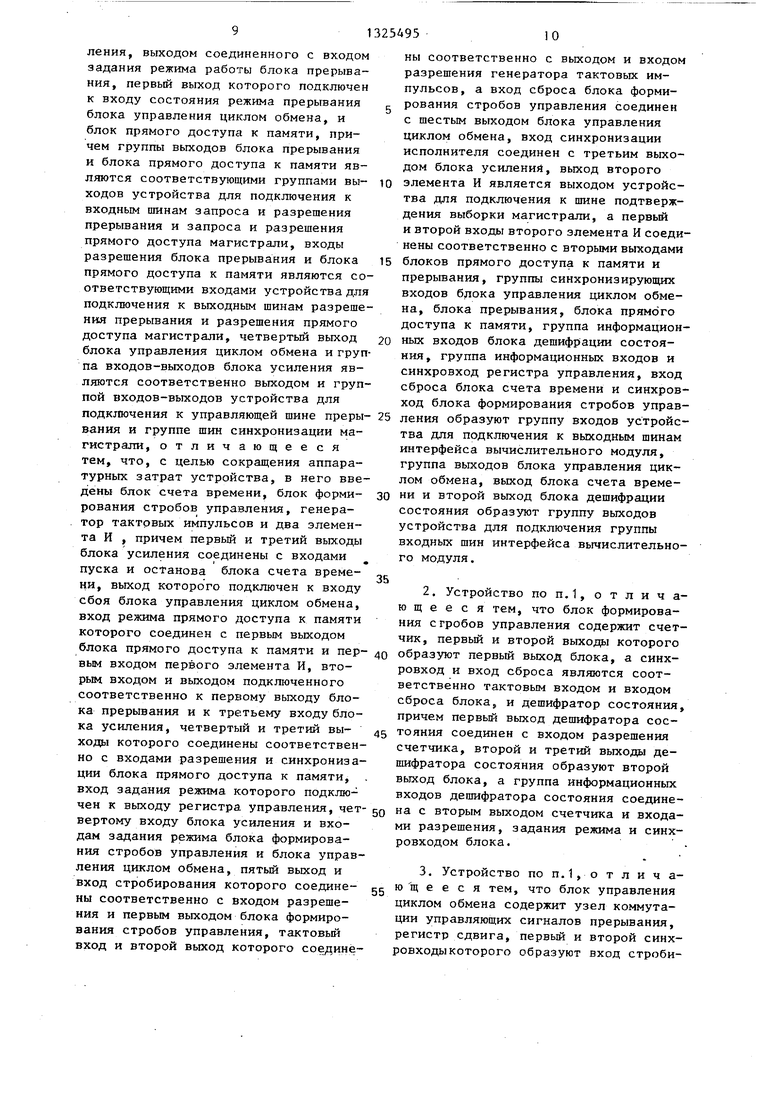

При выполнении операции Запись (фиг.8) по сигналу Вьщача адреса

25 узел 70 вырабатывает сигнал Вьщача данных, которьш поступает по линии 79 в сопрягаемый модуль, который получив этот сигнал вьщает данные на общую шину, а в линию 40 вьщает сиг30 нал Готовность данных. По сигналу в линии 40 дешифратор 140 формирует на линии 141 сигнал, разрешающий работу генератора 15. При поступлении тактовых импульсов счетчик 58 формирует на линиях 67 и 68 первый и второй стробы управления, которые поступают на входы синхронизации регистра 69. По заднему фронту второго строба управления (через 150 не) срабатывает триггер 81 и на выходе узла 70 в линии 46 вырабатывается сигнал Синхро низация задатчика, который поступает на общую шину. При установке триггера 81 на линии 142 дешифратор 140

35

40

рый подается в линию 19 интерфейса 8. 45 вырабатывает сигнал блокировки гене- В ответ по линии 14 из общей шины ратора 15. Генератор 15 блокируется

14

приходит сигнал Синхронизация исполнителя. Узел 72 сбрасьгоает сигналы Вьщача вектора и Прерьшание. Сброс сигнала Вьщача вектора в линии 44 приводит к сбросу триггера 129 блока 24, который устанавливает в исходное состояние регистр 130 и триггеры 126 и 127. При этом режим выдачи вектора прерьюания заканчивается .

Выполнение режима обмена данными по его запросу передачи осуществляетдо тех пор, пока на линии 14 не появится сигнал Синхронизация исполнителя. Срабатывает коммутатор 71,ко50 торый устанавливает триггер 82, снимая блокировку генератора 15. По следующему заднему фронту второго строба управления на линии 68 сбрасы- вается триггер 81 регистра 69. На вы55 ходе элемента И-НЕ 87 вырабатывается сигнал конца цикла, стробирующий триг гер 91, формирующий в 65 сигнал Конец цикла. Обмен массивом слов заканчивается приходом из сопся в два этапа: захват общей шины и управление обменом данных. Между сопрягаемым модулем и пассивньм модулем на общей шине. Захват общей шины происходит аналогично захвату общей щи- ны при выполнении режима вьщачи век - тора прерывания. После вьщачи сигнала Занятость в линию 55 происходит обмен управляющими сигналами для обмена данными по общей щине. В работу включаются блок 18, генератор 15 и блок 16. При поступлении по линиям 74 и 33 блока 18 сигнала требования передачи и сигнала занятости узел 70

вырабатывает на линии 43 сигнал Выдача адреса , которьй поступает на интерфейс 3. Сопрягаемый модуль выдает адрес на общую шину. Код управления на общей шине задается сопрягаемым модулем с помощью сигнала Код операции в линии 41.

При выполнении операции Запись (фиг.8) по сигналу Вьщача адреса

узел 70 вырабатывает сигнал Вьщача данных, которьш поступает по линии 79 в сопрягаемый модуль, который получив этот сигнал вьщает данные на общую шину, а в линию 40 вьщает сигнал Готовность данных. По сигналу в линии 40 дешифратор 140 формирует на линии 141 сигнал, разрешающий работу генератора 15. При поступлении тактовых импульсов счетчик 58 формирует на линиях 67 и 68 первый и второй стробы управления, которые поступают на входы синхронизации регистра 69. По заднему фронту второго строба управления (через 150 не) срабатывает триггер 81 и на выходе узла 70 в линии 46 вырабатывается сигнал Синхронизация задатчика, который поступает на общую шину. При установке триггера 81 на линии 142 дешифратор 140

14

до тех пор, пока на линии 14 не появится сигнал Синхронизация исполнителя. Срабатывает коммутатор 71,ко50 торый устанавливает триггер 82, снимая блокировку генератора 15. По следующему заднему фронту второго строба управления на линии 68 сбрасы- вается триггер 81 регистра 69. На вы55 ходе элемента И-НЕ 87 вырабатывается сигнал конца цикла, стробирующий триггер 91, формирующий в 65 сигнал Конец цикла. Обмен массивом слов заканчивается приходом из сопрягаемого модуля по линии 54 сигнала Последний цикл. По заднему фронту следующего строба сбрасывается триггер 91, снимая сигналы на линиях 43 и 79 и сбрасывая триггер 129, чем выводятся в исходное состояние регистр 130 и триггер 127,

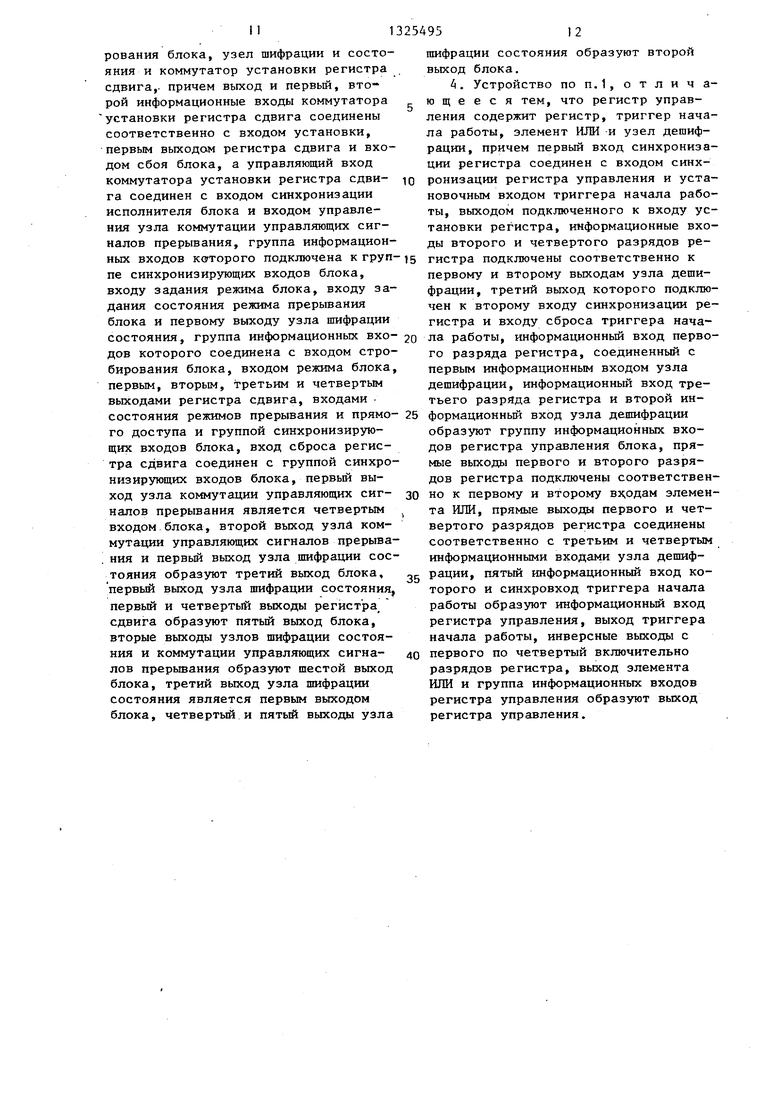

При выполнении операции Чтение (фиг.9) сигналом Вьщача адреса в линии 43 снимается блокировка с генератора 15 и на блок 16 поступают такты, записывающие счетчик 58. Через заданное время (150 не) по заднему фронту сигнала в линии 68 срабатывает триггер 81, формируя в линиях 46 и 66 сигналы Синхронизация задатчи- ка. Высокие уровни сигналов на линиях 66 и 139 приводят к блокировке генератора 15 до прихода из линии 14 сигнала Синхронизация исполнителя, по которому устанавливается триггер 82. Генератор 15 запускается и на линии 67 формируется первый строб. Через такт (75 не) по второму стробу (линия 68) для передачи сопрягаемому модулю на линии 78 формируется сигнал Прием данных, который через элемент ИЛИ 103 и на линию 96 поступает через интерфейс 3 в модуль. Сои- зо срабатывает сигнал в линии 32

рягаемьш модуль осуществляет прием данных в общей шины выдает в линию 40 сигнал Готовность данных. Этот сигнал снова разблокирует генератор 15 аналогично тому, как это., происходит при выполнении операции Запись. Через 75 не вырабатывается сигнал Конец цикла и происходит сброс сигналов Вьщача. адреса, Занятост . На этом выполнение операции Чтение заканчивается.

При превьшении регламента времени на приход по линии 14 сигнала Синхронизация исполнителя с общей щины от пассивного модуля срабатывает блок 1, вьщавая на интерфейс 3 сигнал сбоя по времени, которьм поступает также на блок 18. Таким образом, окончание

обмена происходит либо по приходу сиг- первому и второму выходам блока уси- нала Синхронизация исполнителя, ли- ления, первый и второй входы синхро- бо по сигналу сбоя с выхода блока 1. низации блока усиления соединены со- В ответ на сигнал сбоя сопрягаемый ответственно с первыми выходами бло- модуль посыпает по лини (45 сигнал ка дешифрации состояния и блока уп- Подготовка на блок 1, которьм пос- равления циклом обмена, второй и третий выходы которого соединены соответственно с третьим информационным входом блока дешифрации состояния и информационным входом регистра.управледний приводится в исходное состояние.

При наличии сигнала на линии 134 выполняется режим обмена данными по

запросу передачи с последующим прерыванием, при этом этапь захвата общей шины и обмена данными происходят аналогично описанному. Однако с приходом по линии 54 сигнала Последний цикл не 1роисходит сброса триггера 127, а происходит переход в режим выдачи вектора прерывания после обмена

О данными.

Выполнение режима прямого доступа к памяти происходит в два этапа: захват шины и обмен данными. На этапе захвата шины участвуют блоки 24 и 22.

5 С выхода регистра 130 на линии 75 при наличии сигналов на линиях 133 и 134 устанавливается сигнал запроса прямого доступа в блок 22, которьш формирует сигнал в линию 30 общей шины.

0 В ответ по линии 32 приходит сигнал Разрешение прямого доступа, запирающий одновибратор 107. По переднему фронту выходного импульса одновибра- тора 107 срабатывает триггер 114, по

5 заднему фронту срабатывает триггер 115, вырабатывающий сигнал Подтверждение выборки на линии 57, которым сбрасывается сигнал линии 30. На магистрали в ответ на сигнал в линии

35

40

на инверсном выходе триггера 116 устанавливается сигнал занятости, поступающий в общую шину по линии 33. В блоке 18 формируется сигнал Выдача адреса ( линия 43), и начинается этап обмена данными в описанных режимах Запись или Чтения. Появление сигнала Последний цикл в линии 54 от сопрягаемого модуля сбрасывает триггеры 91, 115, 116 и 129.

Формула изобретения

1. Устройство для сопряжения вы- g числительного модуля с магистралью, содержащее блок управления циклом обмена, блок дешифрации состояния, первый и второй информационные входы которого подключены соответственно к

ления, выходом соединенного с входам задания режима работы блока прерывания, первый выход которого подключен к входу состояния режима прерывания блока управления циклом обмена, и блок прямого доступа к памяти, причем группы выходов блока прерывания и блока прямого доступа к памяти являются соответствующими группами выходов устройства для подключения к входным шинам запроса и разрешения прерывания и запроса и разрешения прямого доступа магистрали, входы разрешения блока прерывания и блока прямого доступа к памяти являются соответствующими входами устройства для подключения к выходным шинам разрешения прерывания и разрешения прямого доступа магистрали, четвертый выход блока управления циклом обмена и группа входон-выходов блока усиления являются соответственно выходом и группой входов-выходов устройства для подктпочения к управляющей шине прерывании и группе шин синхронизации магистрали, отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены блок счета времени, блок формирования стробов управления, генератор тактрвых импульсов и два элемента И , причем первый и третий выходы блока усиления соединены с входами пуска и останова блока счета времени, выход которого подключен к входу сбоя блока управления циклом обмена, вход режима прямого доступа к памяти которого соединен с первым выходом блока прямого доступа к памяти и первым входом первого элемента И, вторым входом и выходом подключенного соответственно к первому выходу блока прерывания и к третьему входу блока усиления, четвертый и третий выходы которого соединены соответственно с входами разрешения и синхронизации блока прямого доступа к памяти, вход задания режима которого подключен к выходу регистра управления, четвертому входу блока усиления и входам задания режима блока формирования стробов управления и блока управления циклом обмена, пятый вькод и вход стробирования которого соединены соответственно с входом разрешения и первым выходом блока формирования стробов управления, тактовый вход и второй выход которого соединены соответственно с выходом и входом разрешения генератора тактовых импульсов , а вход сброса блока форми- рования стробов управления соединен с шестьм выходом блока управления циклом обмена, вход синхронизации исполнителя соединен с третьим выходом блока усилений, выход второго

элемента И является выходом устройства для подключения к шине подтверждения выборки магистрали, а первьй и второй входы второго элемента И соединены соответственно с вторыми выходами

блоков прямого доступа к памяти и прерывания, группы синхронизирующих входов блока управления циклом обмена, блока прерывания, блока прямо го доступа к памяти, группа информационных входов блока дешифрации состояния, группа информационных входов и синхровход регистра управления, вход сброса блока счета времени и синхровход блока формирования стробов управления образуют группу входов устройства для подключения к выходным шинам интерфейса вычислительного модуля, группа выходов блока управления циклом обмена, выход блока счета времени и второй выход блока дешифрации состояния образуют группу выходов устройства для подключения группы входных шин интерфейса вычислительного модуля.

2.Устройство по П.1, отличающееся тем, что блок формирования с гробов управления содержит счетчик, первый и второй выходы которого

образуют первый выход блока, а синхровход и вход сброса являются соответственно тактовым входом и входом сброса блока, и дешифратор состояния, причем первый выход дешифратора состояния соединен с входом разрешения счетчика, второй и третий выходы дешифратора состояния образуют второй выход блока, а группа информационных входов дешифратора состояния соединена с вторым выходом счетчика и входами разрешения, задания режима и синх- ровходом блока.

3.Устройство по П.1,о т л и ч а- ю щ е е с я тем, что блок управления

циклом обмена содержит узел коммутации управляющих сигналов прерывания, регистр сдвига, первый и второй синх- ровходыкоторого образуют вход строби10

рования блока, узел шифрации и состояния и коммутатор установки регистра сдвига,, причем выход и первый, второй информационные входы коммутатора

установки регистра сдвига соединены соответственно с входом установки, первым выходом регистра сдвига и входом сбоя блока, а управляющий вход коммутатора установки регистра сдвига соединен с входом синхронизации исполнителя блока и входом управления узла коммутации управляющих сигналов прерывания, группа информационных входов которого подключена кгруп- ц пе синхронизирующих входов блока, входу задания режима блока, входу задания состояния режима прерывания блока и первому выходу узла шифрации состояния, группа информационных вхо- 2о дов которого соединена с входом стро- бирования блока, входом режима блока, первым, вторым, третьим и четвертым выходами регистра сдвига, входами состояния режимов прерывания и прямо- 25 го доступа и группой синхронизирующих входов блока, вход сброса регистра сдвига соединен с группой синхронизирующих входов блока, первый выход узла коммутации управляющих сиг- зо налов прерывания является четвертым входом блока, второй выход узлй коммутации управляющих сигналов прерывания и первьм выход узла шифрации состояния образуют третий выход блока, первый выход узла шифрации состояния, первый и четвертый выходы регистра сдвига образуют пятый выход блока, вторые выходы узлов шифрации состояния и коммутации управляющих сигналов прерывания образуют щестой выход блока, третий выход узла шифрации состояния является первым выходом блока, четвертый и пятый выходы узла

35

40

0

ц о 5 о

5

0

шифрации состояния образуют второй выход блока.

, Устройство по п,1, о т л и ч а- ю щ е е с я тем, что регистр управления содержит регистр, триггер начала работы, элемент ИЛИ и узел дешифрации, причем первый вход синхронизации регистра соединен с входом синхронизации регистра управления и установочным входом триггера начала работы, выходом подключенного к входу установки регистра, информационные входы второго и четвертого разрядов регистра подключены соответственно к первому и второму выходам узла дешифрации, третий выход которого подключен к второму входу синхронизации регистра и входу сброса триггера начала работы, информационный вход первого разряда регистра, соединенный с первым информационным входом узла дешифрации, информационный вход третьего разряда регистра и второй информационный вход узла дешифрации образуют группу информационных входов регистра управления блока, прямые выходы первого и второго разрядов регистра подключены соответственно к первому и второму вх;одам элемента ИЛИ, прямые выхода первого и четвертого разрядов рег-истра соединены соответственно с третьим и четвертым информационными входами узла дешифрации, пятый информационный вход которого и синхровход триггера начала работы образуют информационный вход регистра управления, выход триггера начала работы, инверсные выходы с первого по четвертый включительно разрядов регистра, выход элемента ИЛИ и группа информационных входов регистра управления образуют выход регистра управления.

,69

.ТО

if.

47 ,

98 l9

18

S5

21

101

Ю)

96

-

97

4

79

35.

Риг.

Фиг. 5

Фиг.6

ФигЛ

OnOpJW

Vi/Jnt ffl/f ffg

ПВ6 JAM

Лт lrf««Mo pr-евя

I II

Я

СКН

МГ 7Ш1Г 1П{1Г7Ш1Г

Я«е1Г: (

А

,

Конец цикла

tocfltixm -ним «

ванны

е5

Составитель В.Вертлиб Редактор А.Ворович Техред Л.Сердюкова Корректор с.Черни

Заказ 3111/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

гг- е

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения магистрали приборного интерфейса с магистралью микро-ЭВМ | 1986 |

|

SU1368885A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения вычислительной машины с периферийными устройствами | 1981 |

|

SU960787A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения модулей, входящих в вычислительную систему магистрального типа общая шина. Целью изобретения является сокращение аппаратурных затрат устройства. Эта цель достигается тем, что в устройство, содержащее блок 18 управления циклом обмена, блок 24 регистра управления, блок 20 дешифрации состояния, блок 22 прямого доступа к памяти, блок 23 прерывания и блок усиления, введены блок 1 счета времени, блок 16 формирования стробов управления, генератор 15 тактовых импульсов и элементы И 26 и 27. 3 з.п. ф-лы, 9 ил. с S (Л Фиг.1

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 3730781, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1985-04-23—Подача