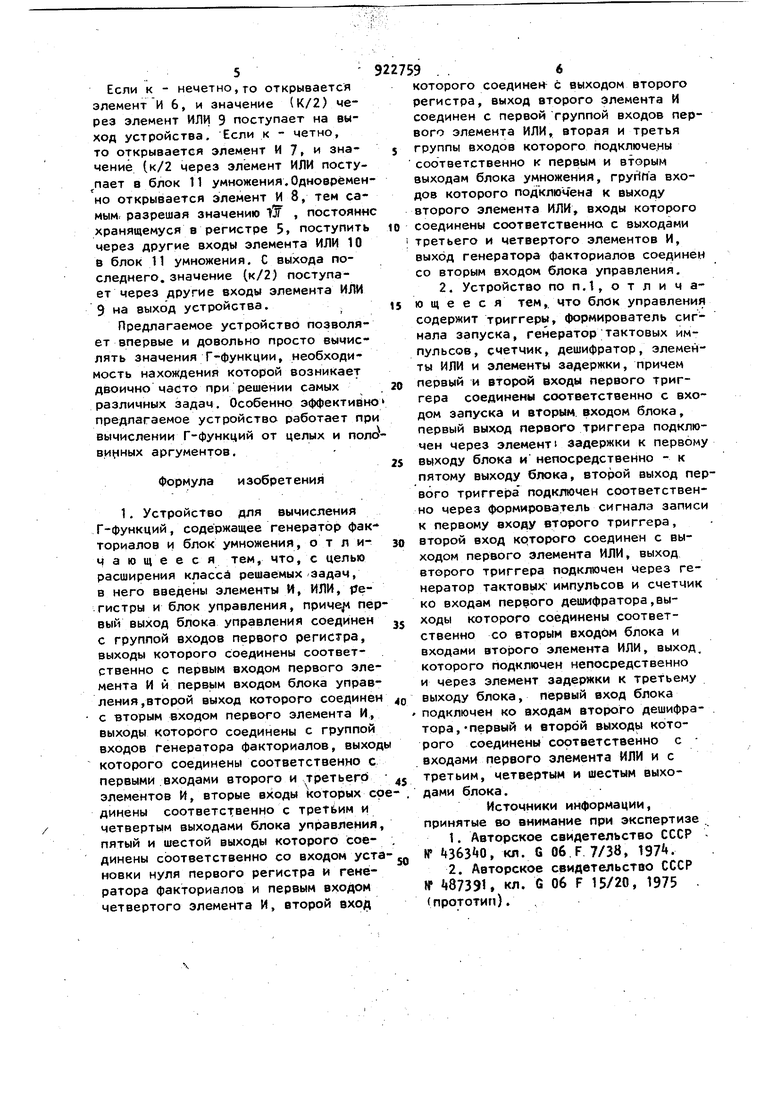

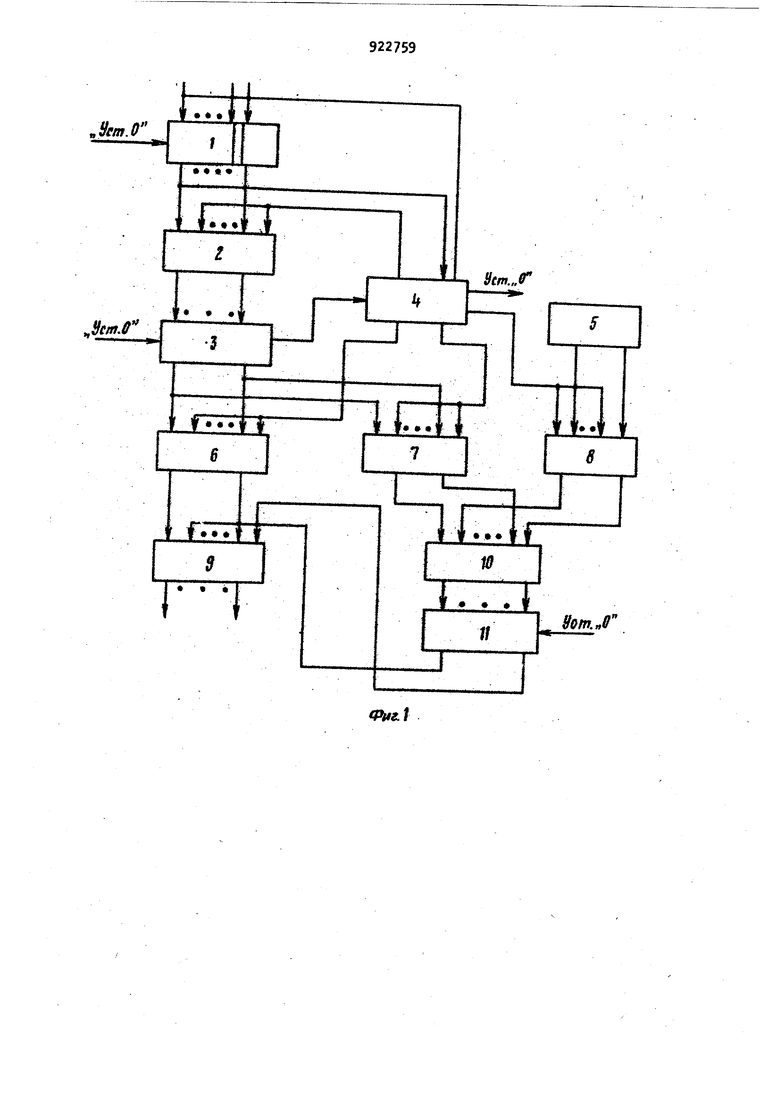

Изобретение относится к вычислительной технике и может найти больш применение при решении широкого кру задач, в которых необходимо произво дить вычисление Г-функций. Известно устройство, выдающее арифметические прогрессии с любой целой или дробной разностью. В част ности, такой прогрессией может быть возрастающий или убывающий ряд чисел с разностью, равной единице 1. Однако определение факториала из чисел этого ряда указанное устройство не производит. Наиболее близким к изобретению по достигаемому результату является устройство, содержащее блок степени полинома, генератор факториало блок умножения, блок уменьшения порядковых номеров коэффициентов, бло деления, блок коэффициентов полинома и блок кратности дифференцирования Г23. Однако круг задач, решаемых этим устройством, не предусматривает вычисление значений Г-функций. Цель изобретения - расширение класса решаемых задач, т.е. создание устройства, позволяющего вычислять значение Г-функций от целых и половинных аргументов. Поставленная цель достигается тем, что в устройство, содержащее генератор факториалов и блок умножения, введены элементы И, ИЛИ, регистры и блок управления, причем первый выход блока управления соединен с группой входов первого регистра, выходы которого соединены .соответственно с первым входом первого элемента И и первым входом блока управления, второй выход которого соединен с вторым входом первого элемента И, выходы которого соединены с группой входов генератора факториалов, выходы которого соединены соответственно с первыми входами второго vt третьего элементов И, вторые ходы которых соединены с ответственно с третьим и.четвертым выходами блока управления, пятый и шестой выходы которого соединены соответственно со входом установки нуля первого регистра и генератора факториалов и первым входом четвертого элемента И, второй вход которо го соединен с выходом второго регис ра, выход второго элемента И соедине с первой группой входов первого элемента. ИЛИ, вторая и третья группа вх дов которого подключены соответствен но к первым и вторым выходам блока умножения, группа входов которого подключена к выходу второго элемента ИЛИ, входы которого соединены соответственно с выходами третьего и чет вертого элементов И, выход генератор факториалов соединен со вторым входом блока управления. Кроме того,блок управления содержит триггеры, формирователь сигнала запуска, генератор тактовых импульсов, счетчик, дешифратор, элементы ИЛИ и элементы задержки, причем первый и второй входы первого триггера соединены соответственно с входом запуска и втopы i входом блока, первый выход первого триггера подключен через элемент задержки к первому входу блока и непосредственно к пятому входу блока, второй выход первого триггера подключен соответственно через формирователь сигнала записи к первому входу второго триггера, второй вход которого соединен с выходом первого элемента ИЛИ, вы- ход второго триггера подключен через генератор тактовых импульсов и счетчик ко входам первого дешифратора, выходы которого соединены соответственно со вторым входом блока и входами второго элемента ИЛИ, выход которого подключен непосредственно и через элемент задержки к третьему выходу блока, первый вход блока подключен ко входам второго дешифратора, первый и второй выходы которбго соединены соответственно с входами первого элемента ИЛИ и с третьим четвертым и шестым выходами блока. На фиг.1 приведена блок-схема устройства для вычисления г-функций нз фиг.2-- схема блока управления. Блок-схема содержит регистр 1 (числа К), элемент 2, генератор 3 факториалов, блок управления, регистр 5 (числа Vj ) , элементы И 6-8 элементы ИЛИ Э, Ю, блок 11 умножения. Блок k управления содержит триггер 1Д, формирователь 13 запуска, триггер 14, генератор 15 тактовых импульсов, счетчик 16, дешифратор 17и 18, элементы ИЛИ 19 и 20. Устройство работает следующим образом. По команде Пуск первый триггер 12 вырабатывает управляющий импульс, который приводит 8 нулевое состояние регистр 1, генератор 3 факториалов и блок 11 умножения. Этот же импульс после задержки.. разрешает подачу в регистр 1 числа к/2, записанного в двоичном коде. После записи в регистре 1 числа к/2, это значение передается на вход второго дешифратора 18и одновременно перебрасывает первый триггер в новое состояние, которое через формирователь 13 запуска и второй управляющий триггер 1 вырабатывает сигнал запуска генератора .тактовых импульсов 15. По первому тактовому импульсу, появившемуся на первой шине дешифратора 17, открывается элемент И 2 и значение K/2i в двоичном коде с регистра 1- поступает в генератор факториалов 3« По второму тактовому импульсу через элемент ИЛИ 20 производится вычитание единицы из целого числа к/2, записанного в регистр 1, а также после задержки опять открывается элемент И 2 и значение к/2-1 )поступает а генератор факториалов 3 для перемножения с предыдущим значением. Одновременно значение (k/2-l) подается на вход деифратора 18.По третьему и остальным тактовым импульсам производится операция, аналогичная операция при втором тактовом импульсе. Генератор 15 вырабатывает тактовые импульсы до тех пор, пока на входе дешифратора 18 не появится комбинация 00...1,0 ёсли к - четное)или 00...0,1 (если, к - нечетноеJ, В первом случае появляется сигнал -на первой шине дешифратора 18 и открывается элемент И 6, во втором случае по сигналу со второй шины указанного дешифратора открываются элементы И 7 и 8. В любом из этих двух случаев появляется сигнал на выходе элемента ИЛИ, перебрасывающий триггер 14 ,и прекращающий работу генератора 15 тактовых импульсов.

Если к - нечетно,то открывается элемент И 6, и значение 1К/2) через элемент ИЛИ 9 поступает на выход устройства. Если к - четно, то открывается элемент И 7, и значение (к/2 через элемент ИЛИ посту пает а блок 11 умножения.Одновременно открывается элемент И 8, тем самым, разрешая значению if , постоянно хранящемуся в регистре 5 поступить через другие входы элемента ИЛИ 10 в блок 11 умножения. С выхода последнего, значение (к/2) поступает через другие входы элемента ИЛИ 9 на выход устройства.

Предлагаемое устройство позволяет впервые и довольно просто вычис лять значения Г-функции, необходимость нахождения которой возникает двоично часто при решении самых различных задач. Особенно эффeктивнo предлагаемое устройство работает при вычислении Г-функций от целых и полс)ви(1ных аргументов. Формула изобретения

1. Устройство для вычисления Г-функций, содержащее генератор фак ториалов и блок умножения, о т л ич а юще е ся тем, что, с целью расширения классе решаемыхЗадач, в него введены элементы И, ИЛИ, (Jeгистры и блок управления, пpичe 4 первый выход блока управления соединен с группой входов первого регистра, выходы которого соединены соответственно с первым входом первого элемента И и первым входом блока управления,второй выход которого соединен с вторым входом первого элемента И, выходы которого соединены с группой входов генератора факториалов, выход которого соединены соответственно с первыми входами второго и третьего элементов И, вторые входы которых со динены соответственно с третьим и четвертым выходами блока управления, пятый и шестой выходы которого соединены соответственно со входом устамовки нуля первого регистра и генератора факториалов и первым входом четвертого элемента И, второй вход

которого соединен с выходом второго регистра, выход второго элемента И соединен с первой группой входов первого элемента ИЛИ, вторая и третья группы входов которого подключены соответственно к первым и вторым выходам блока умножения, rpyrifia входов которого подклюмена к выходу второго элемента ИЛИ, входы которого соединены соответственно с выходами третьего и четвертого элементов И, выход генератора факториалов соединен со вторым входом блока управления,

2. Устройство поп.1,отличаю щ е е с я тем, что блок управления содержит триггеры, формирователь сигнала запуска, генератор тактовых импульсов, счетчик, дешифратор, элементы ИЛИ и элементы задержки, причем первый и второй входы первого триггера соединены соответственно с входом запуска и вторым, входом блока, первый выход первого триггера подключен через элементi задержки к первому выходу блока и непосредственно - к пятому выходу блока, второй выход первого триггера подключен соответственно через формирователь сигнала записи к первому входу второго триггера, второй вход которого соединен с выходом первого элемента ИЛИ, выход второго триггера подключен через генератор тактовых импульсов и счетчик ко входам первого дешифратора,выходы которого соединены соответственно со вторым входом блока и входами второго элемента ИЛИ, выход которого подключен непосредственно и через элемент задержки к третьему выходу блока, первый вход блока подключен ко входам второго дешифратора, -первый и второй выходы которого соединены сортветственно с входами первого элемента ИЛИ и с третьим, четвертым и шестым выходами блока.

Источники информации, принятые во внимание при экспертизе .

1.Авторское свидетельство СССР tt363«0, кя. G Об.F 7/38, 197.

2.Авторское свидетельство СССР № 87391, кл. G Об F 15/20, 1975 . (прототип).

.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления @ -функций | 1983 |

|

SU1124321A1 |

| Вычислительное устройство | 1983 |

|

SU1120345A1 |

| Вычислительное устройство | 1983 |

|

SU1120344A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

Авторы

Даты

1982-04-23—Публикация

1979-02-27—Подача