1

Изобретение относится к аналоговой ; вычислительной технике и может быть использовано для поворота системы координат на плоскости.

Известно устройство, которое содержит два синусно-косинусных трансформатора - датчика слагаемых, операционные усшгатели, блоки памяти fll .

Данное устройство подвержено влиянию помех и чувствительно к изменению формы, фазы или крутизны входных сигналов, поскольку его работа основана на фиксации мгновенного значения синусоидального сигнала.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее двепары врашаю- шихся трансформаторов, коммутаторы, сервосистемы пля отработки рассогласо- . ваний, блоки коррекции и блоки- запоминания 2} .

Его недостаток - малое быстродействие, плохие массогабаритные характеристики, обусловленные наличием электромеханических элементов, и ограниченная точность, связанная с наличием моментных ошибок..

Цель изобретения - повышение быст родействия и точности.

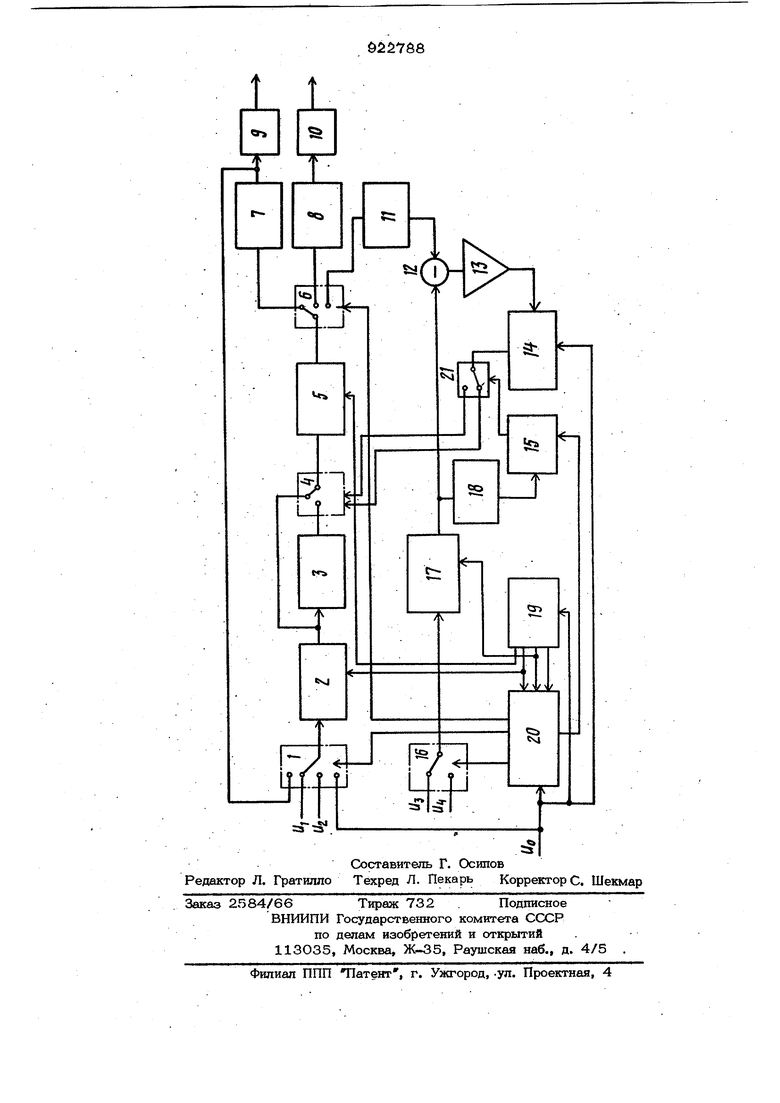

Цель достигается тем, что устройство для вычисления синуса и косинуса суммы двух углов, содержащее первый коммутатор, соответствующие входы которого соединены с шинами синусной и косинусной составляющих яервого угла и с шиной опорного напряжения, второй коммутатор, соответствующие входы которого соединены b шинами синусной и косинусной составляющих второго угла, третий коммутатор, выходы которого соединены с входами соответственно первого, второго и третьего элементов памяти, и элемент сравнения, первый вход которого соединен с выходом третьего элемента памяти, а выход - с входом усилителя, дополнительно содержит 1три интегратора, инвертор, широтно-импульсный модулятор, нуль-орган, распредепитель импульсов, формирователь импульсов, логический элемент эквивалентности, первый и второй двухпозиционные переключатели и первый и второй избирательные фильтры, пойключениь1е к выходам соответственно первого и второго элементов памяти, выход первого коммутатора соединен с входом первого интегратора, выход которого через инвер тор и непосредственно соединен с соот.ветстЕующими входами первого двухпозиционного переключателя, выход которого соединен с входом второго интегратора, выход второго коммутатора соединен с входом третьего интегратора, второго интегратора соединен с входом .третьего коммутатора, выход третье го интегратора соединен с вторым входом элемента сравнения, выход усилителя, соединен с информационным входом широтно-импульсного модулятора, выход которого через второй д хпозиционный переключатель соединен с первым и вторым управляющими входами первого двух позидионного переключателя, шина опорного напряжения соединена с входами синхронизации широтно-импульсного моду лятора, распределителя импульсов и формироватепяимпульсов, первый выход которого соединен с входом сброса первого интегратора и с первым входом распределителя импульсов, второй выход формирователя импульсов соединён с входом сброса второго интегратора, третий выход .формирователя импульсов соединен с входом сброса третьего .интегратора и с вторым входом распределителя импульсов четвертый выход формирователя импульсов соединен с третьим входом распред&лителя импульсов, первый, второй и трети выходы которого соединены с управляющими входами соответственно первого, второго и третьего коммутаторов, а четвертый выход - с,первым входом логического элемента эквивалентности, выход третьего интегратора через нуль-орган связан с вторым рходом логического элемента эквивалентности, выход которого соединен с управляющим входом второго дцухпозиционного переключателя, а также тем, что выход первого элемента памяти соединен с дополнительным входом первого Жоммутатора. На чертеже представлена схема устройства. . Устройство содержит коммутатор 1, интегратор 2, инвертор 3, двухпозиционный переключатель 4, интегратор 5, коммутатор 6, элементы памяти 7 и 8, избирательные фильтры 9 и 1О, элемент 11 памяти, элемент 12 сравнения, усилитель 13, широтно-импутшсный модулятор (ШИМ) 14, логический элемент эквивалентности 15, коммутатор 16, интегратор 17, нуль-орган 18, формирователь 19 импульсов, распределитель 20 импульсов, двухпозиционный переключатель 21, Устройство работает следующим образом. Преобразование производится за 6 тактов в течение шести полупериодов опорного напряжения OQ . Производится формирование двух периодических последовательностей из четырех входных сигналов ченных от синусно-косинусяых датчиков и опорного сигнала по закону: 1, 2, О, 2 - 1, О, 1 ... и 3, 3, 3, 4, 4, 4, 3,.., путем поочередного интегрирования текущих значений сигналов в момент}л времени, соответствующие экстремумам первой гармоники несущей частоты (и минимуму квадратурной помехи, а также четных гармоник) н запоминания интеграла на время между моментами интегрирова- ния. (aiaK -. возле порядкового номера сигнала обозначает интегрирование последиего). Время интегрирования определяется периодом импульсных- помех. Затем осуществляется формирование широтнсз-импульсного сигнала путем сравнения второй последовательности с опорным сигналом и периодическое интегрирование первой поспедовательности синхронно с широтно-импупьсным сигналом. После этого производится выборка и перезапомиЬание попарных произведений, содержащихся в результирующем сигнале, расположенных в периодической последовательности через ра.вные интервалы времени, и выделение переменных составляющих запомненных сигналов, представляю.щих результат вычисления. Распределитель 20 импульсов в определенной последовательности подключает к входам интеграторов 2 и 17 источники опорного и п емножаемых натфяжений на время импульсов фиксирования. Указанные моменты времени соответствуют максимуму первой гармоники несущей частоты сигнала и минимуму квадратурной помехи. По окончании импульса на выходе интегратора 2( 17) запоминается напряжение, пропорциональное амплитуде первой гармоники входного сигнала, свободное от помех, так как интеграл от квадратуры высших четных гармоник и импульсных помех за время импульса

фиксирования paieeH нулю. Перед следующим импульсом фиксирования интеграторы обнуляются, а затем операция повторяется с сигнйлом следующего источника. П ерьвое и второе умножаемые напряжения от датчика первого угла U -| и UQ чередуются с опорным напряжением UQ на выходе интегратора 2 по закону 12О 2-1-01 и т.д

В течение пятого и шестого тактов с выхода распределителя 2О импульсов на вход элемента 15 эквивалентности поступает импульс, который в совокупности с сигналом нуль-органа 18 определяет положение переключателя 21, через который коммутирующий сигнал с выхода ШИМ 14 поступает на управляющий ЕЖОД переключателя 4. Тем самым определяется правильный знак сигнала, поступающего на интегратор 5. На время действи сигнала с выхода распределителя 20 импульсов положение переключателя 4 изменяется.

Третье и четвертое умножаемые напряжения ( Ua и и ) интегрируются и запоминаютсй интегратором 17. При

этом частота юс чередования в три раза ниже частоты опорного напряжения.

На выходе. интегратора 5 формируется сигнал, величина которого в течение каждого такта прямо пропорциональна произведению длительности управляющих импульсов на амплитуду входного напряжения. При этом знак фиксируемого напряжения определяется фазами шш полярностями Еходных сигналов. Перед началом каждого нового широтно-модулированного импульса интегратор 5 обнуляется. Таким образом производится поочередное пере1лножение кходных нат ряжёний: и.; ; UQ и Uo,;

U. и ; Up и UQ.В моменты времени, когда сигнал на вьЕходе интегратора 5 содержит в произведении опорное напряжение Ug, он фиксируется элементом памяти 11 и в ввде отрицательной обратной связи подается на вход усилителя 13. Таким образом создается замкнутый контур регулирования, что обеспечивает точность преобразования, так как нелинейности характеристик блоков преобразователя остаются скомпенсированными.

Каждый из двух элементов памяти 7 и 8 поочередно фиксирует напряжение, пропорциональное произведению то одной, то другой пары перемножаемых сигналов.

На выходе второго запоминающего элемента 7 будут фиксироваться поочередно, через равные интервалы времени напряжения U;ig,,lCU, « вых - i Соответственно не выходе запоминающего элемента 8 будут фиксироваться напряжения г (i И iuyy-l j J

На выходе и ирательных фильтров 9 и 10, выделяющих переменную составляю щую сигнала, будут действовать выходны напряжения переменного тока, амплитуды которых равны сооттветственно

vJ.,..i-l}J -V 4- b

AUWX0.

)к

и.

О.

Указаш ые формулы соответствуют формулам преобразования координат или вычисления синуса и косинуса суммы двух углов.

При этом частота выходного сигнала будет в три раза менвще частоты опорного напряжения. Устройство одинаково Щ)игодно для перемножения входных напряжении как постоянного, так и переменНО1-О тока, имеющих в общем случае разную форму, частоту и фазу. - Если сигнал с выхода одного из элементов памяти 7 и 8 подается на дополнительный вход первого или второго переключателя, то при соответствующем временном тактовом распределении импульсов обнуления и фиксирования происхдит повторное умножение запомненного сигнала на другие.

Таким образом можно получить произведение трех и более сомножителей, а введя дополнительные элементы памяти, возведение указанных сомножителей в П -ю степень.

Технико-экономический эффект от-использования изобретения определяется улучшением метрологических и массогабаритных характерист.ик и возможностью расщирения функциональных возможностей

Формула йзобрете н.и я

1. Устройство для вычисления синуса и косинуса суммы двух углов, содержащее первый коммутатор, соответствующие входы которого соединены с щинами си- нусной и косинусной составляющих первого угла и с щиной опорного напряжения, второй коммутатор, соответствующие входы которого соединены с шинами синусной и косинусной составл5пощих второго угла, третий коммутатор, выходы которого соединены с входами соответственно первого, второго и третьего элементов памяти и элемент сравнения, первый вход,которого соединен с выходом третьего элемента Памяти, а выход - с входом усилителя, отличающееся тем, что, с целью повышения быстродействия и точности, устройство дополнительно содержит три интегратора, инвертор, широтно-импульсный модулятор, нуль-орган, распределитель импульсов, формирователь импульсов, логический элемент эквивалентности, первый и второй двухпозиционные переключатели и первый и второй избирательные фильтры, подключенные к выходам соотвётствешю первого и второго элементов памяти, выход первого ком- , мутатора соедвйен с входом первого интеграторе, выход которого через инвертор и непосредственно соединен с соответствукяцимн входами первого двухпозиционного переключателя, выход которого соединен с входом второго интегратора, выход второго коммутатора соединен с входом третьего интегратора, выход второго интег а гора соединен с входом третьего коммутатора, выход третьего интегратора соедннея с вторым входом элемеш а сравн енвя, выход усилителя соединен с Ш1форма1|и()няым входом широтно- импульсного модулятора, выход которого через ет-орой дзЕ гэЬюзидибнный переключатель соединен с первым и вторым управляющими входами первого двухпозидионного переключателя, шина опорного напряжения соединена с входами синхронизации

широтно-импульсного модулятора, распределителя импульсов и формирователя импульсов, первый выход которого соединен с входом сброса первого интегратора и с первым входом распределителя импульсов, второй выход формирователя импульсов соединен с входом сброса второго интегратора, третий выход формирователя импульсов соединен с входом сброса третьего интегратора и с вторым входом распределителя импутшсов, четвертый выход формирователя импульсов соединен с третьим входом распределителя импульсов, первый, второй и третий выходы которого соединены с управляющими входами соответственно первого, второго и третьего коммутаторов, а четвертый выход - с первым входом логического элемента эквивалентности, выход третьего интегратора через нульорган Связан с вторым входом логического элемента эквивалентности, а11ход которого соединен с управляющим входом второго двухпозидионного переключателя. 2. Устройство по п. 1, отличаю щ е « ей тем, что, с делью расширения класса решаемых задач, выход первого элемента памяти соединен с дополнительным входом первого коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 374620, кл. SOeOi 7/22, 1971.

2.Авторское свидетельство СССР Ms 436364, кл. G06G 7/22, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU769637A1 |

| Вентильный электродвигатель | 1989 |

|

SU1767638A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1654973A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Вентильный электропривод | 1990 |

|

SU1767688A1 |

| Компенсационный измеритель разности фаз | 1979 |

|

SU855527A1 |

| ПОЛИМАГНИТНЫЙ ТЕРАПЕВТИЧЕСКИЙ АППАРАТ | 1992 |

|

RU2007198C1 |

| Способ управления трехфазным мостовым инвертором,работающим на двигатель переменного тока,и устройство для его осуществления | 1984 |

|

SU1270850A1 |

| Устройство для измерения скорости и направления течения | 1987 |

|

SU1520451A1 |

| АВТОМАТИЗИРОВАННОЕ ЗАРЯДНОЕ УСТРОЙСТВО | 1999 |

|

RU2159492C1 |

Авторы

Даты

1982-04-23—Публикация

1980-01-04—Подача