(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1120315A1 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| Генератор случайных последовательностей | 1983 |

|

SU1180887A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство для сравнения чисел | 1985 |

|

SU1260944A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Генератор псевдослучайных чисел | 1983 |

|

SU1185582A1 |

| Устройство для экстремальной фильтрации | 1987 |

|

SU1413621A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах электронных вычислительных машин.

Известно вычислительное устройство, содержащее блоки алалиэа единиц и нулей, блок равнозначности, триггеры запрета анализа единиц и ну-. лей, группы элементов И, формирующие разности по несовпадению и по равенству, группы элементов ИЛИ, элементы И, ИЛИ, инверторы, триггер 1 .

Однако известное устройство характеризуется большим объемом обог рудования и невысоким быстродей.- ствием.

Наиболее близким к предлагаемому является устройство для определения разности двух чисел, содержащее генератор импульсов, соединенный с первым входом первого элемента И, второй вход которого подключен к нулевому выходу RS-триггера, R - вход, последнего соединен с шиной записи второго числа, первый и второй счетчики,установочные входы которых соединены соответственно с шинами записи первого и второго, числа, второй элемент И, элемент или, счетный триггер, нулевой вход которого соединен с инверсным выходом RS-триггера, а счетный вход с выходом элемента ИЛИ- входы которого соединены соответственно с выходами первого и второго счетчиков, причем прямой выход счетноготриггера соединен с S-входом Н8 триггера и с первым входом второго элемен10та И, второй вход которого подключен к генератору импульсов, а выход - к выходной шине устройства, выход первого элемента И соединен со счетными входами счетчиков 2.

15

Цель изобретения - расширение функциональных возможностей устройства, заключающееся в возможностн одновременного определения устройством как разности так и суммы двух

20 двоичных чисел.

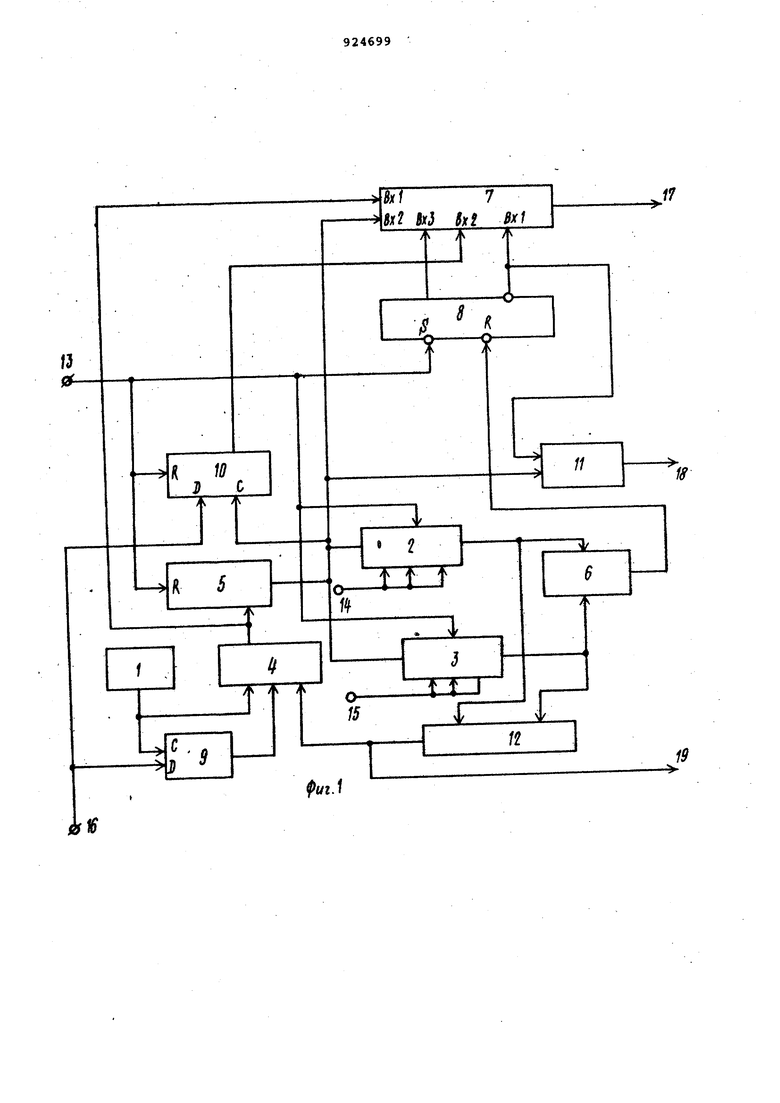

Поставленная цель достигается тем, что вычислительное устройство, содержащее генератор импульсов, два элемента И, два счетчика, RS-триггер

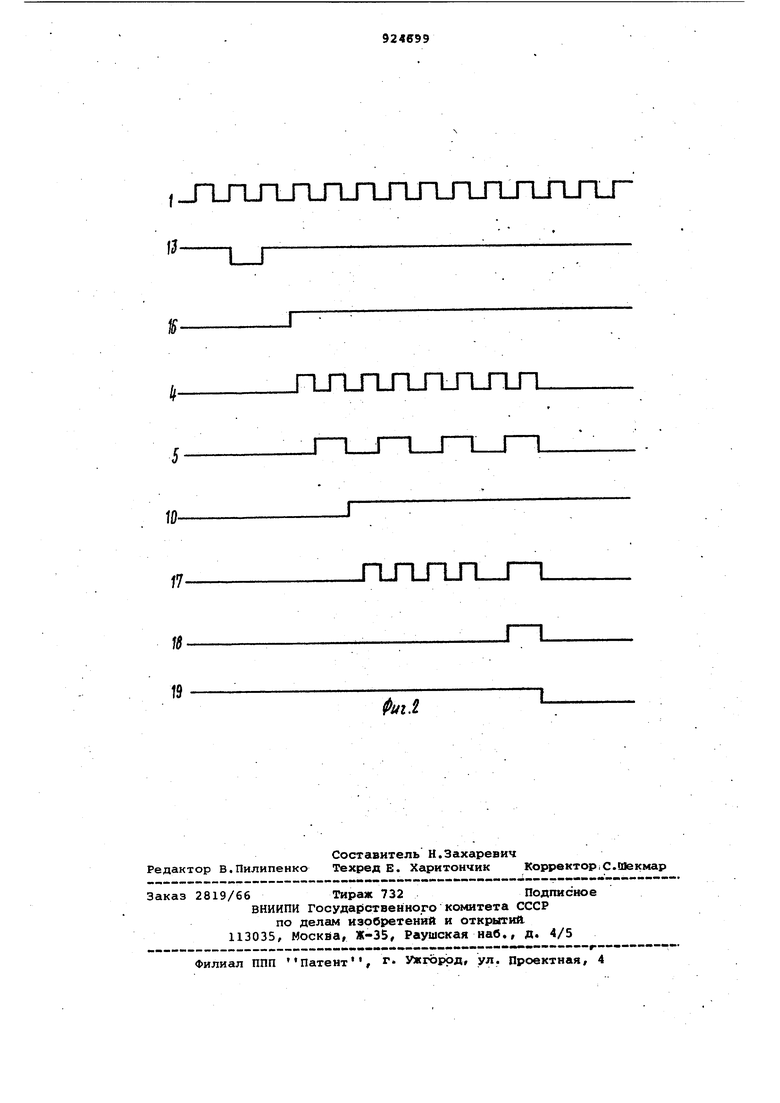

25 и счетный триггер, причем выход генератора импульсов соединен с первым входом первого элемента И, установочные входы первого и второго счетчиков соединены с шинами запи30си первого и второго числа устрой-. ства соответственно, выход второго элемента И подключен к выходу разности устройства, содержит элементы ИЛИ-НЕ, И-НБ, коммутатор, первый и второй D-триггеры, 0 -входы которы соединены с шиной задания режима устройства, синхровход первого D-триггера соединен с выходом генератора импульсов, а выход с вторым входом первого элемента и, третий вход которого соединен с выходом элемелта И-НЕ, а выход - со счетным входом счетного триггера и первым информационным входом коммутато ра, второй информационный вход которого соединен с выходом счетного триггера, синхровходом второго D-триггера, счетными входами первог и второго счетчиков и первым входом второго элемента И, второй вход коtoporo соединен с инверсным выходом RS-триггёра и первым управляющим входом коммутатора, второй управляю щий вход которого соединен с выходом второго D-триггера, а третий уп равляющий вход коммутатора соединен с прямым выходом RS-триггера, S вход которого соединен со входной шиной начальной установки и входами начальной установки второго D-триггера, счетного триггера, первого и второго счетчиков, выход пер вого счетчика соединен с первыми входами элементов И-НЕ и ИЛИ-НЕ, выход второго счетчика соединен со вторыми входами элементов И-НЕ и ИЛИ-НЕ, ВЫХОД элемента ИЛИ-НБ соединен с R-входом RS-триггера, выход, второго элемента И соединен с выходом разности устройства, выход коммутатора подключен к выходу суммы устройства. На фиг.1 изображена функциональная схема вычислительного устройства f на фиг.2 - временная диаграмма работы устройства. В состав устройства входит генератор 1 импульсов, первый счетчик 2 второй счетчик 3, первый элемент И 4, счетный триггер 5, элемент ИЛИ-Н 6, коммутатор 7 RS-триггер 8, первый D-триггер 9, второй D-триггер l второй элемент И 11, элемент И-НЕ 12, входная шина начальной установки 13, Зина 14 записи первого числа, шина 15 записи второго числа, шина 16 задания режима, выход суммы 17, выход разности 18, выходная управляющая шина 19. Устройство работает следующим об разом. На шину 13 подаётся импульс нача льной установки отрицательной поляр ности, который производит установку RS-триггера 8 в 1, а второго D-триггера 10, счетного триггера 5, счетчиков 2 и 3 - в нуль. Выход второго D-триггера 10 запрещает прохождение импульсов через коммутатор 7. На шины 14 и 15 записи поступают соответственно инверсные значения первого и второго числа, которые записываются в соответствую(аие .счетчики (кроме старших разрядов, на которых формируется перенос). Сигнал Работа подается на шину 16. Счетные импульсы с выхода генератора импульсов поступают на С-вход первого D-триггера 9 и по положительному фронту записывают в него информацию, находящуюся на D-входе,. в данном случае , которая разрешает прохождение счетных импульсов через элемент И 4. Счетные импульсы с выхода логического элемента И 4 поступают на первый информационный вход коммутатора 7 и на счетный вход счетного триггера 5, на котором по отрицательному фронту происходит деление частоты на 2. Импульсы с выхода счетного триггера 5 поступают на счетные входы счетчиков 2 и 3 (которые работают по отрицательному -фронту), на второй информационный вход коммутатора 7, на второй вход элемента И 11 и на С-вход второго D-триггера 10. По отрицательному фронту во второй D-триггер 10 записывается логическая единица (при наличии сигнала Работа), которая поступает на вторрй управляющий вход коммутатора 7 и разрешает прохождение через него импульсов с первого входа. После того, как один из счетчиков переполнился, на выходе элемента ИЛИ-НЕ б появляется сигнеш логического нуля, который поступает на ft-вход RS-триггера, последний устанавливается в положение,разрешающее прохождение импульсов через и ii и переключает коммутатор 7 в положение , при котором на его выход поступают .импульсы с выхода счетного риггера 5. Переполнение следующего счетчика приводит к тому, что на входе элемента И-НЕ 12 появляется сигнал Конец работы (выходная правляющая шина 19), запрещающий прохождение счетных импульсов чеез элемент И 4. Таким образом, на выходе элемента И 11 (на выходе разности 18) возникают импульсы, количество кото«7 рых равно разности двух чисел, в том счётчике(Который переполнился раньше (это соответствует тому, что в нем записано меньшее число) записывается параллельный код разности двух чисел, а на выходе коммутатора 7 (на выходе суммы 17) возникают импульсы, количество которых равно сумме двух чисел.

Если считать, что счетчик 2 счетчик уменьшаемого, а счетчик 3 счетчик вычитаемого, то разность будет положительной тогда, когда первым переполнился счетчик 3. Если первьм переполнился счетчик 2 уменьшаемого, то разность чисел в параллельном ходе записывается в счетчике 2 уменьшаемого и это соответствует отрицательной разности.

Если сравниваеАше числа оказываются равными, то сигналы переполнения с выходов счетчиков 2 и 3 устанавливаются по одному и тому же счетному импульсу. В этом случае на выходе элемента И-НЕ 12 появля ется-сигнёш, запрещающий прохождение импульсов через элемент И 4.

На фиг.2 приведена временная диаграмма работы устройства для случая, когда первое число равно 3, а второе 2.

Применение предлагаемого устройства позволяет упростить работу устройства при равенстве двух чисел, расширить его функциональные возможности за счет возможности одновременного определения сумма и разности одним устройством.

Формула изобретения

Вычислительное устройство, содержащее генератор импульсов, два элемента И, два счетчика, 1W -триггер и счетный триггер, причем выход генератора импульсов соединен с nepsiM входом первого элемента И установочные входы первого и второго счетчиков соединены с шинами записи первого и второго числа устройства соответственно, выход второго элемента И подключен к выходу разности устройства, отличаиввее с я тем, что, с целью расширения функциональных возможностей за счет одновременного получения суммы и

разности двух двоичных чисел,оно содержит элементы :ЙЛИ-НЕ, И-НЕ, коммутатор, первый и второй D-триг геры, D-входы которых соединены с шиной задания режима устройства, .

синхровход первого D-триггера сое- динен с выходом генератора импульсов, авыход - с вторым входом первого элемента И, третий вход которого соединен с выходом элемента ИНЕ, а выход - со счетньм входом счетного триггера и первым информациониш4.входом, коммутатора, второй информационный вход которого соединен с выходом счетного триггера, синхровходом второго D-триггера, счетныю входами первого и второго счетчиков и первым входом второго элемента и второй вход которого соединен с инверсным выходом

RS-триггера и первьв управляющим

входом коммутатора, второй управляющий вход которого соединен с выходом второго D-триггера, а третий управляющий вход коммутатора соединен с прямым выходом RS-триггера, S-вход которого соединен с входной шиной начальной установки и входами начальной установки второго D-триггера, счетного триггера, первого и второго счетчиков, выход первого счетчика соединен с первкши входами элементов И-НЕ и ИЛИ-НЕ, выход второго счетчика соединен с вторыми входами элементов И-НЕ и ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с

к-вход 4 НЗ триггера, выход второго элемента И соединен с выходом разности устройства, выход коммутатора подключен к выходу суммы устройства .

ИСТОЧНИКИ информации, принятые во внимание при экспертизе

1,Авторское свидетельство CCCf 408306, кл..G 06 F 7/385, 1973.

2,Авторское свидетельство СССР 434410, кл. G 06 F 7/385, 1974.

JlJlJ JTJljriJlJlJTJ

ЛJnJПLЛJTJTJlJT

f719

rLJlJTTLJTT

m.2

Авторы

Даты

1982-04-30—Публикация

1980-09-08—Подача