1120

D-TpHrrepa, третий вход пятого элемента Н соединен с тактовыми входами третьего и четвертого j)-триггеров и с прямым выходом счетного триггера, четвертый вход пятого элемента И - с прямым выходом R5-триггера, информационный вход четвертого D -триггера с прямым- выходом третьего 3) -триггера, инверсный выход которого соединен со своим информационным входом, второй вход четвертого элемента И соединен с инверсным выходом четвертого D-триггера, выход четвертого элемента И соединен с входом сброса третьего D-триггера, выход элемента ИЛИ соединен с выходом корня квадратного из суммы квадратов двух чисел устройства, выход э;7емента И-НЕ является выходом конца вычислений устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1985 |

|

SU1280614A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1242936A1 |

| Вычислительное устройство | 1984 |

|

SU1242938A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для вычисления разности квадратов двух чисел | 1990 |

|

SU1727121A1 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1990 |

|

SU1781642A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Устройство для вычисления квадрата и квадратного корня | 1983 |

|

SU1120320A1 |

| Цифровой фазометр | 1989 |

|

SU1707566A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее генератор импульсов, два элемента И, два счетчика, два D -триггера, R5 -триггер, счетный триггер, коммутатор, элемент ИЛИ-НЕ и элемент И-НЕ, причем выход генератора импульсов соединён с первым входом первого элемента И, разрядные входы первого и второго счетчиков соединены с входами первого и второго операндов соответственно, выход второго элемента И является выходом разности устройства, информационные входы первого и второго D -триггеров соедине- , ны с входом пуска устройства, тактовый вход первого D -триггера соединен с выходом генератора импульсов, выход первого Б -триггера - с вторвш входом первого элемента И, третий вход которого соединен с вьЬсодом элемента И-НЕ, выход первого элемента И соединен со счетным входом счетного триггера и первым информационным входом коммутатора, второй информационный вход которого соединен с выходом счетного триггера, тактовым входом второго D-триггера, счетными входами первого иВторого счетчиков и первым входом второго элемента И, второй вход которого соединен с инверсным выходом R5-триггераИ первым управляюпр м входом коммутатора, второй управляющий вход которого соединен с выходом второго D-триггера, а третий управляющий вход коммутатора соединен с прямым выходом R5 -триггера, вход установки которого соединен с входом начальной установки устройства и входа-ми сброса второго D -триггера, счетноге триггера, первого и второго счетчиков, выход переполнения первого счетчика соединен с первыми входами элементов И-НЕ и ИЛИ-НЕ, выход переполнения второго счетчика соединен с вторыми входами элементов И-НЕ и { ИЛИ-НЕ,. выход элемента ИЛИ-НЕ - с вхо-. СП дом сброса RS-триггера, выход коммутатора является выходом суммы устройства, отличающее с. я тем, что, с целью расширения области 2 применения путем получения возможности вычислять корень квадратный из суммы квадратов двух чисел, в него введены третий и четвертый D -триггеры, третий, четвертый и пятый элементы И и элемент ИШ1, причем первый вход третьего элемента И соединен с первым входом пятого элемента И и выходом первого элемента И, второй вход третьего элемента И соединен с инверсным выходом счетного триггера, третий вход третьего элемента И - с первым входом четвертого элемента И, входом, сброса четвертого D -триггера и выходом второго D -триггера, выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен с прямым выходом четвертого

1

Изобретение относится к вычислит1ельной технике и может быть использовано в измерительно-информационных системах в качестве устройства обработки информации.

Известно вычислительное устройство, содержащее блок анализа единицы и нулей, блок равнозначности, триггеры запрета анализа единиц и нулей, группы элементов И, формирующие разности по несовпадению и по равенству, группы элементов ИЛИ, элементы H ИЛИ, инверторы и триггер 1.

Однако данное устройство характеризуется большим объемом оборудования, невысоким быстродействием и ограниченными функциональными возможностями.

Наиболее близким к предлагаемому является вычислительное устройство, содержащее генератор импульсов, два счетчика, два Б-триггера, коммутатор, RS-триггер, счетный триггер, два элемента И, элемент ИЛИ, эле№нт И-НЕ и элемент ИЛИ-НЕ .21.

Однако для известного устройства характерны недостаточные функциональные возможности, не позволяющие производить одновременно с вычислением суммы и разности двух чисел вычисление квадратного корня из квад- ратой двух чисел.

Цель изобретения г расширение области применения путем получения возможности вычислять корень квадратный из суммы квадратов двух чисел одновременно с вычислением разности и суммы этих чисел.

Поставленная цель достигается тем, что вычислительное устройство, содержащее генератор импульсов, два

элемента И, два счетчика, дваD -триггерй, R5 -триггер, счетньм триггер, коммутатор, элемент ИЛИ-НЕ и элемент И-НЕ, причем выход генератора ИМПУЛЬСОВ соединен с первым входом первого элемента И, разрядные входы первого и второго счетчиков соединены с входами первого и второго операндов соответственно, выход второго элемента И является выходом разности устройства, информационные входы первого и второго Б-триггеров соединены с входом пуска устройства, тактовый вход первого D -триггера соединен с выходом генератора импульсов, выход первого J) -триггера - с вторым входом перрого элемента И, третий вход которого соединен с. выходом элемента И-НЕ, выход первого элемента И соединен со счетным входом счетного триггера и первым информационным входом коммутатора, второй информационный вход которого соединен с выходом счетного триггера, тактовым вхо-. дом второго D-триггера, счетными входами первого и второго счетчиков и первым входом второго элемента -И, второй вход которого соединен с инверсным выходом R5 -триггера и первым управляюЕцим входом коммутатора, второй управляющий вход которого соединен с выходом второго D -триггера, а третий управляющий вход коммутатора соединен с прямым выходом Р5-триггера, вход установки которого соединен с входом начальной установки устройства и входами сброса второго D триггера, счетного триггера, первого и второго счетчиков, выход переполнения первого счетчика соединен с первыми входами элементов И-НЕ и

ИЛИ-НЕ, выход переполнения второго счетчика соединен с вторыми входами элементов Н-НЕ и ИЛИ-НЕ, выход элемента ИЛИ-НЕ - с входом сброса R5триггера, выход коммутатора является выходом суммы устройства, дополни- тёльно содержит третий и четвертый D-триггеры, третий, четвертый и пятый элементы И и элемент ИЛИ, причем первый вход третьего элемента И соединен с первым входом пятого элемента И и выходом первого элемента И, второй вход третьего элемента И соединен с инверсным выходом счетного триггера, третий вход третьего элемента И - с . первым входом четвертого элемента И, входом сброса четвертого D -триггера и выходом второго D -триггера, выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен с прямым выходом четвертого 3)-триггера, третий вход пятого элемента И соединен с тактовыми входами третьего и четвертого J-триггеров и с прямым выходом счетного триггера, четвертьш вход пятого элемента И с прямым выходом R5-триггера, информационный вход четвертого D -триггера - с прямым выходом третьего 3) триггера, инверсный выход которого соединен со своим информационным входом, второй .вход четвертого элемента И соединен с инверсным выходом четвертого J) -триггера, выход четвертого элемента И соединен с входом с броса третьего Т)-триггера, выход элемента ШШ соединен с выходом корня квадратного из.суммы квадратов двух чисел устройства, выход элемента И-НЕ является выходом конца вычислений устройства.

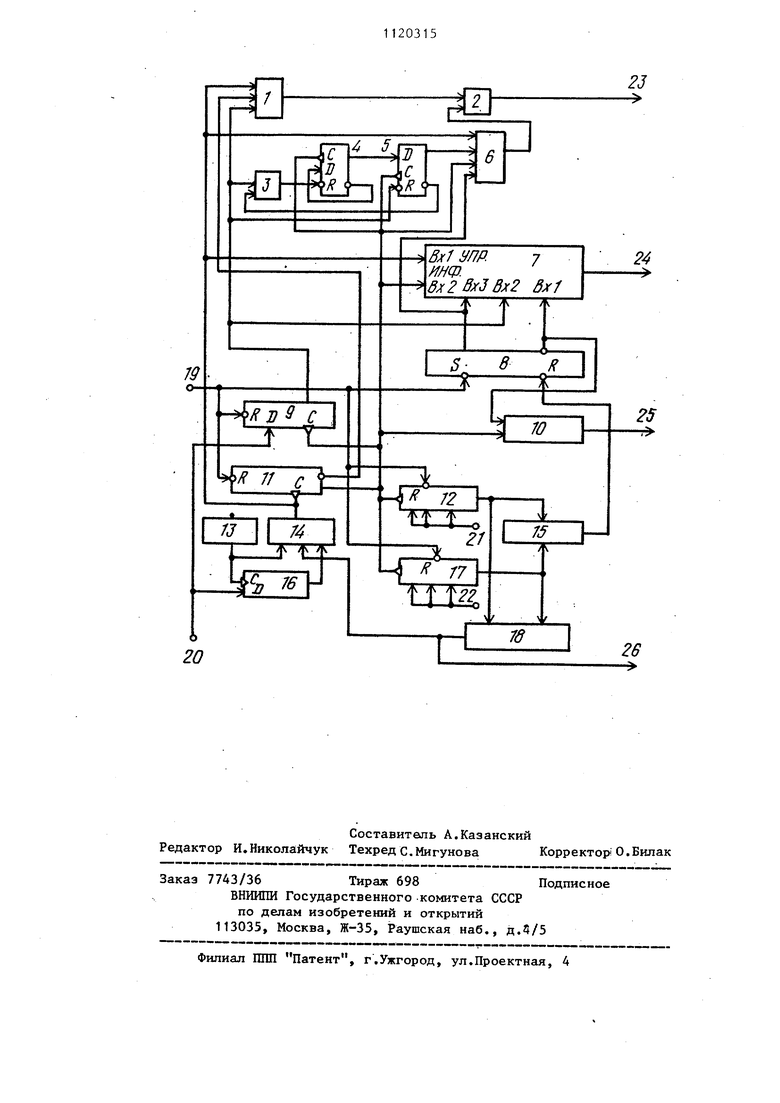

На чертеже изображена функциональная схема вычислительного устройства

Устройство содержит элемент И 1, элемент ИЛИ 2, элемент И 3, D -триггеры 4 и 5, элемент И 6, коммутатор 7, R5 -триггер 8, D -триггер 9, элемент -И 10, счетный триггер 11, счетчик 12, генератор 13 импульсов, элемент И 14, элемент ИЛИ-НЕ 15, D-триггер 16, счетчик 17,элемент И-НЕ 18, вход 19 начальной установки, вход 20 пуска устройства, вход 21 первого числа, вход 22 второго числа выход 23 корня квадратного из суммы квадратов, выход 24 суммы, выход 25 разности и выход 26 конца вычислений

154

Вычисление квадратного корня из суммы квадратов в устройстве основано на использовании аглоритма приближенного вычисления (алгоритм дает максимальную относительную погрешность вычисления около 6%).

Устройство работает следующим образом.

На вход 19 начальной установки поступает импульс начальной установки, которьш устанавливает RS -триггер 8 в 1, а триггеры 9, 11 и счетчики 12, 17 - в О, Логический О на выходе D -триггера 9 устанавливает D-триггер 5 и через элемент И 3 3)-триггер 4 в О. В исходном состоянии в D-триггер 16 записан О, который запрещает прохождение счетных импульсов через элемент И 14. На входы 21 и 22 поступают инверсные значения соответственно первого и второго числа, которые записываются в соответствующие счетчики 12 и 17. На шину 20 режима потенциалом логической 1 поступает сигнал Работа, крторый передним фронтом счетных импульсов генератора 13 записывается в D-триггер 16. Сигнал логической 1 на выходе Ъ -триггера 16 разрешает прохождение счетных импульсов генератора 13 через элемент И 14, с выхода которого счетныеимпульсы поступают на счетный вход счетного триггера 11, работакяцего по отрицательному фронту, где -частота следования счетных импульсов делится на, два. Импульсы с выхода счетного триггера 11 поступают на счетные входы счетчиков 12 и 17 (которые работают, по отрицательному фронту), содержимое которых по каждому импульсу увеличивается на единицу. По первому отрицательному фронту на С-входе В -триггера 9 в него записывается 1, которая поступает на второй управляющий вход коммутатора 7 и разрешает прохождение через него счетных импульсов с его первого информационного входа.

Логическая единица с выхода 15 -триггера 9 поступает также на входы сброса Г-триггеров 4 и 5, которые работают по отрицательному фронту, и разрешает запись информации в эти триггеры с D -входов. Импульсы, поступаящие после установки D -триггера 9 в единичное состояние с выхода счетного триггера 11, управляют работой Б-триггеров 4 и 5 следующим образом: по первому импульсу в D -триггер 4 за.1 писывается 1, а в D -триггер 5 , по второму импульсу в D -тригге А эаписьшается О, а в D-триггер 5 1, по третьему импульсу в1)-тригге 5 записывается О, а D -триггер 4 остается в нулевом состоянии, так ка на установочном входе во время записи находится О. По приходу последующих импульсов работа Б -триггеров 4 и 5 проходит аналогично. На выходе элемента И 6 (при наличии 1 на втором, третьем и четвертом входе) по приходу счетного формируется импульс, длительнсэсть которого равна длительности ctjieTHoro импульса. Количество импуль С0В на выходе элемента И 6 равно 1/3 меньшего числа, а при равенстве чисел - 1/3 одного из чисел. После того, как один из счетчиков 12 или 17 переполняется, на выходе элемента ИПИ-НЕ 15 формируется О, которьш поступает на вход сброса КЙ-триггера 8 и устанавливает его в Q. Изменение состояния R5 -триггера 8 переключает KdNMyTaTop 7 в полс жение, при которой на его выход псютупают импульсы с выхода счетного триггера. Переполнение следующего счетчика приводит к тому, что на выходе элеме|нта ИЛИ-НЕ 18 появляется сигнал Конец работы (выход 26 конца вычислений) , запрещающий прохождение счетных импульсов через элемент И 14. Если числа, записанные в счетчики 12 и 17, оказываются равн1)1ми, то сигналы переполнення с выходов счетчИков 12 и 17 устанавливаются по одному и тому же счетному импульсу. В этом случае на выходе элемента И-НЕ 18 появляется сигнал, запрещаюсций прохождение счетных импульсов через элемент И 14. 156 Таким образом, на выходе элемента ИЛИ 2 формируются импульсы, количество которых равно корню квадратному из суммы квадратов двух чисел, на выходе коммутатора 7,- импульсы, количество которых равно сумме двух чисел, а на выходе элемента И 10 импульсы, количество которых равно разности двух чисел. Время вычисления, независимо от выполняемой операции, определяется из соотношений 2Т(А+1)+ ir ,при Т ВЫЧМсл I 2Т(В+1Х.;Г5, при где А,В - модули операндов-, Tg - задержка срабатьшания цепи блокировки, Т - период повторения счетных импульсов. Период повторения счетных импульсов выбирается из следующих сообра- жений где t - длительность счетного импульсаtn - длительность паузы. Длительность счетного импульса ограничивается временем задержки срабатьгоания)Триггеров 9 и 16, т.е. fcti Длительность паузы между импульсами ограничивается временем задержки срабатывания счетчиков 12 и 17, элемента ,ИЛИ-НЕ 15, триггеров 8.и 11 и коммутатора 7, г-е. Таким образом, введение двух 3)-триггеров и трех элементов И и элемента ИЛИ позволяет расширить область применения устройства за счет получения возможности извлекать корень квадратный из суммл квадратов двух чисел одновременно с получением их суммы и разности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU408306A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство | 1980 |

|

SU924699A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-04-28—Подача