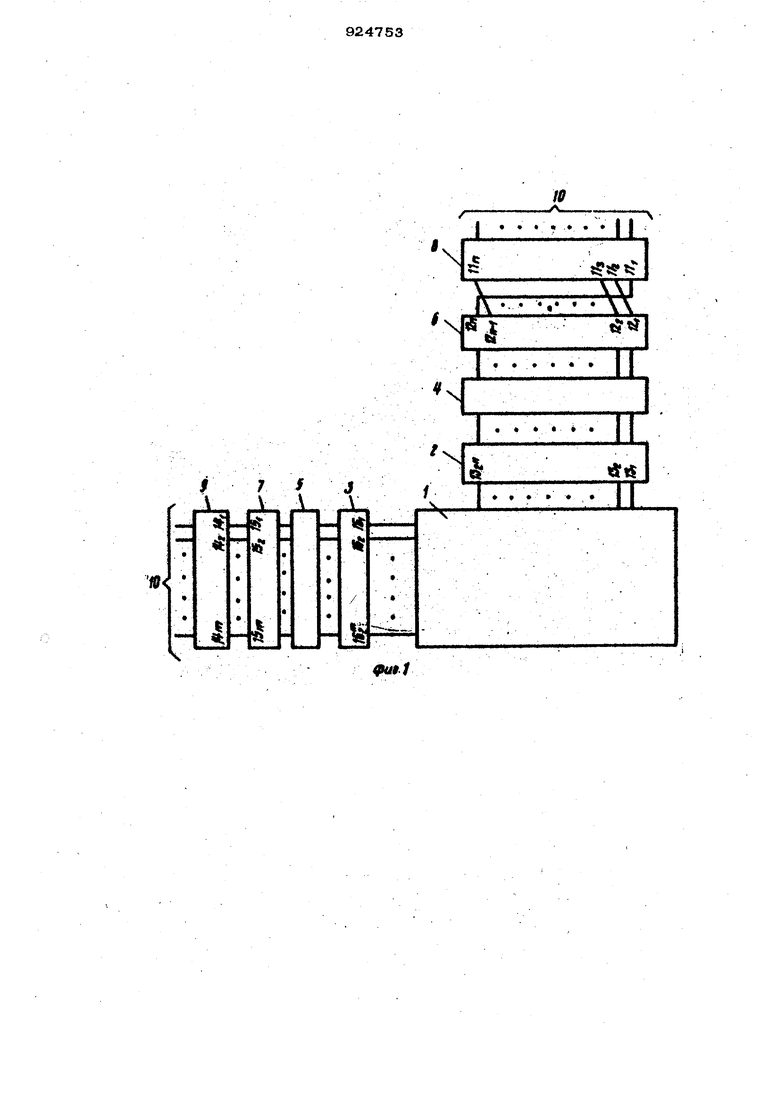

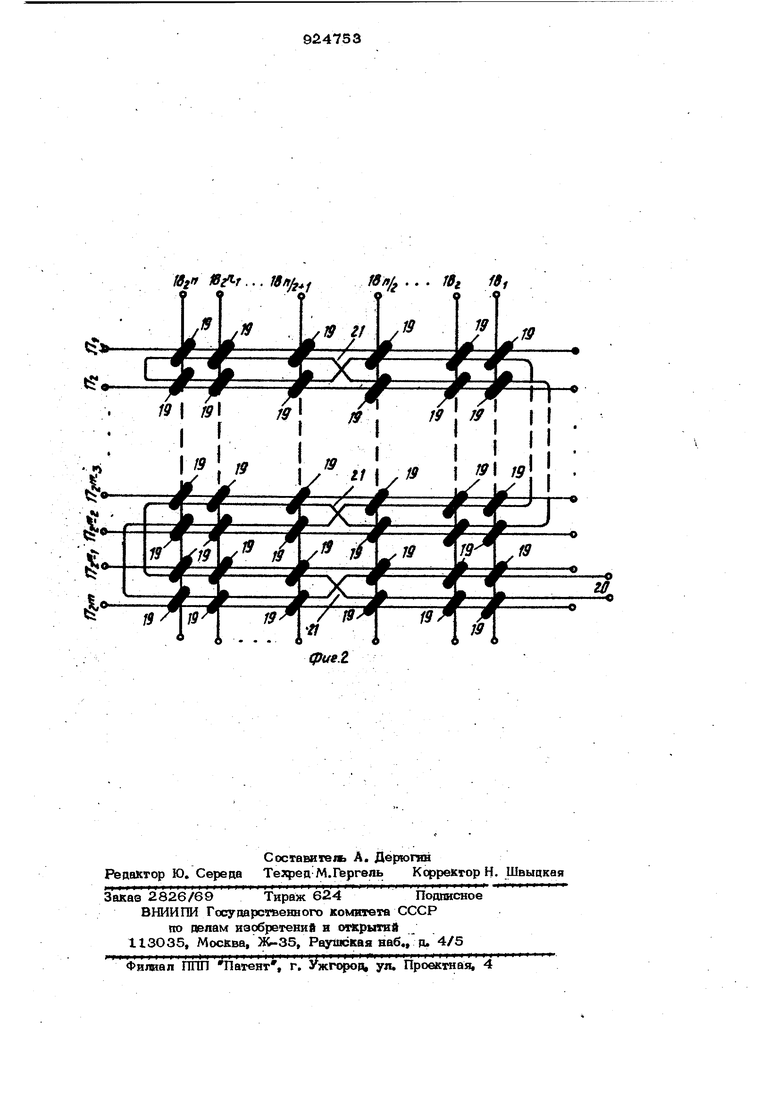

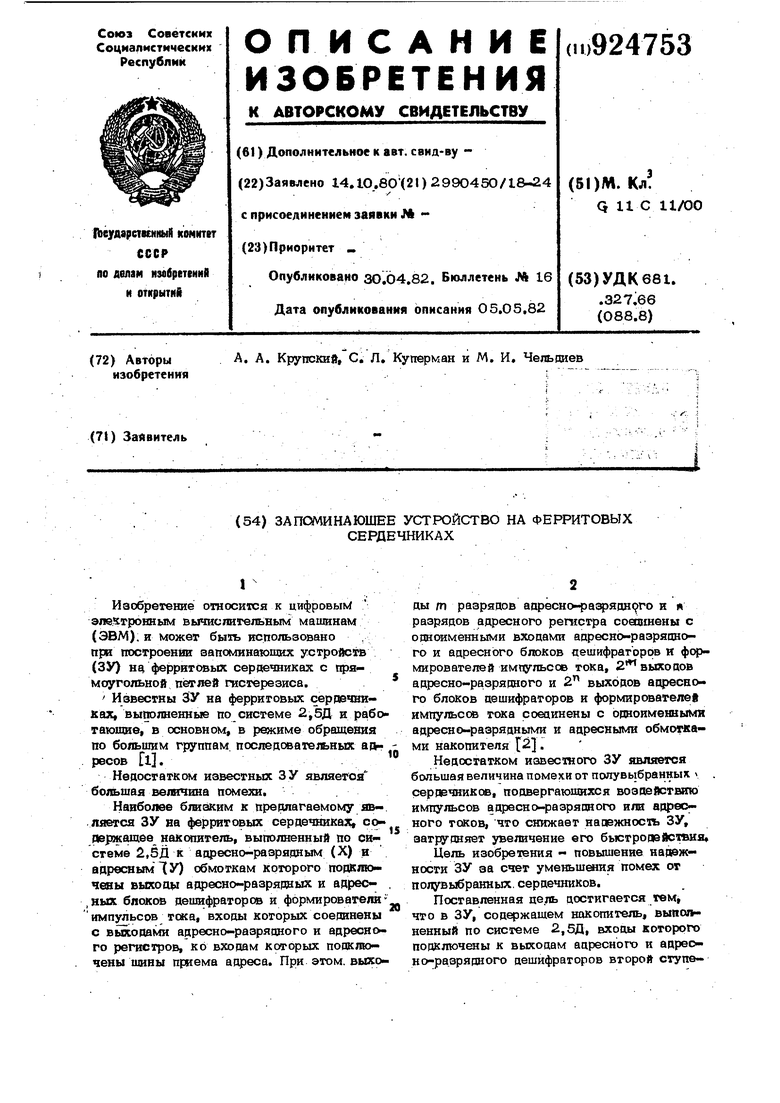

ни, входы которых порвключеиы к выходам адресных и адресно-разрядных формирователей входы Которых посислючены к выходам адресного и адресно-разрядного дешифраторов первой ступени, рходы которых подключены к выходам адресного и адресно-разрядного pierHCTpoB соответственно, входы подключены к адресным шинам, первый вькод адресного репнстра подключен к п -му входу адресного да- шифратора первой ступени, а выход адресного регистра с второго по Sr -ый ПОДКЛЮЧЙ1Ы к входам адресного дешифраторй первой ступени с первого по (тл-I)-и соответственно. На фиг. 1 изображена схема предлагаемого устройсгеа на фиг. 2 - схема прошивки одного разряда накопителя. Устройство содержит накопитель 1, адресный блок 2 дешифраторов второй ступе ни,адресно-разрядный блок 3 дешифраторов второй ступени, ааресный блок 4 формирователей импульсов гока,адресно-разрядный блок 5 формирователей импульсов . тока, адресный блок 6 дешифраторов первой ступени, адресно-разрядный блш 7 дешифраторов первой, ступени, арресный регистр 8 на П разрядов, аруресно-раэряганый регистр 9 на гл разрядов, шины приема адреса 10, выкоды адресного регистра ±1 - 11 , входы адресного блока дешифраторов первой ступени 12 12fi выходы адресного блока дешифраторов второй ступени , выходы а{Н ресно-разрядного регистра l4 -14rn,. входы адресно-разрядного блока дешифраторов , первой ступени, выходы адресно разрядного блока цешнфраторов второй ступени адресно-раэрядные обмотки накопителя , адресные обмсфки накопителя IS., ферритовые сердечники 19, выходную обмотку 2О, перекрестия прсеодов выходно обмотки 21. Накопитель 1 содержит координаты обмотки: адресно-разрядные 17,- 17||П, к которым подключены одноименные выхо ы 16 -16 «айресно-разряднбго блока д ишфраторов второй ступени 3, и адресны ia)-18j,n, к которым ггодключены одно именные выходы адресного бло ка деишфраторов второй ступени 2. Выходы адресно-разрядного репнсгра 9 соединены с одноименными входами адресно-разрядного блока 7 дешифраторов первой ступени. Выходы адресного регистра 8 Соединены со входами блока 6 дешифраторов первой ступени следуюшим образом: выход первого (младшего) разряда адресного регистра 8 соединены со входом 12 последнего (старшего) разряда адресного блока 6 дешифраторов первой ступени, выходы со второго по и -и адресного регистра 8 подключены ко входам с первого по (п-1)-й ащзесного блока дeшифpaтqэa первой ступени 6. За счет такого выпо1В1ения связей .ааресного регистра с адресным блоком дешифраторов первой ступени при подаче последовательных адресов на регистр адреса адресные обмотки выбираются поочередно слева и справа от перекрытия выходной обмотки. Устройство работает следующим образом. Допустим, что выбираемый массив имеет адреса с 18 -18 , а для хранения рассматриваемого разреда массива используются сердечники, находящиеся на пересечении обмотки 17 й обмоток 18jj по , При обращении к этому массиву последовательно выбираются адресные обмотки 18 -l8( . 18. J.a.a7i) 183 , 18(2,,) 18,0 при этом с каждой адресной обмоткой выбираются адресно-разрядная обмотка I7t . Такая последовательность выборки адресных, обмоток повторяется при любой выбранной адресно-разрядной обмотке. Оценим значение той составляющей помехи от полувыбранных сердечников, которая связана с неидентичносгью состояний компенсирующих друг друга пар полувыбраннык сердечников, расположенных с разных сторон от перекрестия. Помеха от полувыбранных сердечни- КОВ возникает при воздействии на них импульса тока считывания только по одной из координат/ причем большую помеху дают сердечники, находящиеся в состояни5нс единицы и разрушенного нуля. Компенсация этих помех обес печивается прошивкой выхосиой обмотки с перекрещиванием прямого и обратного гроводсж, причем нетпучшая компенсация (суммарная помеха, близкая к нулю) обеспечиваетс% если на взаимно Компенсирующих отрезках выходной обмотки имеется одинаковое количество сердечников, дающих большую помеху, и ofomaKosoe малую помеху. После подачи тока считывания, например, в обмотку 17 все сердечники этой обмотки находятся в состояниях разрушенной единицы, либо в сосгоян1ш нуля, т.е. при следуквдем считывашш все

они цатот мадую помеху, и обеспечивается наилучшая компенсация. Если после эгого начинается обращение к некоторому массиву и многократно выбирается обмотка 17ц , то. на сердечники обмотки 17|. воздействуют импульсы тока в обмотках Чв, l8t2(iM); : isj /ie jn/b+j) и т.д., после которых соответствующие се дечники остаются в состояниях единицы либо разрушенного нуля т.е. тфи следу ющем обращении они дают большую помеху. Поскольку подача токав обмотки 18 в предлагаемом устройстве произвел дится поочередно - сперва в одну обмот КУ слева от перекрестия проводов Bbucoffrной обмотки, затем в одну обмотку от перекрестия проводов выходной о&мотки и т.д., то наибольшая суммарная помеха гфи первом обращении к обмогке 17j , отличается от слепая наилучшей компенсаций только на величину разности между большой и малой помехами с одной пары сердечников. Аналогичный э4 фект достигается также во всех ддггих случаяз4 например, если перед обращени-у ем к данному массиву по рассматриваемой обмомсе подается имцульс тоКа записи..

Таким образом, в предлагаемом устройстве рассматриваемая составляю-., щая помехи от попувыбранных сердечников по адресно-разрядным обмоткам умень- шаегся в раз, а по адресным обмоткам в раз. Для современных массовых ЗУ системы 2,5Д значения 2 и 2 составляют соответственно 256 512 и 32-64, поэтому в предлагаемом устройстее суммарная уменьшается в несколько раз. Это позволяет cj щественно повысить надежность (вероятность бессбойной работы устройства,

либо увеличить быстродействие устройства в 1у2-2 раза за счет уменьшения времени затухания помехи.

Формула, изобретения

Запоминающее устройство на ферриговых серпе ошках сопержащее HaKototTenb, вьтолненный по с{к;теме 2,5Д, входы которого подключены к выходам адресного и адресно-разрядного дешифраторов второй ступени, входы которых подключ №Ы к выходам ааресных и адресно-разрядных формирователей, входы которых пошило чены к выходам адресного и адресно-раэрядного дешифраторов первой ступени, входы которых подключены к выходам адресного и адресно-разрядного регистров соответственно, входы которых подключены, адресным Ш1шам, отличающее с я тем, что с целью пежышения надежности устройства, в нем первый выход адресного регистра подключен к входу адресного дешифратора первой сту пени, где гт -число разрядов адресного регистра, а выходы адресного регистра с второго по п -и подключены к входам адресного деши4ратора первой ступени с первого по { п-1)-й соответственно.

Источники информации, принятые во внимание при экспертизе

1. Запоминающее устройство совреМеайых 3UBMi Сб. статей под ред. Крупского А. А. М., Мир, 1968, с. 56.

2. Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные машины, М., Энергия, 1975, с. 161 (прототип).

i

JU

I -; v - 41

I

л

f « V

t

IE

. fgf ... 18 n/ ... I8i 181

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ обращения к запоминающему устройству на ферритовых сердечниках типа 2,5 Д | 1984 |

|

SU1144151A1 |

| Блок управления для запоминающего устройства | 1976 |

|

SU572846A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| МАГНИТНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU329578A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1974 |

|

SU555437A1 |

| Запоминающее устройство с произвольным доступом и одновременной выборкой переменного массива слов | 1983 |

|

SU1167655A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

Авторы

Даты

1982-04-30—Публикация

1980-10-14—Подача