1

Изобретение относится к области вычислительной техники, в частности, к запоминающим устройствам типа 2,5Д на ферритовых сердечниках.

Известны блоки управления для запоминающего устройства, содержащие адресный регистр, адресно-разрядный регистр, регистр записи и хронизатор 1, 2.

Наиболее близким к данному изобретению является устройство, рассмотренное в работе 2. Недостаток этого устройства заключается в невысокой надежности ввиду возможности возникновения б - помехи больщой амплитуды и длительности.

Целью изобретения является повышение надежности работы запоминающего устройства путем снижения уровня б - помех.

Поставленная цель достигается тем, что в блок управления для запоминающего устройства, содержащий узел синхронизации, вход которого соединен с щипой обращения, а выходы - с регистрами записи, адресиым и адресно-разрядиым, кодовые шины адреса и приема числа, введены коммутаторы кодовых шин адреса и приема числа, коммутаторы адреса восстановления, счетчик обращений и счетчик адреса восстановления, выходы которого через коммутатор адреса восстановления подключены к адресно-разрядному регистру, причем вход счетчика обращепий соединен с

щиной обращения,а выход-со входами управления счетчика адреса восстановления и коммутаторов, а кодовые шины адреса и приема числа подключены к ннформациониым входам соответствующих регистров через коммутаторы соответственно адреса и приема числа.

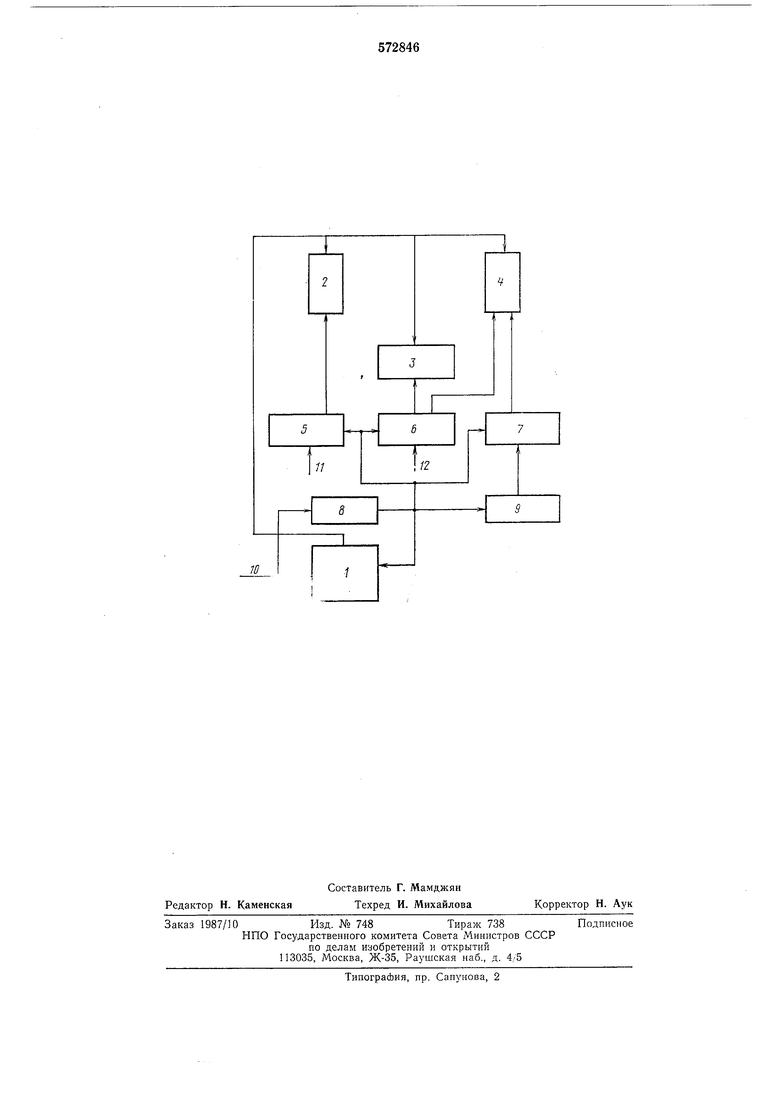

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит Ззел 1 синхронизации, регистр записи 2, адресный 3 и адресно-разрядный 4 регистры с соответствующими дешифраторами, коммутатор 5 приема числа, коммутатор 6 кодовых тин адреса и коммутатор 7 адреса восстановления накопителя, счетчик 8 обращения, счетчик 9 адреса восстановления. Выход нереполнения счетчика 8 обращений подключеи к входам блокировки коммутаторов 6 и 5, к входу узла 1 синхронизации, к входу разблокировки коммутатора 7 и к счетному входу счетчика 9. Кодовый выход счетчика 9 связан с кодовым входом коммутатора 7. Выходы коммутатора 7 подключены к адресно-разрядному регистру 4. Вход

синхроимпульсов по шине 10 обращений подключен к входу счетчика 8 и к входу узла 1 синхронизации. Коммутаторы 6, 7 включены между регистрами 3, 4 и соответствующими нм кодовыми шинами приема числа 11 и адреса 12.

Регистры записи 2, адресный 3 и адресноразрядный регистры 4 предназначены для промежуточного хранения числа и его адреса. Коммутаторы кодовых шин адреса 6 и числа 5 предназначены для блокировки поступления кода в ЗУ по кодовым шинам числа 11 и адреса 12.

Коммутатор 7 адреса восстановления предназначен для разрешения передачи кода адреса восстановления с кодовых выходов счетчика 9.

Счетчик обраш,ений предназначен для подсчета количества обращений к ЗУ. Максимальный коэффициент пересчета - коэффициент заполнения определяется максимальным значением б - помехи, накопленной за

циклов обраЩбНИЙ.

Счетчик адреса восстановления предназначен для периодического изменения адреса восстанавливаемой адресно-разрядной координаты. Максимальный коэффициент пересчета счетчика 9 равен количеству адресноразрядных координат в одном разряде ЗУ.

Устройство работает следуюш,им образом.

На вход узла синхронизации и на счетный вход счетчика обрашений поступает синхроимпульс обраш,ения. Поступление синхроимпульса на счетный вход счетчика 8 увеличивает заполнение счетчика на единицу.

Если при этом счетчик 8 не переполняется, т. е. количество синхроимпульсов не превышает коэффициент заполнения (), то с выхода переполнения счетчика 8 поступает сигнал на входы коммутаторов 5, 6, разрешающий поступление информации с кодовых шин числа И и адреса 12. Одновременно сигнал с выхода переполнения счетчика 8 поступает на вход коммутатора 7 и вход узла синхронизации, в которых, соответственно, запрещает прохождение кода с выходов счетчика адреса восстановления в адресно-разрядный регистр 4 и выработку строба восстановления для накопителя. В этом случае ЗУ выполняет команды, поступившие с машины.

Если при поступлении синхроимпульса счетчик 8 переполняется, то сигнал переполнения запрещает поступление информации с кодовых шин числа 11 и адреса 12 ЗУ. Одновременно сигнал переполнения, поступая на счетный вход счетчика адреса восстановления, изменяет состояние счетчика 9 на единицу и разрешает прохождение кода с выхода данного счетчика на адресно-разрядный регистр 5 через коммутатор 7. Разрешается также выработка синхроимпульса узлом синхронизации и происходит восстановление координаты, адрес которой указывает счетчик адреса. Таким образом, производится последовательное разрушение «тяжелого кода по всем адресно-разрядным координатам накопителя и не допускается увеличения б - помех больше допустимых в любой адресно-разрядной координате накопителя.

Формула изобретения

Блок управления для запоминающего устройства, содержащий узел синхронизации, вход которого соединен с шиной обращения, а выходы - с регистрами записи, адресным и

адресно-разрядным, кодовые шины адреса и приема числа, отличающийся тем, что, с целью повышения надежности блока, он содержит коммутаторы кодовых шин адреса и приема числа, коммутаторы адреса восстановления, счетчик обращений и счетчик адреса восстановления, выходы которого через коммутатор адреса восстановления подключены к адресно-разрядному регистру, причем вход счетчика обращений соединен с шиной

обращения, а выход - со входами управления счетчика адреса восстановления и коммутаторов, а кодовые шины адреса и приема числа подключены к информационным входам соответствующих регистров через коммутаторы соответственно адреса и приема числа.

Источники информации, принятые во внимание при экспертизе 1. Бардиж В. В. Магнитные элементы ЦВМ «Энергия, 1974.

2. Запоминающие устройства современных ЭЦВМ, Сб. ст. Перевод с английского под ред. А. Крупского, «Мир, 1967, с. 58-63.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275520A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для регистрации сигналов, представленных в цифровой форме | 1976 |

|

SU659904A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Авторы

Даты

1977-09-15—Публикация

1976-04-22—Подача