Известны магнитные запоминающие устройства (МЗУ) с автономным контролем, содержащие накопитель, налример, на фсрритовых сердечниках, с .которым соединены разрядные формирователи записи, адресный счетчик, вход которого связан с выходом блока синхрон 1зации, и управляемый от адресного счетчика блок формирования тяжелого кода, служащий для записи заданной контрольной последовательности «1 и «О в разрядной плоскости накопителя МЗУ (куба памяти).

Недостатком известных МЗУ с автономным контролем является запись тяжелого кода в проверяемом разряде, не зависимая от других разрядов накопителя, из-за чего при последующем считывании с контролем не всегда обеспечиваются наиболее тяжелые условия помехообразования с учетом взаимного влияния разрядных цепей. В известных МЗУ возможно также необпаружение групповых отказов в четном числе разрядов (при контроле ио нечетности). Другой недостаток известных МЗУ с автономным контролем заключается в том, что их схема не обеспечивает произвольного количества обращений по контролируемому адресу, в силу чего при чтении не создаются наиболее тяжелые условия для выделения полезного сигнала на фоне помех от полувыбранных запоминающих элементов.

устройство с автономным контролем отличается от известных тем, что оно содержит блок поразрядного унравления записью, состоящий из счетчика обходов адресов, вход которого подключен к выходу адресного счетчика; дешифратора выбора разряда, входы которого подключень к выходам каскадов счетчика обходов адресов; разрядных схем равнозначности, один вход каждой из которых подключен к Jшфop aцнoннoмy выходу блока формирования тяжелого кода, другой вход - к соответствующе.му вы.чоду дешифратора выбора разряда, а выход соединен со входом соответствующего разрядного формирователя записи. Количество схем равнозначности равно количеству разрядов в слове или части слова (байте) МЗУ.

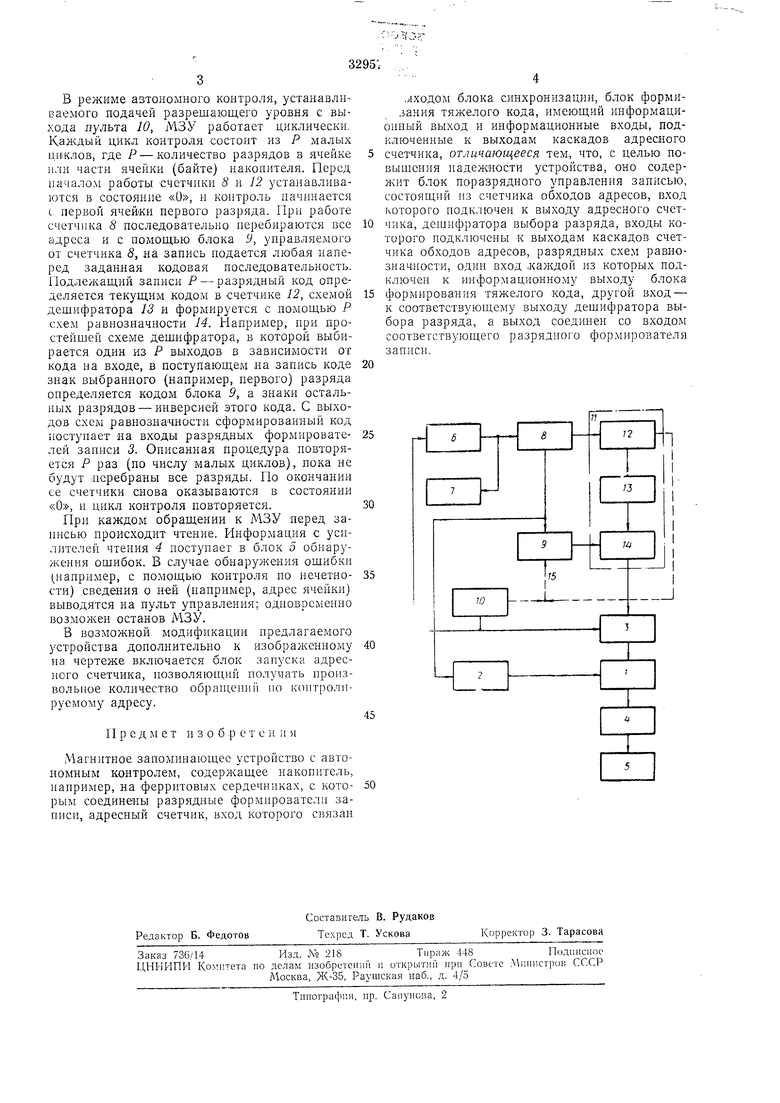

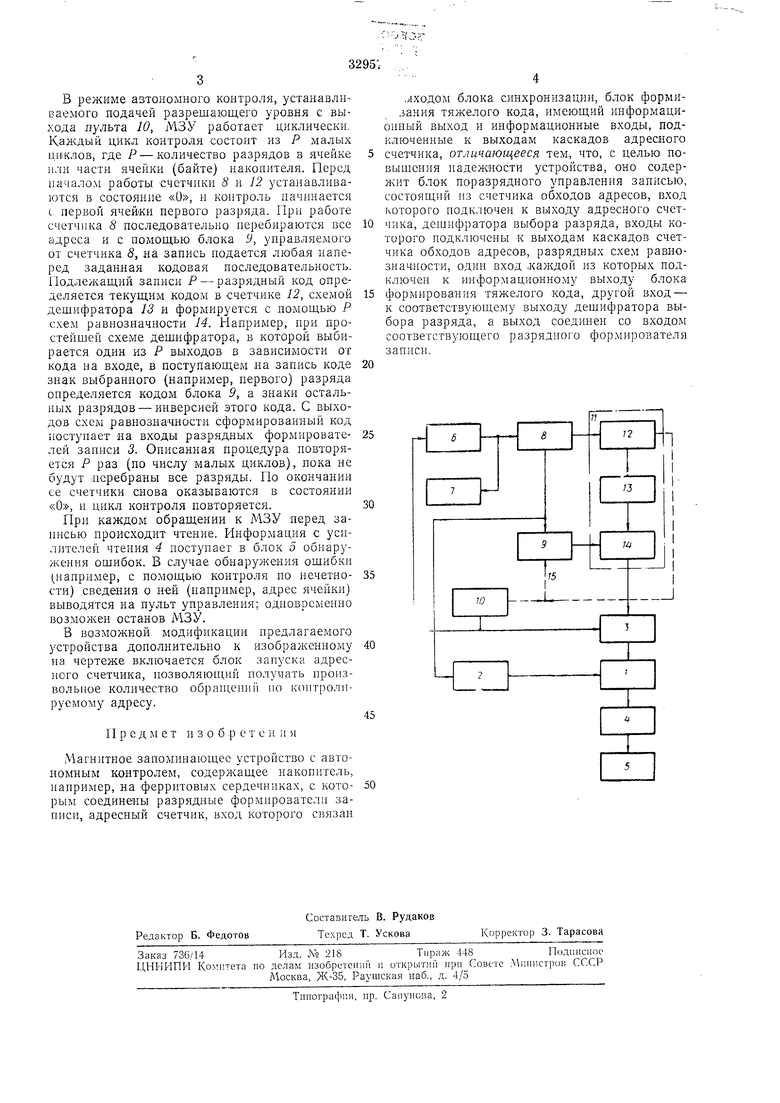

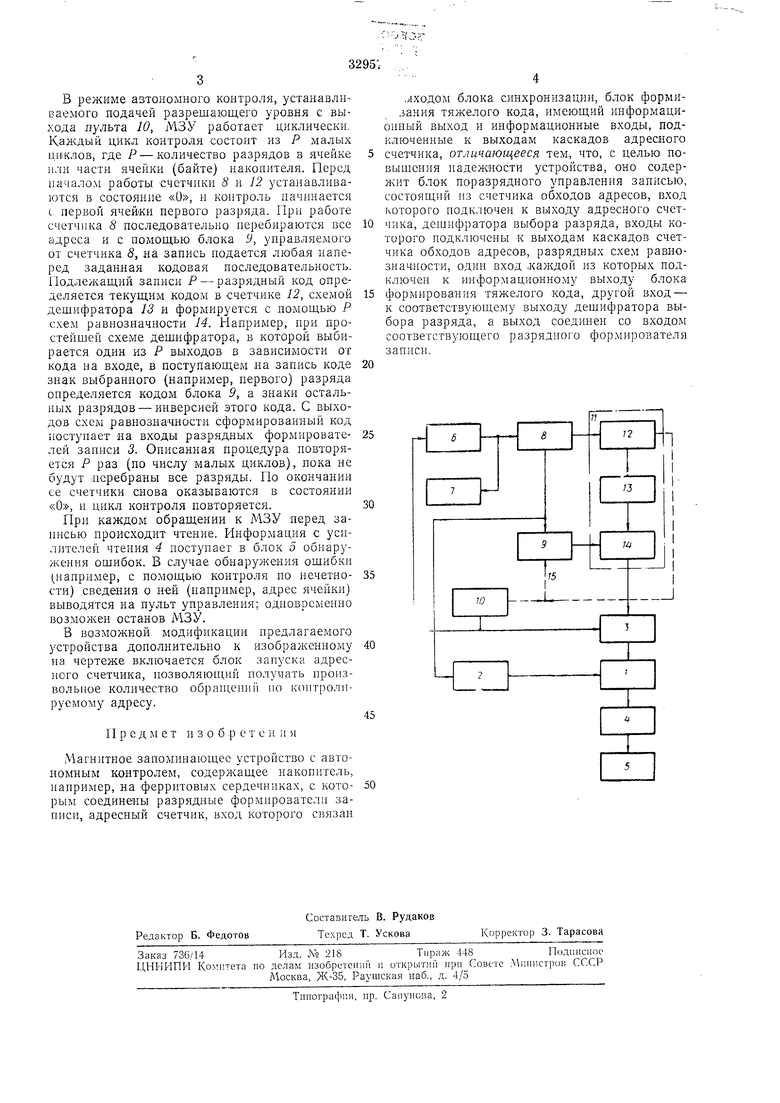

На чертеже показана блок-схема предлагае-мого устройства.

Устройство содержит накопитель /, адресные формирователи выборки 2, разрядные формирователи 3, усилители 4, блок 5 обнаружошя ошибок, блоки синхронизации 6 и задания времениой диаграммы устройства 7, адресный счетчик 8, блок 9 формирования тяжелого кода, пульт управления 10 и блок // управления поразрядной записью, включающий в себя счетчик 12 обходов адресов, дешифратор выбора разряда 13 и разрядные схемы равнозначности 14.

в режиме автономного контроля, устанавливаемого подачей разрешающего уровня с выхода пульта 10, МЗУ работает циклически. цикл контроля состоит из Р малых циклов, где Р - количество разрядов в ячейке или части ячейки (байте) иакопителя. Перед началом работы счетчики 8 и 12 устаиавлнваются в состояние «О, н контроль начинается с первой ячейки первого разряда. При работе счетчика 8 иоследовательно перебираются все адреса и с помощью блока 9, управляемого от счетчика 8, на запись подается любая наперед заданная кодовая последовательность. Подле/кащий записи Р - разрядный код определяется текущим кодом в счетчике 12, схемой дешифратора 13 и формируется с помощью Р схем равнозначности 14. Например, при простейщей схеме дешифратора, в которой выбирается один из -Р выходов в зависимости от кода иа входе, в поступающем на запись коде знак выбранного (например, первого) разряда определяется кодом блока 9, а знаки остальных разрядов - инверсией этого кода. С выходов схем равнозначности сформированный код поступает иа входы разрядных формирователей записи 3. Описанная процедура повторяется Р раз (по числу малых циклов), пока не будут :иеребраны все разряды. По окончании ее счетчики снова оказываются в состоянии «О, и цикл контроля повторяется.

При каждом обращении к МЗУ перед записью происходит чтение. Информация с усилителей чтения 4 поступает в блок 5 обнаружения ошибок. В случае обнаружения ошибки (например, с помощью контроля ло нечетности) сведения о ней (например, адрес ячейки) выводятся на пульт управления; одновременно возмол :ен останов МЗУ.

В возможной модификации предлагаемого устройства дополнительно к изобрал енному на чертеже включается блок запуска адресного счетчика, позволяюпщй получать произвольное количество o6paHi,einiii но контролируемому адресу.

Предмет и з о б .р е т е и и я

Магнитное запоминающее устройство с автономным контролем, содержащее накопитель, например, на ферритовых сердечниках, с которым соединены разрядные формирователи записи, адресный счетчик, вход которого оуязан

.лходом блока синхронизации, блок формизання тяжелого кода, имеющий информационный выход и информационные входы, подключенные к выходам каскадов адресного счетчика, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок поразрядного управления записью, состоящий из счетчика обходов а,ресов, вход которого подключен к выходу адресного счетчика, дешифратора выбора разряда, входы которого подключены к выходам каскадов счетчика обходов адресов, разрядных схем равнозначности, один вход .каждой из которых подключен к информационному выходу блока формирования тяжелого кода, другой вход - к соответствующему выходу дешифратора выбора разряда, а выход соединен со входом соответствующего разрядного формирователя записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Устройство для обучения записи информации в память ЭВМ | 1983 |

|

SU1153340A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387046A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Даты

1972-01-01—Публикация