Изобретение относится к запоминающим .устройствам и может быть использовано в ассоциативных процессорах.

Известна ассоциативная запоминающая матрица, содержащая запоминающие ячейки, подключенные к управляющим i шинамС1Э.

Недостатком этой ассоциативной матрицы является отсутствие информации о правильности ее функционирования.

Наиболее близкой к изобретению является ассоциативная запоминающая матрица, содержащая ассоциативные ячейки, каждая из которых состоит из элемента памяти, элементов записи и сравнения, причем выходы элементов записи .подключены к соответствующим входам элемента памяти,выходы которого юдключены к первым двум входам элементов сравнения, выходы которих подсоединены к шине результата опроса данной строки, первые входы элементов записи ячеек каждой строки подключены к адресной шине данной строки, вторые входы элементов записи и вторые,входы элементов сравнения ячеек п аждЬго столбца соединены попарно и подключены к соответствующим информационным шинам каждого столбца С2.

Однако отсутствие в этой ассоциативной запоминающей матрице элементов , выдающих информацию-о Тправильности функционирования матрицы, снижает, ее эксплуатационную надежность и является препятствием для построения высоконадежных ассоциатив10ных устройств и процессоров.

Целью изобрет-ения является повьииение надежности ассоциативной: запоминающей матрищл засчет повышения контролепригодности и достоверности ее

15 функционирования, сокращения времени обнаружения неисправности и локализации ее в рабочем режиме матрицы, что также повышает ремонтопригодность и коэффициент .готовности мат20рицы.

Поставленная цель достигается тем, что в ассоциативную запоминающую матрицу, содерясащую запотганающие ячейки, каждая из которых состоит из

25 элемента памяти, двух элементов сравнения и двух элементов записи, выходы которых подключены ко входам элемента .памяти, выходы которого соединены с первыми входами элементов

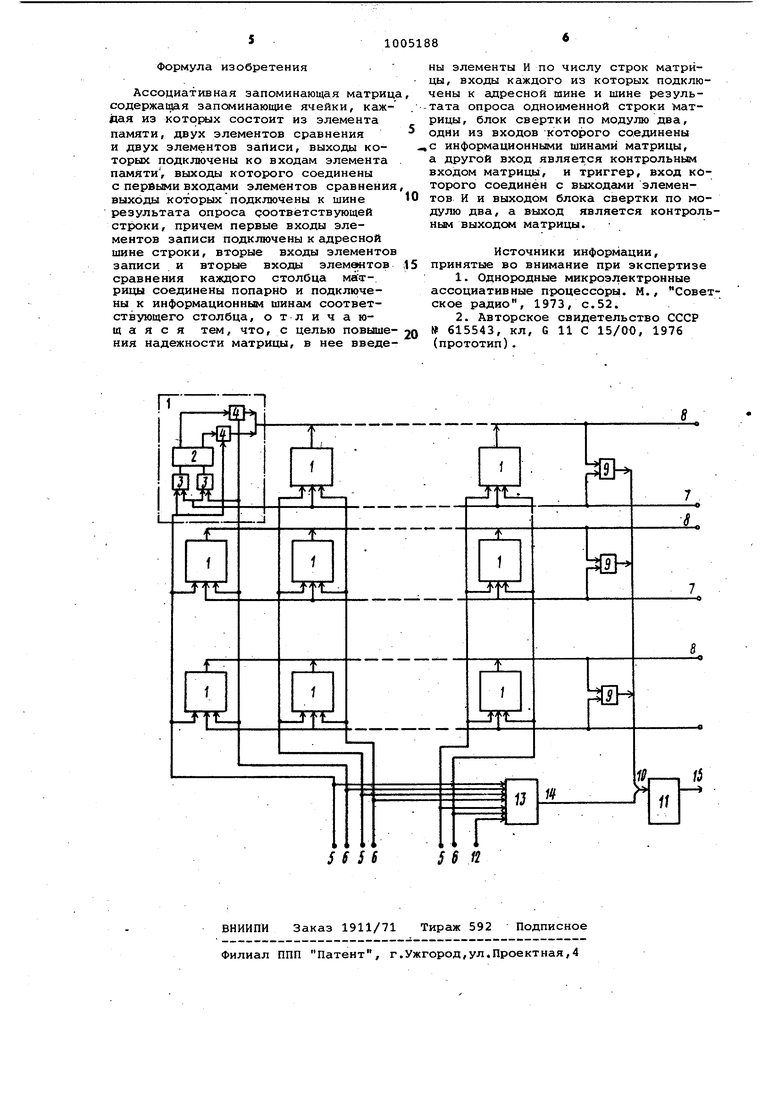

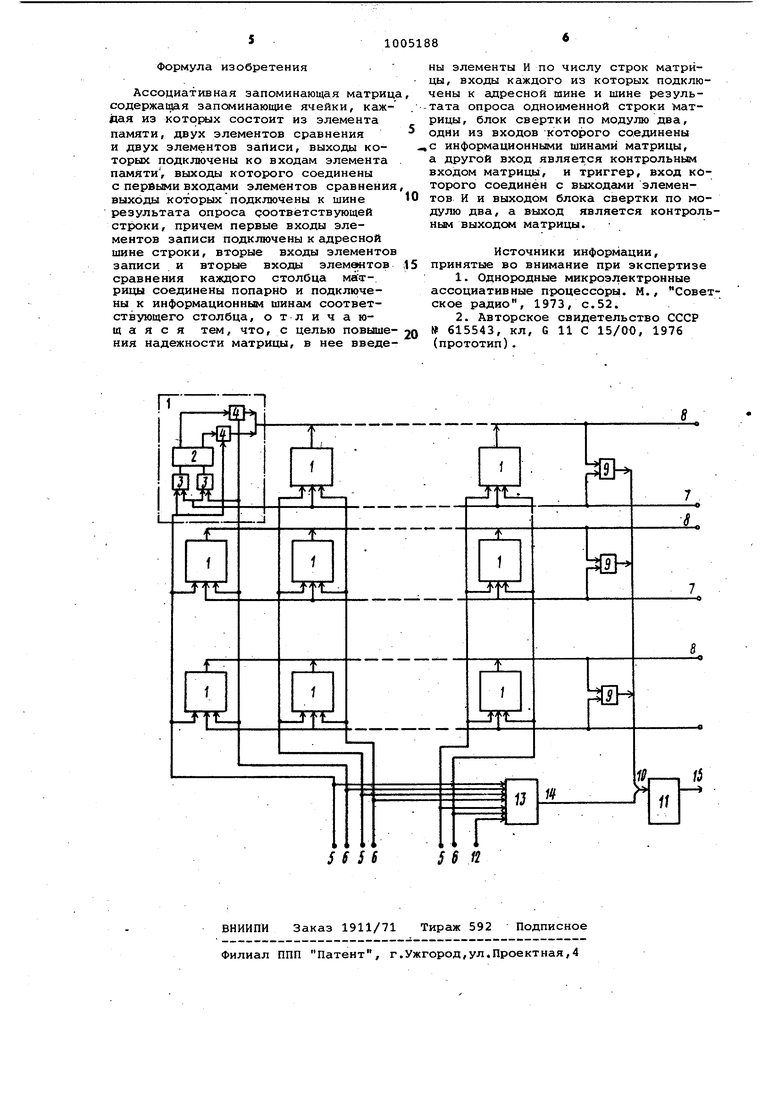

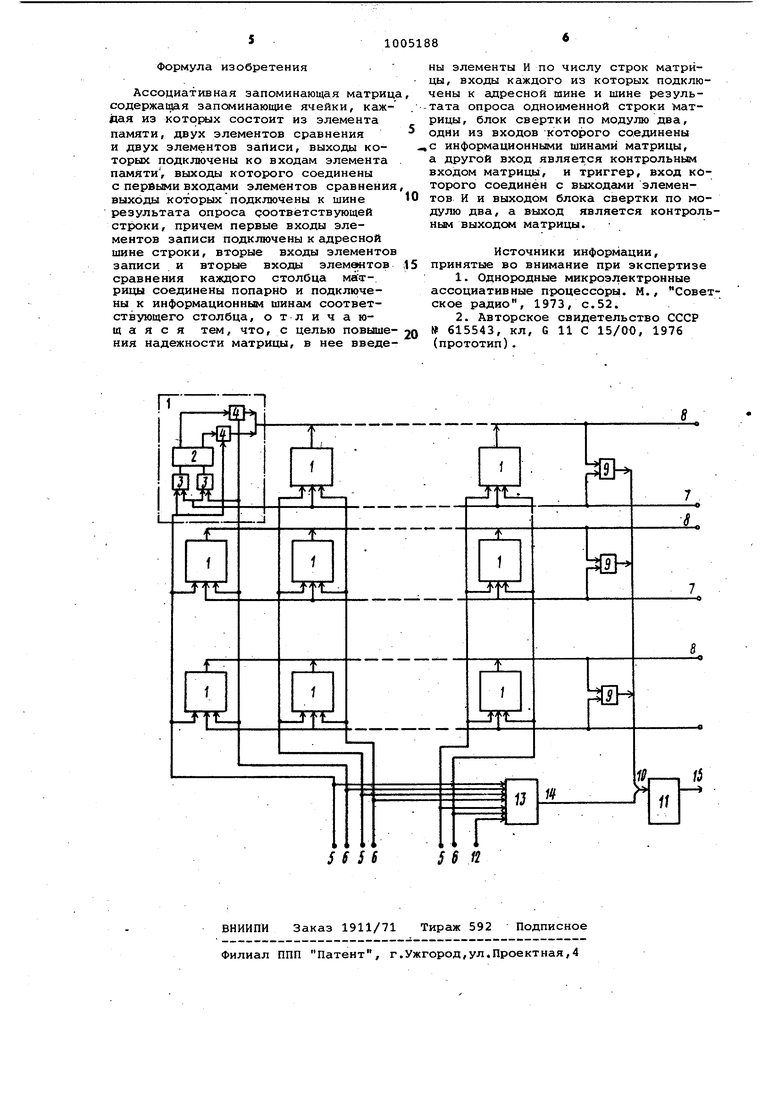

30 сравнения, выходы которых.подключены к шине результата опроса соответ ствующей строки, причем первые входы элементов записи подключены к адресной шине строки, вторые входы элементов записи и вторые входы эле ментов сравнения каждого столбца ма .рицы. соединены попарно и подключены к информационным шинам соответствующего столбца, введены элементы И по числу строк матрицы, входы каждого из которых подключены к адресной шине и шине результата опроса одноименной строки матрицы, блок свертки по модулю два, одни из вхо дов которого соединены с информацио ными шинами матрицы, а другой вход является контрольным входом матрицы и триггер, вход которого соединен с выходами элементов И и выходом бл ка свертки по модулю два, а выход является контрольным выходом матриц На чертеже представлена структур ная схема ассоциативной запоминающе матрицы, ; Матрица содержит запоминающие ячейки 1, каждая из которых включае в себя элемент 2 памяти, элементы 3 записи, элементы 4 сравнения. Первы входы элементов 3 записи и элементо сравнения, принадлежащих одному стол цу матрицы, объединены и подключены соответственно к информационным шинам 5,6 столбца. Вторые входы элементов- 3 записи соединены построчно с соответствугацей адресной шиной .7. Выходы элементов 4 сравнения каждой ячейки матрицы объединены построчно шиной 8 результата опроса. Каждая строка матрицы содержит двухвходовой элемент 9, подключенный своими входами к адресной шине 7 и к шине результата опроса данной строки. Выходы элементов И 9 объединены и подключены к единичному входу 10 триггера 11, Информационные шины 5, столбцов и контрольный вход 12 матрицы соединены со входами блока 13 свертки по модулю два. Выход 14 бло ка 13 также подключен к единичному входу 10 триггера 11, выход 15 которого является контрольным выходом матрицы. Матрица работает следующим образо При выполнении операции записи на адресуню шину 7 подается сигнал Логической 1, разрешающий запись через элементы 3 записи в элемент 2 памяти информации, поданной на информационные шины 5 и 6, при этом на шине. В результата опроса элементы 4 сравнения при правильном функционировании вырабатывают сигнал логического О. В случае наличия одиночной неисправности на входах и выходах всех элементов ячейки 1 элементов 3 записи, элемента 2-памяти и элементов 4 сравнения за исключением неисправнос ти типа Тождестве.нный О на выходах элементов 4 сравнения, на шине 8 результата опроса появляется сигнал логической 1. При проверке правильности функционирования ячеек 1 во время операции записи на один вход элемента И 9 поступает сигнал разрешения проведения контроля в виде логической 1 с адресной шины 7, а на другой вход поступает сигнал с шины 8 результата опроса, который при правильном функционировании равен значению логического О, а при наличии неиспра:вности в какой-либо ячейке 1 данной строки равен значению логической 1. В первом случае выход элемента И 9 равен значению логического О, во втором случае на выходе элемента 9 соответствующей строки появляется сигнал ошибки, равный логической 1. Сигналы ошибки от каждой строки ассоциативной запоминающей матрицы поступают на вход 10 триггера 11 которой служит для записи сигналов ошибок. На тот же вход 10 триггера 11 поступает сигнал с выхода 14 блока 13. Информация на шины 5,6 матрицы поступает в сопровождении контрюльного разряда по четности, подаваемого на вход 12. Информационные входные сиг- .налы матрицы с учетом сопровождающего контрольного разряда попарно сворачиваются в блоке 13. В случае наличия ошибки (нечетной кратности) в поступающей информации на выходе 14 блока 13 появляется значение логической 1, которое поступает на вход 10 триггера 11, что приводиттакже к появлению сигнала ошибки на контрольном выводе 15 асЬоциативной матрицы. Положительный эффект от использования предлагаемой ассоциативной матрицы в процессорах и в запоминающих устройствах вычислительных систем заключается в повьлаении их эксплуатационной надежности и достигается как в рабочем режиме работы матрицы, так в режиме профилактического тестового контроля. В рабочем режиме в момент записи информации в матрицу повышается достоверность функционирования матрицы. В режиме тестирования сокращается время обнаружения неисправностей и время поис-ка места неисправности (в 1,5 раза). Все этого в совокупности повышает ремонтопригодность и коэффициент готовности матрицы. J Введение в матрицу элементов И, блока свертки по модулю два и триггера может быть осуществлено на любом уровне: в корпусе интегральной схемы, на уровне -платы, на уровне функционального законченного узла ассоциативной матрицы или на уровне всей матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1980 |

|

SU903983A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

| Ячейка ассоциативной памяти | 1990 |

|

SU1751817A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

Авторы

Даты

1983-03-15—Публикация

1981-10-29—Подача