(54) УСТРОЙСТВО ЦИКЛОВОЙ. СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

Изобретение относится к технике связи и предназначено для использования в синхронных системах связи с импулъсно-ко- довой модуляцией.

Известно устройство цикловой синхронизации, содержащее счетчик .тактовой частоты передачи, последовательно соединенные входной и промежуточный регистры сдвига и декодер циклового синхросигнала, а также последовательно соединенные блок вьаделения тактовой частоты приема, причем второй выход блока выделения тактовой частоты приема соединен со счетным входом счетчика тактовой частоты приема tl

Однако известное устройство имеет большое время восстановления синхронизма по циклам.

Цель изобретения - сокрашенне времени восстановления синхронизации по циклам.

Для достижения указанной цели в устройство цикловой синхронизации, содержащее счетчик тактовой частоты передачи, последовательно соединенные входной регистр сдвига, промежуточный регистр сдвига и декодер циклового синхросигнала, а также последовательно соединенные блок вьщеления тактовой частоты приема, решающий блок и счетчик тактовой частоты приема, причем второйвыход блока выделения тактовой частоты приема соединен со счетным входом счетчика тактовой частоты приема, до10полнительно введен формирователь временного интервала ожидания синхросигнала, содержащий последовательно соединенные блок памяти, блок сравнения и элемент И, причем выход счетчика так15товой частоты передачи подключен к второму входу блока сравнения, выход диЕОдера синхросигнала подключен к второму входу элемента И, выход которого- соединен с вторым входом ре20шающего блока.

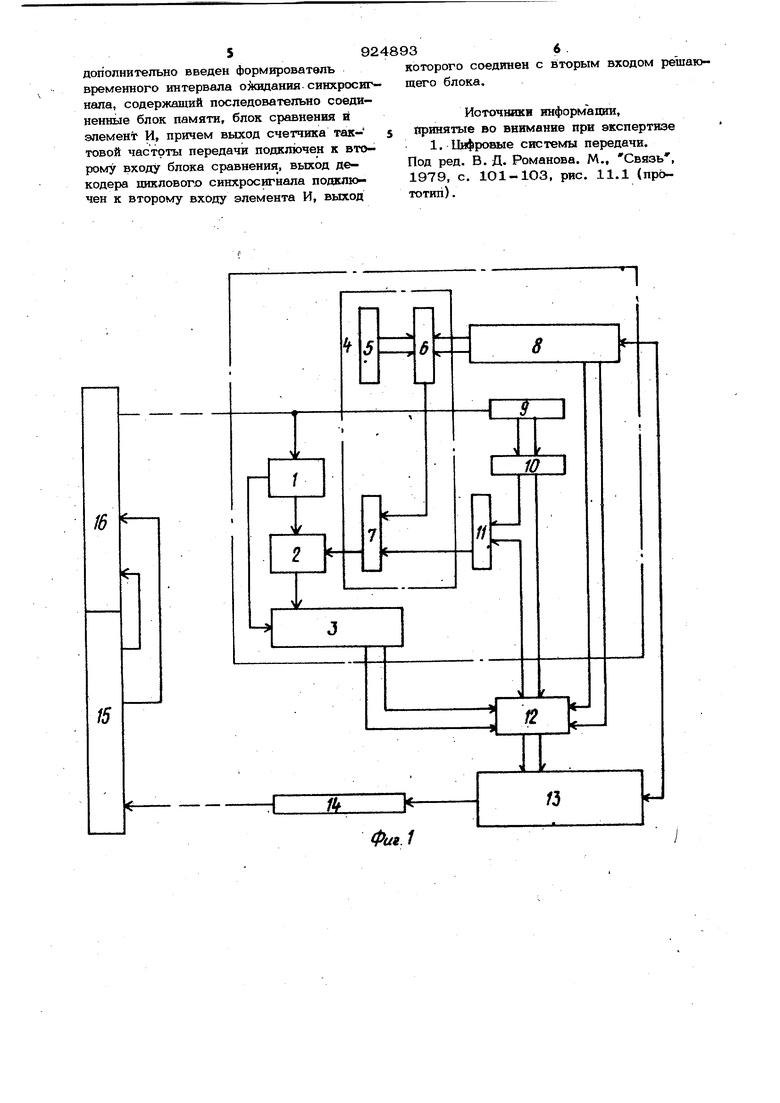

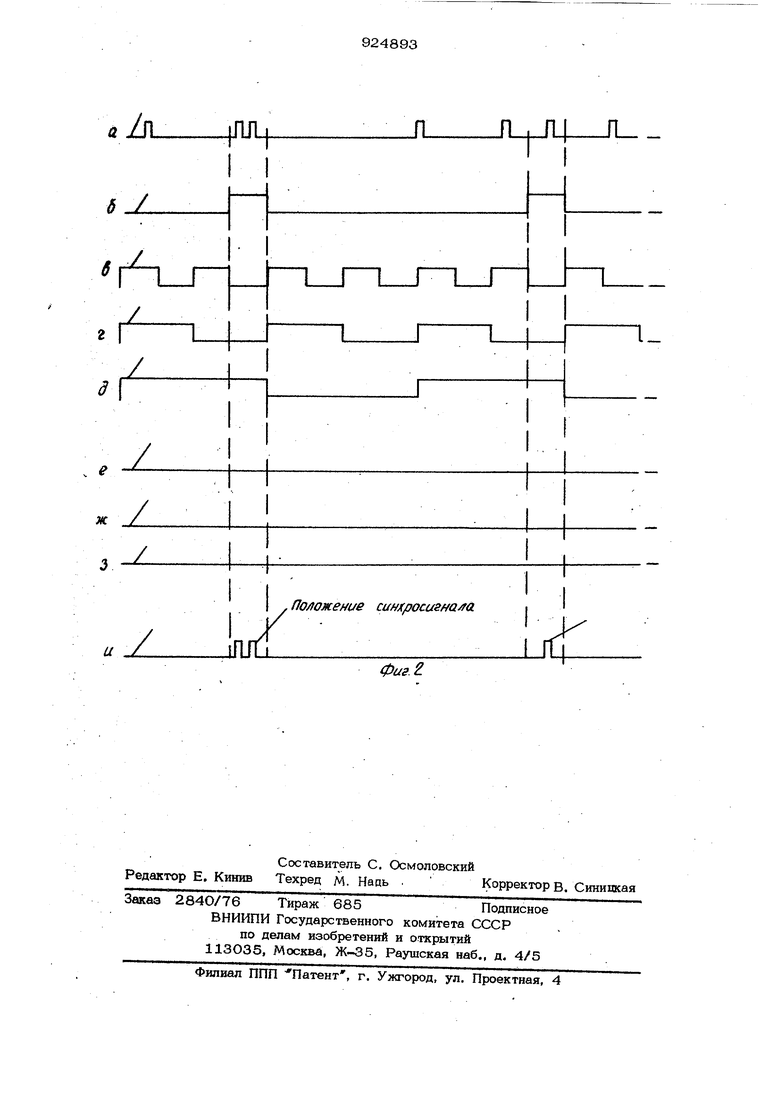

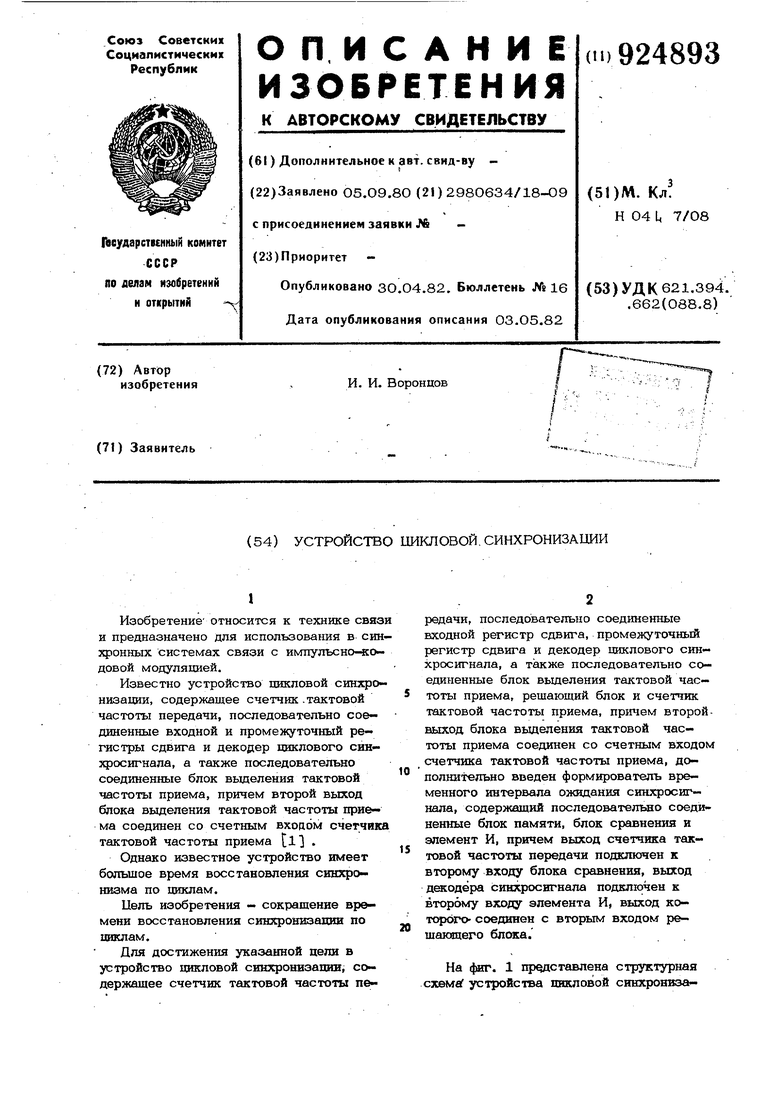

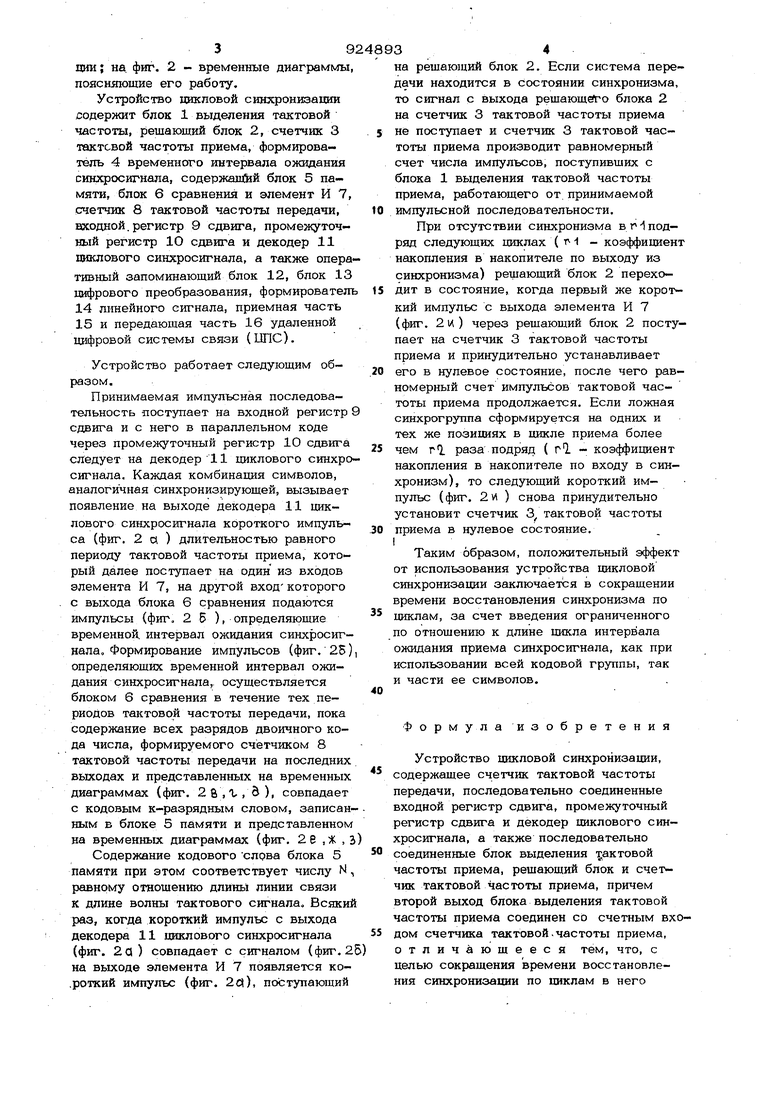

На фиг. 1 представлена структурная схемаГ устройства цикловой синхронвзаюга; на. фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство цикловой синхронизации содержит блок 1 выделения тактовой частоты, решающий блок 2, счетчик 3 гактсвой частоты приема, формирователь 4 временного интервала ожидания синхросигнала, содержаний блок 5 памяти, блок 6 сравнения и элемент И 7, рчетчик 8 тактовой частоты передачи, входной, регистр 9 сдвига, промежуточный регистр 10 сдвига и декодер 11 пиклового синхросигнала, а также оперативный запоминающий блок 12, блок 13 цифрового преобразования, формирователь

14линейного сигнала, приемная часть

15и передающая часть 16 удаленной цифровой системы связи (ЦПС).

Устройство работает следующим образом.

Принимаемая импульсная последовательность поступает на входной регистр 9 сдвига и с него в параллельном коде через промежуточный регистр 10 сдвига следует на декодер 11 циклового синхросигнала. Каждая комбинация символов, аналогичная синхронизирующей, вызывает появление на выходе декодера 11 циклового синхросигнала короткого импульса (фиг. 2 а ) длительностью равного периоду тактовой частоты приема, который далее поступает на один из входов элемента И 7, на другой вход которого с выхода блока 6 сравнения подаются импульсы (фиг, 26), определяющие временной, интервал ожидания синхросигнала. Формирование импульсов (фиг. 25), определяющих временной интервал ожидания синхросигнала, осуществляется блоком 6 сравнения в течение тех периодов тактовой частоты передачи, пока содержание всех разрядов двоичного кода числа, формируемого счетчиком 8 тактовой частоты передачи на последних выходах и представленных на временных диаграммах (фиг. 26,t,d), совпадает с кодовым к-разрядным словом, записан- ным в блоке 5 памяти и представленном на временных диаграммах (фиг. 26 ,% , З

Содержание кодового слова блока 5 памяти при этом соответствует числу N, равному отношению длины линии связи к длине волны тактового сигнала. Всякий раз, когда короткий импульс с выхода декодера 11 циклового синхросигнала (фиг. 2а) совпадает с сигналом (фиг. 25 на выходе элемента И 7 появляется ко.роткий импульс (фиг. 2а), поступающий

на решающий блок 2. Если система передачи находится в Состоянии синхронизма, то сигнал с выхода решающего блока 2 на счетчик 3 тактовой частоты приема 5 не поступает и счетчик 3 тактовой частоты приема производит равномерный счет числа импульсов, поступивших с блока 1 выделения тактовой частоты приема, работающего от. принимаемой

0 импульсной последовательности.

При отсутствии синхронизма в гI подряд следующих циклах ( г 1 - коэффициент накопления в накопителе по выходу из синхронизма) рещающий блок 2 перехо5 дит в состояние, когда первый же короткий импульс с выхода элемента И 7 (фиг. 2и) через решающий блок 2 поступает на счетчик 3 тактовой частоты приема и принудительно устанавливает

0 его в нулевое состояние, после чего равномерный счет импульсов тактовой частоты приема продолжается. Если ложная синхрогруппа сформируется на одних и тех же позициях в цикле приема более

5 чем г1 раза подряд ( г - коэффициент накопления в накопителе по входу в синхронизм), то следующий короткий импульс (фиг. 2и ) снова принудительно установит счетчик 3, тактовой частоты

0 приема в нулевое состояние. I

Таким образом, положительный эффект

от использования устройства цикловой синхронизации заключается в сокращении времени восстановления синхронизма по циклам, за счет введения ограниченного по отношению к длине цикла интервала ожидания приема синхросигнала, как при использовании всей кодовой группы, так

и части ее символов. 0

Формула изобретения

Устройство цикловой синхронизации, содержащее счетчик тактовой частоты передачи, последовательно соединенные входной регистр сдвига, промежуточный регистр сдвига и декодер циклового синхросигнала, а также последовательно соединенные блок выделения актовой частоты приема, решающий блок и счетчик тактовой частоты приема, причем второй выход блока выделения тактовой частоты приема соединен со счетным вхо5 дом счетчика тактовой.частоты приема, отличающееся тем, что, с целью сокращения времени восстановления синхронизации по циклам в него

дополнительно введен формирователь временного интервала ойзддания синхросигнала, содержащий последовательно соединенные блок памяти, блок сравнения и элемент И, причем выход счетчика тактовой частоты передачи подключен к второму входу блока сравнения, выход декодера циклового синхросигнала подключен к второму входу элемента И, выход

которого соединен с вторым входом решающего блока.

Источники информации, Принятые во внимание при экспертизе

А

&Jп , п

л

Л

/

г

ж

По/юженив cuHXpocuSffO a

ImtL

uA

фиг.:

Авторы

Даты

1982-04-30—Публикация

1980-09-05—Подача