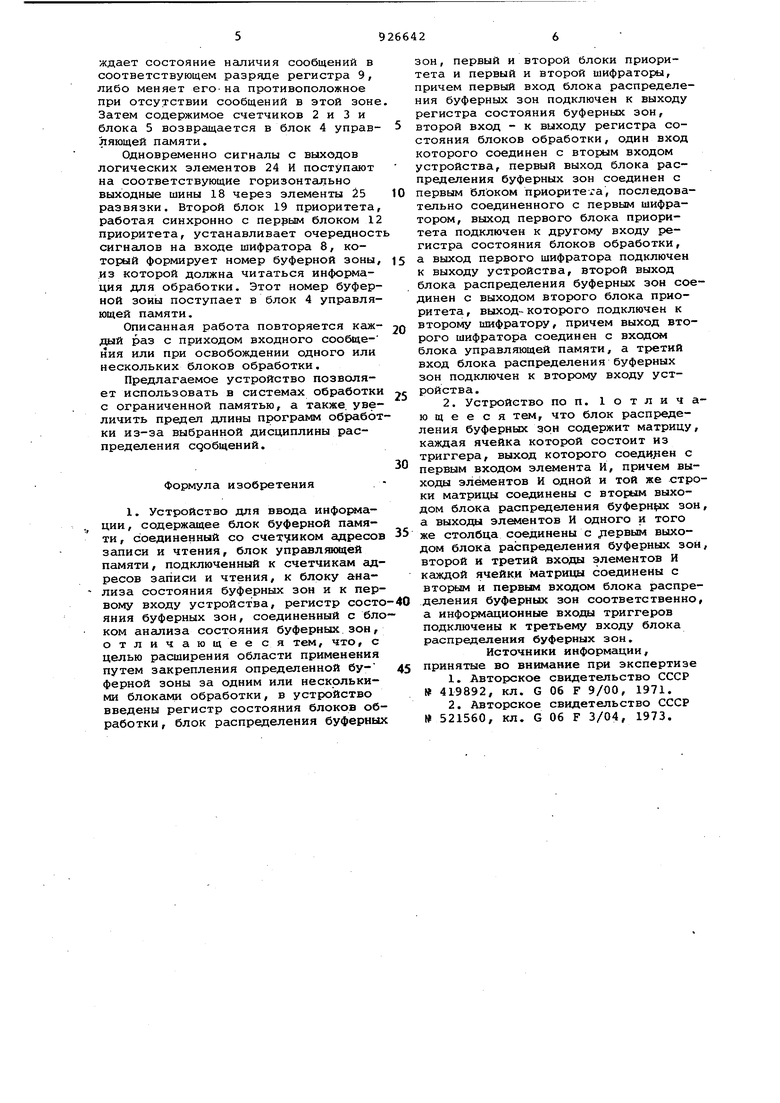

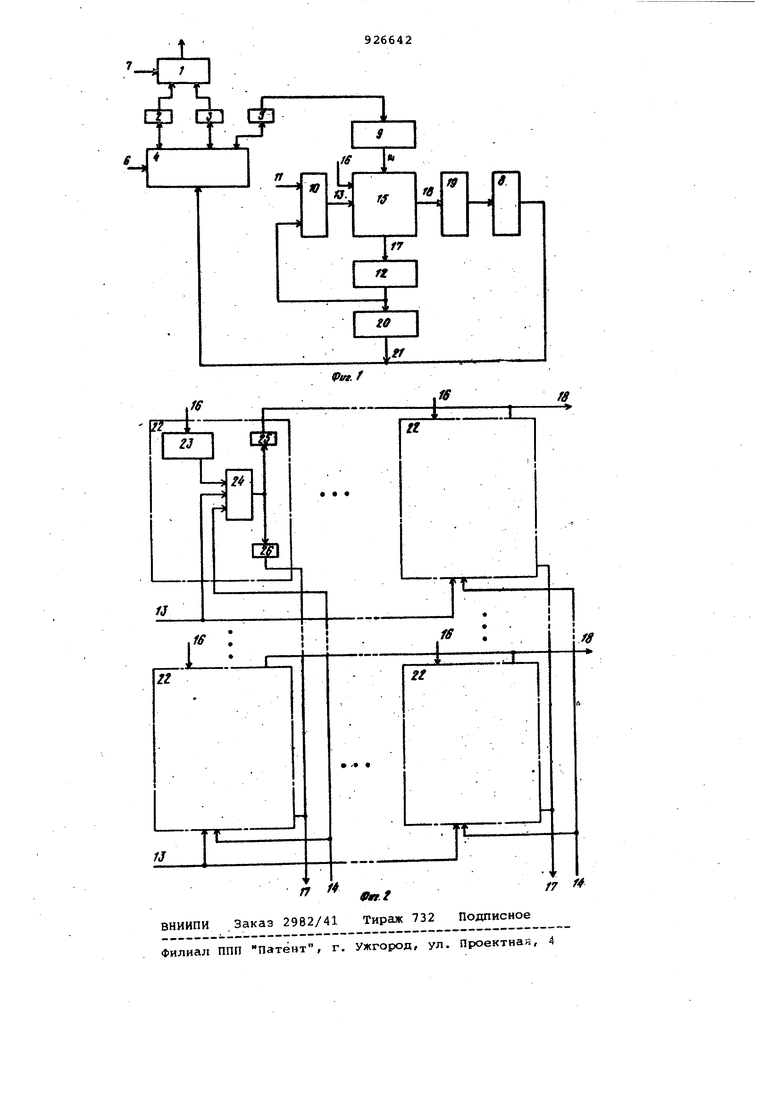

чем первый вход блока распределения буферных зон подключен к выходу регистра состояния буферных зон, втор вход - к выходу регистра состояния блоков обработки, один вход которого соединен с вторым входом устройства, первый выход блока распределе ния буферных зон соединен с первым .блоком приоритета, последовательно соединенного с первым шифратором, выход первого блока приоритета подключей к другому,входу регистра состояния блоков обработки, а выход первого шифратора подключен к выход устройства, второй выход блока распределения буферных зон соединен с выходом второго блока приоритета, выход которого подключен к второму шифратору, причем выход второго шиф ратора соединен с выходом блока управляющей памяти,а третий вход, блок распределения буферных зон подключе к второму входу устройства. Причём блок распределения буферных зон содержит матрицу, каждая ячейка которой состоит из триггера, выход которого соединен с первым входом элемента И, причем выходы элементовИ одной и той же строки матрицы соединены с вторым выходом блока распределениябуферных зон, а выходы элементов И одного и того же столбца соединены с первым выходом блока распределения буферных зон, второй и третий входы элементов И каждой ячейки Матрицы соедине ны с вторым и первым входом распред ления буферных зон соответственно, а информационные входы триггеров подключены к третьему входу блока распределения буферных зон, На фиг. 1 дана схема предлагаемо го устройства; на фиг. 2 - структур ная схема распределения буферных зо Устройство содержит буферную память 1, адресные входы которой соединены со счетчиками 2 адреса записи и 3 адреса чтения, блок 4 управляющей памяти, блок 5 анализа состо яния буферных зон, шины 6 идентификатора входных сообщений, входные шины 7, первый шифратор 8 номера буферной зоны, регистр 9 состояния буферных зон,регистр 10 состояния блоков обработки, шины 11 состояния блоков обработки, первый блок 12 пр оритета, горизонтальные входные шины 13 и вертикальные входные шины 14, блок 15 распределения буферных зон, информационные входы 16, вертикальные выходные шины 17, горизон тальные выходные шины 18, второй блок 19 п| иоритета, шифратор 20, шины 21 номера приемника информации Блок 15 представляет собой матрицу ячеек 22 распределения, число строк которой равно количеству блоков обработки, а число столбцовколичеству буферных зон (фиг. 2). Каждая ячейка У атрицы состоит из триггера 23, логического элемента 24 И, первого элемента 25 развязки и второго элемента 26 развязки. При поступлении на вход 7 устройства информационного сообщения вместе с идентификатором на входе 6, последний попадает в блок 4 управляющей памяти, где используется для выбора соответствующего данному сообщению или группе сообщений управляющего слова. Это управляющее слово загружается в счетчики 2 и 3 и блок 5 анализа состояния буферных зон. В результате формируется адрес ячейки буферной памяти 1, куда записывается данное сообщение, и блок 5 устанавливает соответствующий разряд регистра 9 состояния буферных зон в состояние, соответствующее наличию сообщений в данной буферной зоне. Одновременно сообщение записывается в ячейку блока буферной памяти и содержимое счетчика 2 модифицируется, а затем возвращается в блок управляющей памяти, вместе со счетчиком 3. Если один или несколько блоков обработки свободны, то по шинам 11 в соответствующие разряды регистра 10 записываются признаки Свободно. Эти признаки с выходов регистра 10 в виде единичных потенциалов поступают на горизонтальные входные шины 13 блока 15, -на вертикальные входные шины 14 которого поступают единичные потенциалы признаков наличия сообщений в буферньгх зонах. Единичные потенциалы на шинах 13 опрашивают логические элементы 24 И соответствующих сгрок. Если в триггерах 23 этих строк хранятся признаки закрепления i-той буферной зоны за j-тым блоком обработки., то в соответствующих Вертикальных выходных шинах 17 появляются сигналы, поступающие на входы первого блока 12 приоритета. Первый блок 12 приоритета устанавливает очередность поступления этих сигналов на вход второго шифратора 20, который формирует номер, приемника сообщения, поступающий на шины И, разрешаясоответствующему блоку обработки приема данных, считанных из блока 1 буферной памяти. Одновременно соответствующий разряд регистра 10 устанавливается- в состояние Занято. Этот номер буферной зоны поступает в блок 4 управляющей памяти, откуда выбирается соответствующее управляющее слово, которое, как и ранее, загружается в счетчики 2 и 3 и блок 5, инициируя чтение из выбранной буферной зоны. После модификации содержимого счетчика 3 блок 5 анализа состояния буферных зон либо подтверждает состояние наличия сообщений в соответствующем разряде регистра 9, либо меняет его-на противоположное при отсутствии сообщений в этой зоне Затем содержимое счетчиков 2 и 3 и блока 5 возвращается в блок 4 управляющей памяти. Одновременно сигналы с выходов логических элементов 24 И поступгиот на соответствующие горизонтально выходные шины 18 через элементы 25 развязки. Второй блок 19 приоритета, работая синхронно с перрым блоком 12 приоритета, устанавливает очередност сигналов на входе шифратора 8, который формирует номер буферной зоны, из которой должна читаться информация для обработки. Этот номер буферной зоны поступает в блок 4 управляющей памяти. Описанная работа повторяется каждый раз с приходом входного сообщения или при освобождении одного или нескольких блоков обработки. Предлагаемое устройство позволяет использовать в системах обработки с ограниченной памятью, а также, увеличить предел длины программ обработ ки из-за выбранной дисциплины распределения сдобщений. Формула изобретения 1. Устройство для ввода , дни, содержащее блок буферной памяти, Ьоединенный со счетчиком адресов записи и чтения, блок управляющей памяти, подключенный к счетчикам адресов записи и чтения, к блоку анализа состояния буферных зон и к первому входу устройства, регистр состо яния буферных зон, соединенный с бло ком анализа состояния буферных зон, отличающее ся тем, что, с целью расширения области применения путем закрепления определенной буферной зоны за одним или несколькими блоками обработки, в устройство введены регистр состояния блоков обработки , блок распределения буферных зон, первый и второй блоки приоритета и первый и второй шифраторы, причем первый вход блока распределения буферных зон подключен к выходу регистра состояния буферных зон, второй вход - к выходу регистра состояния блоков обработки, один вход которого соединен с вторым входом устройства, первый выход блока распределения буферных зон соединен с первым блоком приоритета, последовательно соединенного с первым шифратором, выход первого блока приоритета подключен к другому входу регистра состояния блоков обработки, а выход первого шифратора подключен к выходу устройства, второй выход блока распределения буферных зон соединен с выходом второго блока приоритета, выход-которого подключен к второму шифратору, причем выход второго шифратора соединен с входом блока управляющей памяти, а третий вход блока распределения буферных зон подключен к второму входу устройства. 2. Устройство по п. 1отличаю щ е е с я тем, что блок распределения буферных зон содержит матрицу, каждая ячейка которой состоит из триггера, выход которого соеди;1ен с первым входом элемента И, причем выходы элементов И одной и той же строки матрицы соединены с вторым выходом блока распределения буферн дх зон, а выходы элементов И одного и того же столбца соединены с /1ервым выходом блока распределения буферных зон, второй и третий входы элементов И каждой ячейки матрицы соединены с вторым и первым входом блока распределения буферных зон соответственно, а информационные входы триггеров подключены к третьему входу блока распределения буферных зон. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 419892, кл. G 06 F 9/00, 1971. 2.Авторское свидетельство СССР 521560, кл. G 06 F 3/04, 1973.

1± ф ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU995123A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для сопряжения | 1980 |

|

SU903853A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

IS

.

Ш

СЖ

,л

.1.1

7/

JS

/

/

/У

f8

м

Авторы

Даты

1982-05-07—Публикация

1980-03-07—Подача