(5) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Устройство для ввода информации | 1980 |

|

SU926642A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

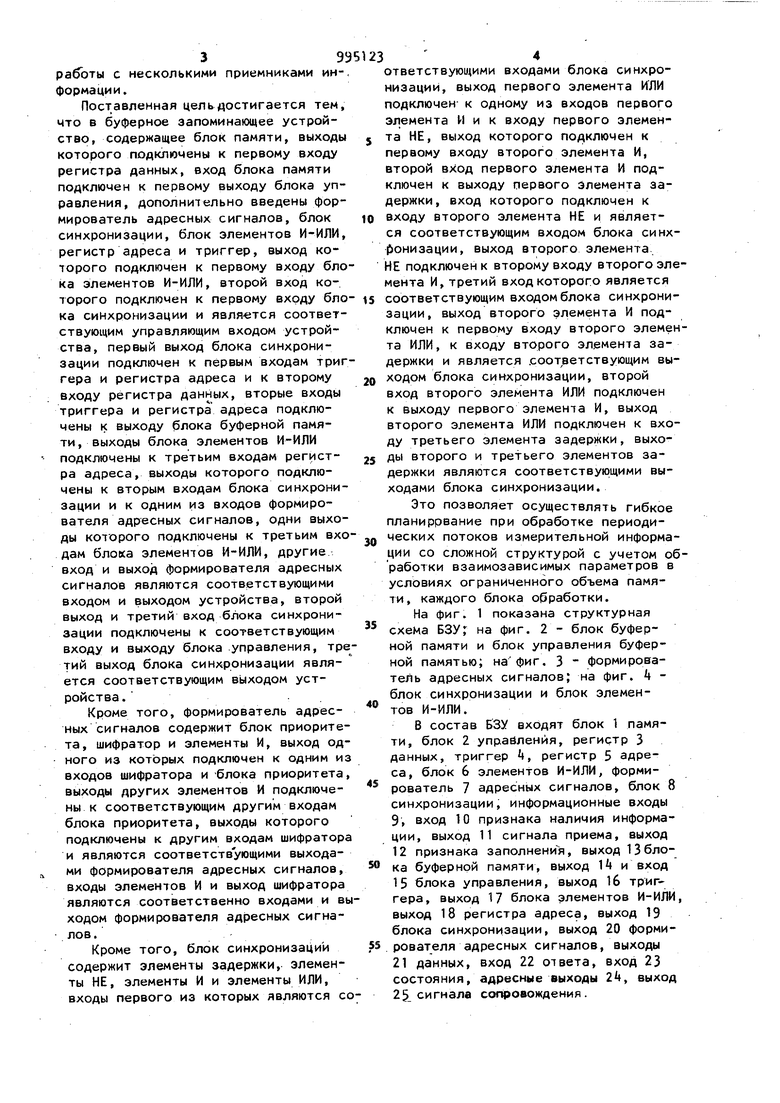

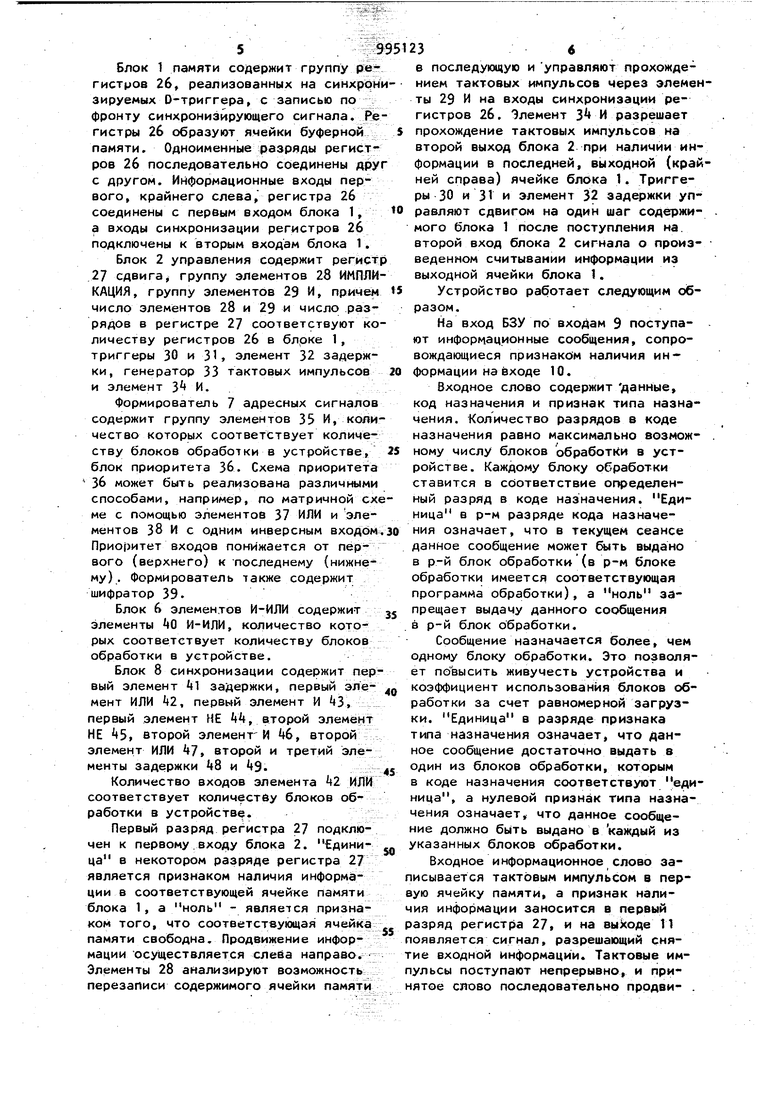

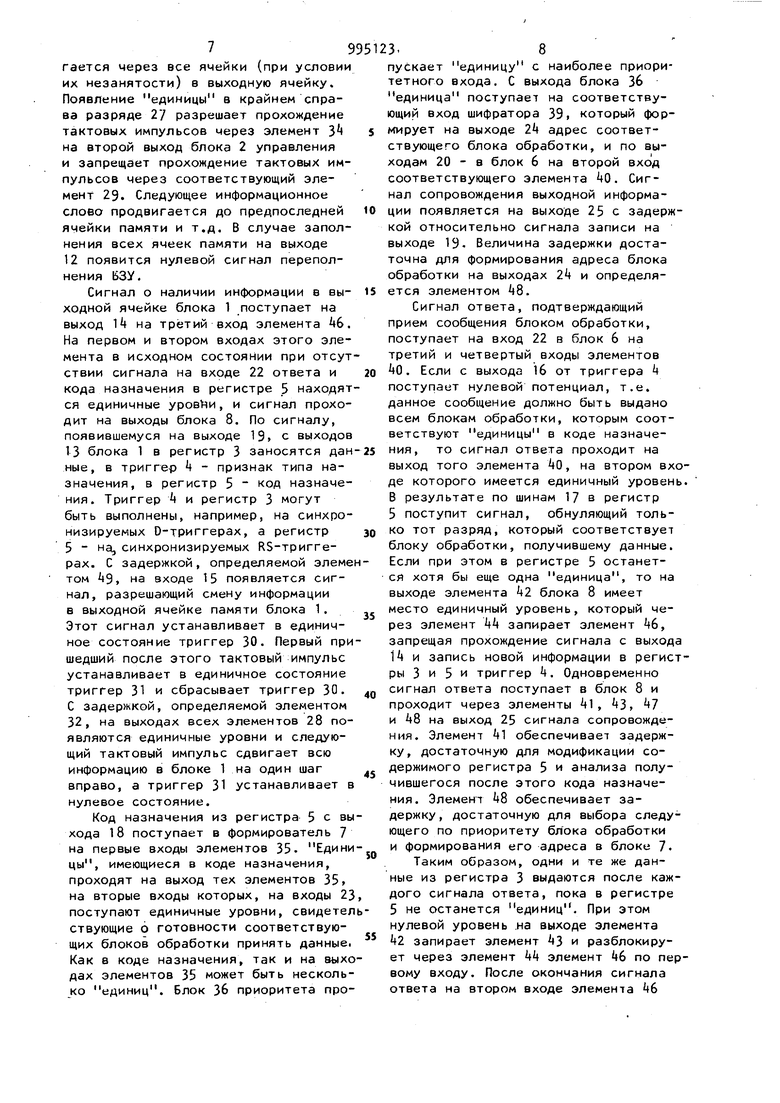

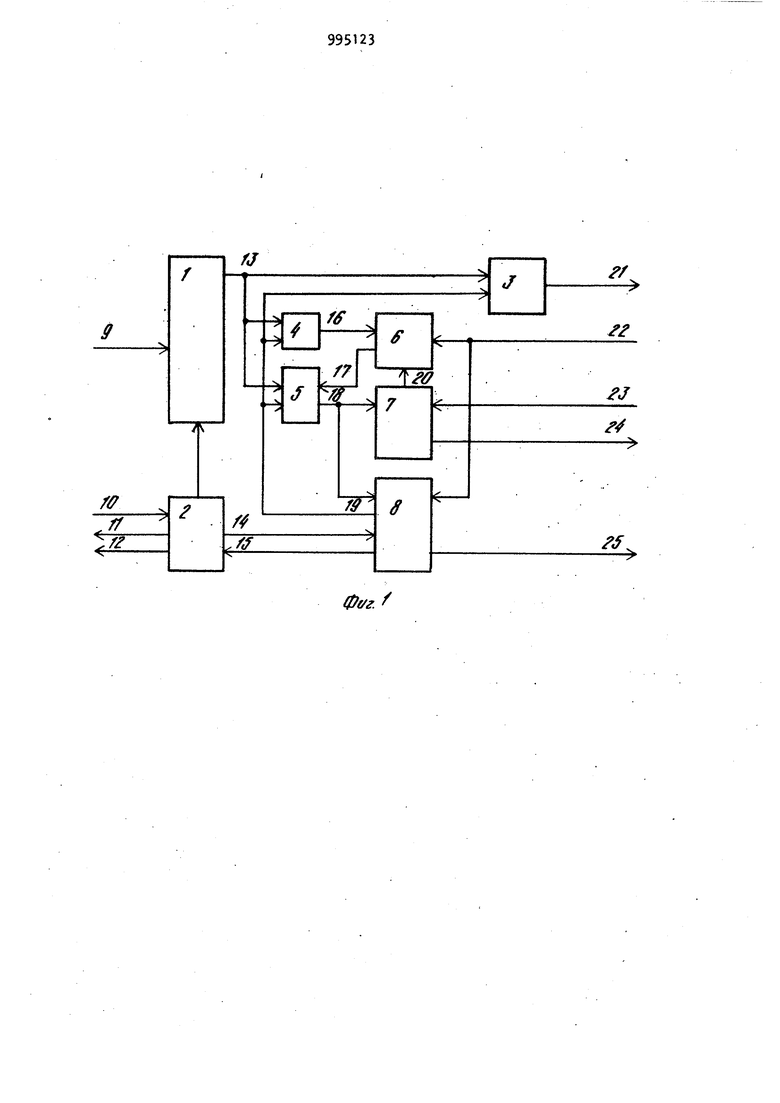

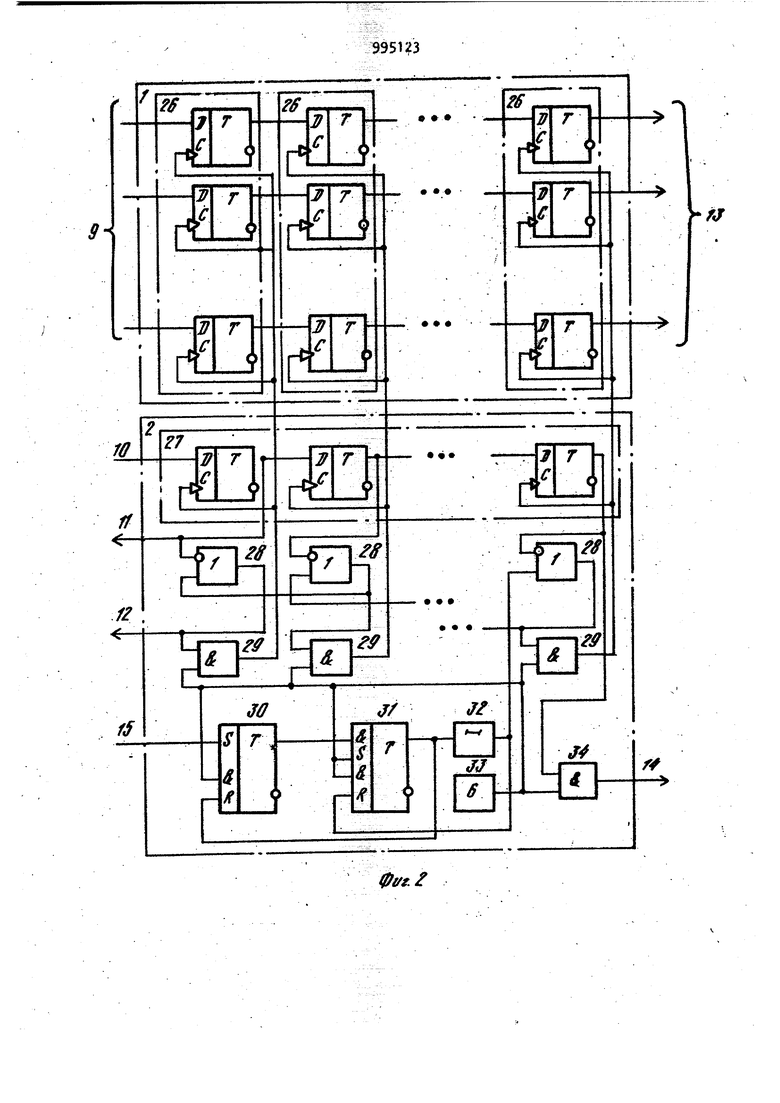

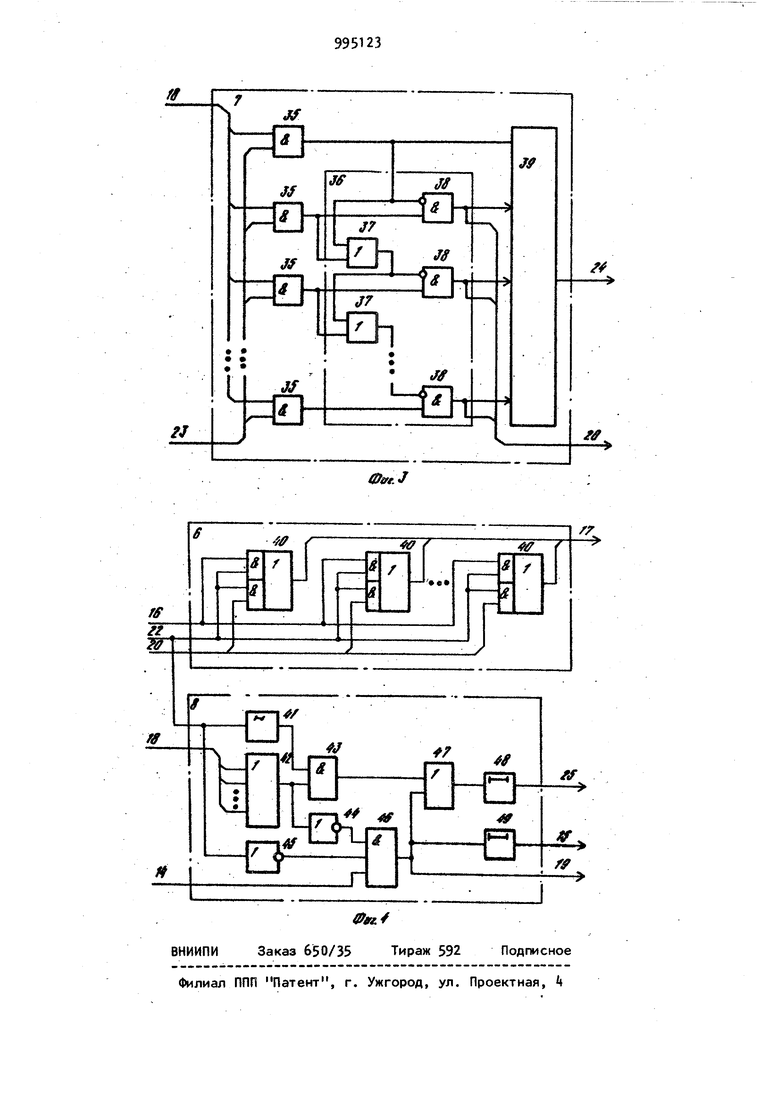

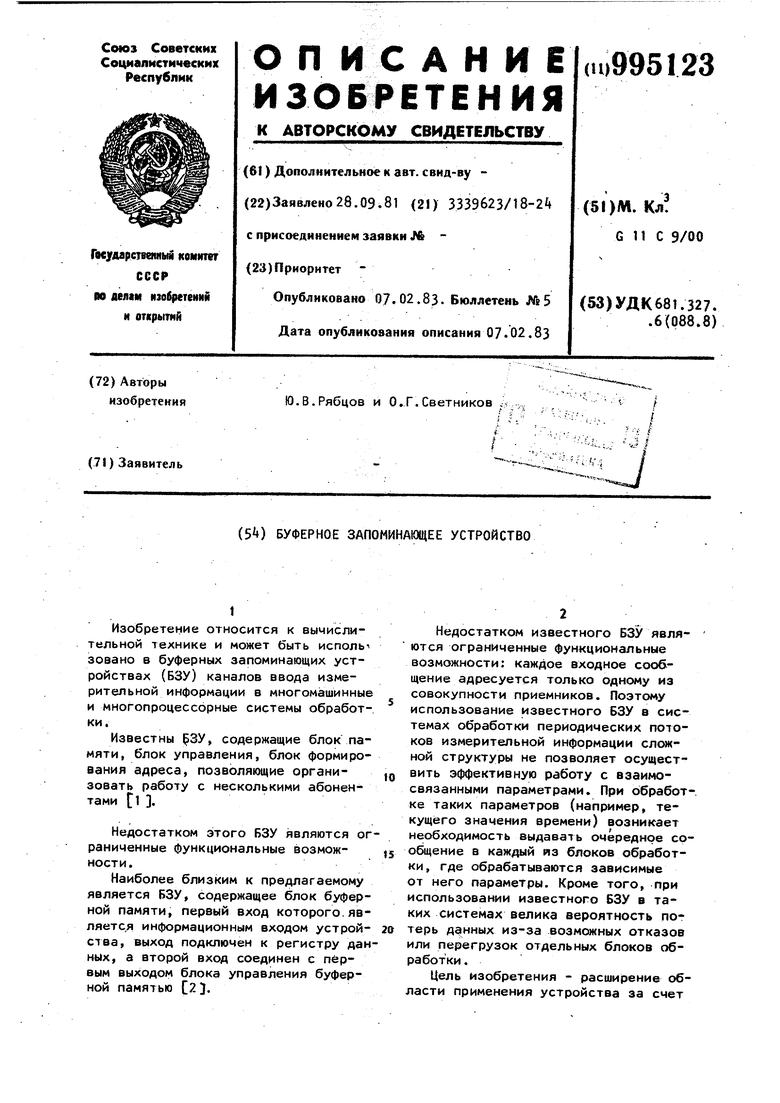

Изобретение относится к вычислительной технике и может быть исполь зовано в буферных запоминающих устройствах (БЗУ) каналов ввода измерительной информации в многомашинные и многопроцессорные системы обработки. Известны ЗУ, содержащие блок памяти, блок управления, блок формирования адреса, позволяющие организовать работу с несколькими абонентами f 1 . Недостатком этого БЗУ являются ог раниченные функциональные возможности. Наиболее близким к предлагаемому является БЗУ, содержащее блок буферной памяти, первый вход которого.являетс,я информационным входом устройства, выход подключен к регистру дан ных, а второй вход соединен с первым выходом блока управления буферной памятью ., Недостатком известного БЗУ являются ограниченные функциональные возможности: каждое входное сообщение адресуется только одному из совокупности приемников. Поэтому использование известного БЗУ в системах обработки периодических потоков измерительной информации сложной структуры не позволяет осуществить эффективную работу с взаимосвязанными параметрами. При обработ-. ке таких параметров (например, текущего значения времени) возникает необходимость выдавать очередное сообщение в каждый из блоков обработки, где обрабатываются зависимые от него параметры. Кроме того, при использовании известного БЗУ в таких системах велика вероятность потерь данных из-за возможных отказов или перегрузок отдельных блоков обработки . Цель изобретения - расширение области применения устройства за счет 9 работы с несколькими приемниками информации. Поставленная цель достигается тем что в буферное запоминающее устройство, содержащее блок памяти, выходы которого подключены к первому входу регистра данных, вход блока памяти подключен к первому выходу блока управления, дополнительно введены формирователь адресных сигналов, блок синхронизации, блок элементов И-ИЛИ регистр адреса и триггер, выход которого подключен к первому входу бло ка элементов И-ИЛИ, второй вход которого подключен к первому вхрду бло ка синхронизации и является соответствующим управляющим входом устройства, первый выход блока синхронизации подключен к первым входам триг гера и регистра адреса и к второму входу регистра данных, вторые входы триггера и регистра адреса подключены к выходу блока буферной памяти, выходы блока элементов И-ИЛИ подключены к третьим входам регистра адреса, выходы которого подключены к вторым входам блока синхронизации и к одним из входов формирователя адресных сигналов, одни выходы которого подключены к третьим вхо дам блока элементов И-ИЛИ, другие вход и выход формирователя адресных сигналов являются соответствующими входом и выходом устройства, второй выход и третий вход блока синхронизации подключены к соответствующим входу и выходу блока управления, тре тий выход блока синхронизации является соответствующим выходом устройства. Кроме того, формирователь адресных сигналов содержит блок приоритета, шифратор и элементы И, выход одного из которых подключен к одним из входов шифратора и блока приоритета выходы других элементов И подключены к соответствующим другим входам блока приоритета, выходы которого подключены к другим входам шифратора и являются соответствующими выходами формирователя адресных сигналов, входы элементов И и выход шифратора являются соответственно входами и вы ходом формирователя адресных сигналов . Кроме того, блок синхронизации содержит элементы задержки, элементы НЕ, элементы И и элементы ИЛИ, входы первого из которых являются со ответствующими входами блока синхронизации, выход первого элемента ИЛИ подключен к одному из входов первого элемента И и к входу первого элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход первого элемента И подключен к выходу первого элемента задержки, вход которого подключен к входу второго элемента НЕ и является соответствующим входом блока синх1 онизации, выход второго элемента НЕ подключен к второму входу второго элемента И, третий вход которого является соответствующим входом блока синхронизации, выход второго элемента И подключен к первому входу второго элемента ИЛИ, к входу второго элемента задержки и является .соот ветствующим выходом блока синхронизации, второй вход второго элемента ИЛИ подключен к выходу первого элемента И, выход второго элемента ИЛИ подключен к входу третьего элемента задержки, выходы второго и третьего элементов задержки являются соответствующими выходами блока синхронизации. Это позволяет осуществлять гибкое планиррвание при обработке периодических потоков измерительной информации со сложной структурой с учетом обработки взаимозависимых параметров в условиях ограниченного объема памяти, каждого блока обработки. На фиг. 1 показана структурная схема БЗУГ на фиг. 2 - блок буферной памяти и блок управления буферной памятью; нафиг. 3 - формирователь адресных сигналов; на фиг. k блок синхронизации и блок элементов И-ИЛИ. В состав БЗУ входят блок 1 памяти, блок 2 упрайленйя, регистр 3 данных, триггер , регистр 5 адреса, блок 6 элементов И-ИЛИ, формирователь 7 адресных сигналов, блок 8 синхронизации, информационные входы 9, вход 10 признака наличия информации, выход 11 сигнала приема, выход 12 признака заполнения, выход 13 блока буферной памяти, выход 1 и вход 15 блока управления, выход 16 триггера, выход 17 блока элементов И-ИЛИ, выход 18 регистра адреса, выход 19 блока синхронизации, выход 20 формирователя адресных сигналов, выходы 21 данных, вход 22 ответа, вход 23 состояния, адресные выходы 2, выход 25 сигнала сопровождения. 59 Блок 1 памяти содержит группу регистров 2б, реализованных на синхрон зируемых D-триггера, с записью по фронту синхронизирующего сигнала. Ре гистры 2б образуют ячейки буферной памяти. Одноименные разряды регистров 26 последовательно соединены дру с другом. Информационные входы первого, крайнего слева, регистра 26 соединены с первым входом блока 1, а входы синхронизации регистров 26 подключены к вторым входам блока 1. Блок 2 управления содержит регист 27 сдвига, группу элементов 28 ИМПЛИ КАЦИЯ, группу элементов 29 И, причем число элементов 28 и 29 и число разрядов в регистре 27 соответствуют ко личеству регистров 26 в блрке 1, триггеры 30 и 31, элемент 32 задержки, генератор 33 тактовых импульсов и элемент З И. Формирователь 7 адресных сигналов содержит группу элементов 35 И, коли чество которых соответствует количеству блоков обработки в устройстве, блок приоритета 36. Схема приоритет-а Зб может быть реализована различными способами, например, по матричной сх ме с помощью элементов 37 ИЛИ и элементов 38 И с одним инверсным входом Приоритет входов понижается от первого (верхнего) к последнему (нижнему) . Формирователь также содержит шифратор 39. Блок 6 элементов И-ИЛИ содержит элементы О И-ИЛИ, количество которых соответствует количеству блоков обработки в устройстве. Блок В синхронизации содержит пер вый элемент k} задержки, первый элемент ИЛИ , первый элемент И , первый элемент НЕ tA, второй элемент НЕ 5, второй элемент-И +6, второй элемент ИЛИ 7, второй и третий элементы задержки 8 и . Количество входов элемента 2 ИЛИ соответствует количеству блоков обработки в устройстве. Первый разряд регистра 27 подключен к первому.входу блока 2. Единица в некотором разряде регистра 27 является признаком наличия информации в соответствующей ячейке памяти блока 1, а ноль - является признаком того, что соответствующая ячейка памяти свободна. Продвижение информации осуществляется слейа направо. Элементы 28 анализируют возможность перезаписи содержимого ячейки памяти 23 В последующую и управляют прохождением тактовых импульсов через элементы 29 И на входы синхронизации регистров 26. Элемент 3 И разрешает прохождение тактовых импульсов на второй выход блока 2 при наличии информации в последней, выходной (крайней справа) ячейке блока 1. Триггеры 30 и 3 и элемент 32 задержки управляют сдвигом на один шаг содержимого блока 1 после поступления на. второй вход блока 2 сигнала о произведенном считывании информации из выходной ячейки блока I. Устройство работает следующим образом. На вход БЗУ по вхоДам 9 поступают информационные сообщения, сопровождающиеся признаком наличия информации на входе 10. Входное слово содержит данные, код назначения и признак типа назначения. Количество разрядов в коде назначения равно максимально возмож- . ному числу блоков обработки в устройстве. Каждому блоку обработки ставится в соответствие определенный разряд в коде назначения. Единица в р-м разряде кода назначения означает, что в текущем сеансе данное сообщение может быть выдано в р-й блок обработки (в р-м блоке обработки имеется соответствующая программа обработки), а ноль запрещает выдачу данного сообщения в р-й блок обработки. Сообщение назначается более, чем одному блоку обработки. Это позволяет повысить живучесть устройства и коэффициент использования блоков обработки за счет равномерной загрузки. Единица в разряде признака типа назначения означает, что данное сообщение достаточно выдать в один из блоков обработки, которым в коде назначения соответствуют единица, а нулевой признак типа назначения означает, что данное сообщение должно быть выдано в каждый из указанных блоков обработки. Входное информационное слово заисывается тактовым импульсом в перую ячейку памяти, а признак налиия информации заносится в первый азряд регистра 27, и на выХоде 11 оявляется сигнал, разрешающий сняие входной информации. Тактовые имульсы поступают непрерывно, и приятое слово последовательно продви- . гается через все ячейки (при условии их незанятости) в выходную ячейку. Появление единицы в крайнем справа разряде 27 разрешает прохождение тактовых импульсов через элемент З на второй выход блока 2 управления и запрещает прохождение тактовых импульсов через соответствующий элемент 29. Следующее информационное слово продвигается до предпоследней ячейки памяти и т.д. В случае заполнения всех ячеек памяти на выходе 12появится нулевой сигнал переполнения ВЗУ. Сигнал о наличии информации в выходной ячейке блока 1 поступает на выход It на третий вход элемента А6. На первом и втором входах этого элемента в исходном состоянии при отсут ствии сигнала на входе 22 ответа и кода назначения в регистре 5 находят ся единичные уровни, и сигнал проходит на выходы блока 8. По сигналу, появившемуся на выходе 19, с выходов 13блока 1 в регистр 3 заносятся дан ные, в триггер - признак типа назначения, в регистр 5 код назначения. Триггер k и регистр 3 могут быть выполнены, например, на синхронизируемых О-триггерах, а регистр 5 на, синхронизируемых RS-триггерах. С задержкой, определяемой элеме том 9 на входе 15 появляется сигнал, разрешающий смену информации в выходной ячейке памяти блока 1. Этот сигнал устанавливает в единичное состояние триггер 30. Первый при шедший после этого тактовый импульс устанавливает в единичное состояние триггер 31 и сбрасывает триггер 30. С задержкой, определяемой элементом 32, на выходах всех элементов 28 появляются единичные уровни и следующий тактовый импульс сдвигает всю информацию в блоке 1 на один шаг вправо, а триггер 31 устанавливает в нулевое состояние. Код назначения из регистра 5 с вы хода 18 поступает в формирователь 7 на первые входы элементов 35. Едини цы, имеющиеся в коде назначения, проходят на выход тех элементов 35 на вторые входы которых, на входы 23 поступают единичные уровни, свидетел ствующие о готовности соответствующих блоков обработки принять данные Как в коде назначения, так и на выхо дах элементов 35 может быть несколько единиц. Блок 36 приоритета пропускает единицу с наиболее приоритетного входа. С выхода блока 36 единица поступает на соответствующий вход шифратора 39. который формирует на выходе адрес соответствующего блока обработки, и по выходам 20 - в блок 6 на второй вхо1д соответствующего элемента 40. Сигнал сопровождения выходной информации появляется на выходе 25 с задержкой относительно сигнала записи на выходе 19. Величина задержки достаточна для формирования адреса блока обработки на выходах 2k и определяется элементом 48. Сигнал ответа, подтверждающий прием сообщения блоком обработки, поступает на вход 22 в блок 6 на третий и четвертый входы элементов 40. Если с выхода 16 от триггера k поступает нулевой потенциал, т.е. данное сообщение должно быть выдано всем блокам обработки, которым соответствуют единицы в коде назначения, то сигнал ответа проходит на выход того элемента 40, на втором входе которого имеется единичный уровень. В результате по шинам 17 в регистр 5 поступит сигнал, обнуляющий только тот разряд, который соответствует блоку обработки, получившему данные. Если при этом в регистре 5 останется хотя бы еще одна единица, то на выходе элемента k2 блока 8 имеет место единичный уровень, который через элемент kk запирает элемент +6, запрещая прохождение сигнала с выхода Н и запись новой информации в регистры 3 и 5 и триггер 4. Одновременно сигнал ответа поступает в блок 8 и проходит через элементы 41, 43, 47 и 48 на выход 25 сигнала сопровождения. Элемент 41 обеспечивает задержку, достаточную для модификации содержимого регистра 5 и анализа получившегося после этого кода назначения. Элемент 48 обеспечивает задержку , достаточную для выбора следующего по приоритету блока обработки и формирования его адреса в блоке 7Таким образом, одни и те же данные из регистра 3 выдаются после каждого сигнала ответа, пока в регистре 5 не останется единиц. При этом нулевой уровень .на выходе элемента 42 запирает элемент 43 и разблокирует через элемент 44 элемент 46 по первому входу. После окончания сигнала ответа на втором входе элемента 46 9 появляется единичный уровень, сигнал с шины 1 проходит на выходы блока 8 и описанный выше процесс повторяется В том случае, когда в триггер k заносится единица, сообщение доста точно выдать только один раз. Первый же сигнал ответа проходит через все элементы 0, так как на их первых входах находится единичный уровень, и обнуляет все разряды регистра 5. Таким образом, предлагаемое БЗУ п зволяет организовать гибкое распреде ление входных сообщений по блокам об .. работки при наличии взаимосвязанных параметров и планировании сеанса обработки в условиях ограниченной памя ти в каждом блоке обработки, т.е. при отсутствии возможности хранить в каждом блоке обработки полный набор программ обработки всей совокупности параметров. Предлагаемое БЗУ позволяет также уменьшить веро.ятность потерь входных данных за счет возможности назначения сообщений более , чем одному блоку обработки. Формула изобретения 1. Буферное запоминающее устройство, содержащее блок памяти выходы которого подключены к первому входу регистра данных, вход блока памяти подключен к первому выходу блока управления, отличающееся тем, что, с целью расширения Области применения у.стройства за счет работы с несколькими приемниками информации оно содержит формирователь адресных сигналов, блок синхронизации, блок элементов И-ИЛИ, регистр адреса и триггер, выход которого подключен к первому входу блока элементов И-ИЛИ, второй вход которого подключен к пер вому входу блока синхронизации и является соответствующим управляющим входом устройства, первый выход блока синхронизации подключен к первым входам триггера и регистра адреса и к второму входу регистра данных, вто рые входы триггера и регистра адреса подключены к выходу блока буферной па мяти, выходы блока элементов И-ИЛИ подключены к третьим входам регистpa адреса, выходы которого подключены к вторым входам блока синхронизации и к одним из входов формирователя адресных сигналов, одни выходы которого подключены к третьим входам блока элементов И-ИЛИ, другие .вход и выход формирователя адресных сигналов являются соответствующими входом и выходом устройства,второй выход и , 310 третий вход блока синхронизации подключены к соответствующим входу и выходу блока управления, третий выход блока синхронизации является соответствующим выходом устройства. 2.Устройство по п. 1, отличающееся тем, что формирователь адресных сигналов содержит блок приоритета, шифратор и элементы И, выход одного из которых подключен к одним из входов шифратора и блока приоритета, выходы других элементов И подключены к соответствующим другим входам блока приоритета, выходы которого подключены к другим входам шифратора и являются соответствующими выходами формирователя адресных сигналов, входы элементов И и выходшифратора являются соответственно входами и выходом формирователя адрес, ных сигналов. 3.Устройство по п. 1, отличающееся тем, что блок синхронизации содержит элементы задержки, элементы НЕ, элементы И и элементы ИЛИ, входы первого из которых являются соответствующими входами блока синхронизации, выход первого элемента ИЛИ подключен к одному из входов первого элемента И и к входу первого элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход первого элемента И подключен к выходу первого элемента задержки, вход которого подключен к входу второго элемента НЕ и является соответствующим входом блока синхронизации, выход второго элемента НЕ подключен к второму входу второго элемента И, третий вход которого является соответствующим входом блока синхронизации, выход второго элемента И подключен к первому входу второго элемента ИЛИ, к входу.второго элемента задержки и является соответствующим выходом блока синхронизации, второй вход второго элемента ИЛИ подключен к выходу первого элементу И, выход второго элемента ЛИ подключен к входу третьего элемента адержки ,выходы второго и третьего эле-, ентов задержки являются соответствующими выходами блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 705517, кл G 11 С 19/00, 1977. 2.Авторское свидетельство СССР f 769620, кл. G 11 С 19/00, 1978 (прототип).

Фе/г.

9-

лг

Iff.

Авторы

Даты

1983-02-07—Публикация

1981-09-28—Подача