I

Изобретение относится к радиолокации и технике связи и может использоваться в устройствах измерения частоты радиоимпульсных сигналов, отраженных от протяженных объектов, например метеорбразований.

Известен частотный дискриминатор, содержащий ограничитель, генератор, фазовращатель и первый и второй каналы, каждый из которых содержит первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок памяти, второй перемножитель и блок сложения, при этом выход ограничителя соединен с первыми входами фазовых детекторов первого и второго каналов, выход генератора соединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом фазового детектора первого канала через фазовращатель, выход блока памяти первого канала соединен через

лервый перемножитель первого канала с вторым входом блока сложения второго канала, а выход блока памяти второго канала соединен через первый перемножитель второго канала с вторым входом блока сложения первого канала 11 .

Однако известный частотный дискриминатор имеет низкую чувствительность .

10

Цель изобретения - увеличение чувствительности.

Для достижения цели в частотный дискриминатор, содержащий ограничитель, генератор, фазовращатель и

IS первый и второй каналы, каждый из которых содержит первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок

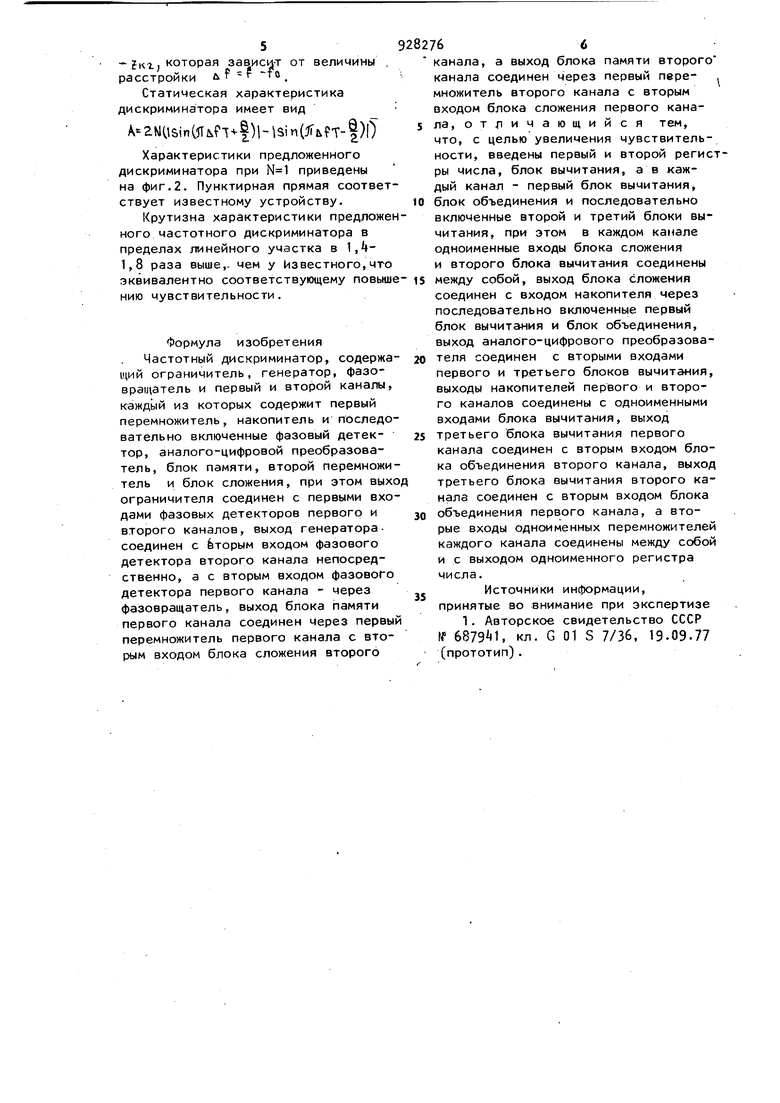

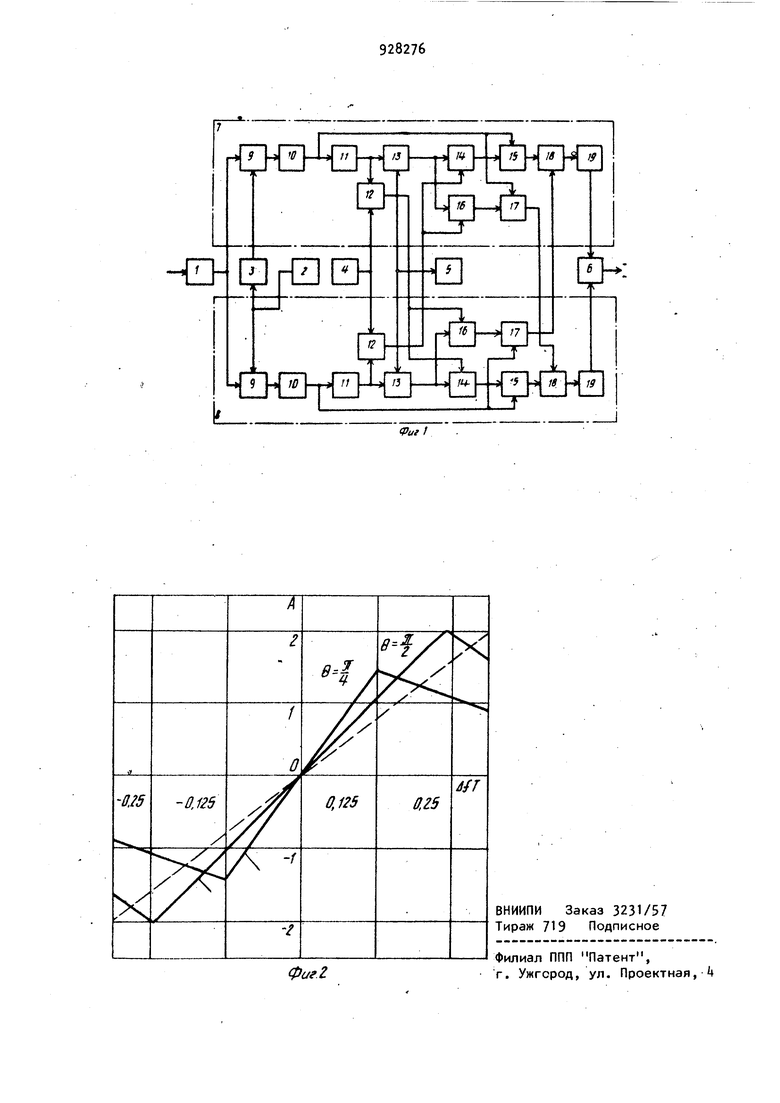

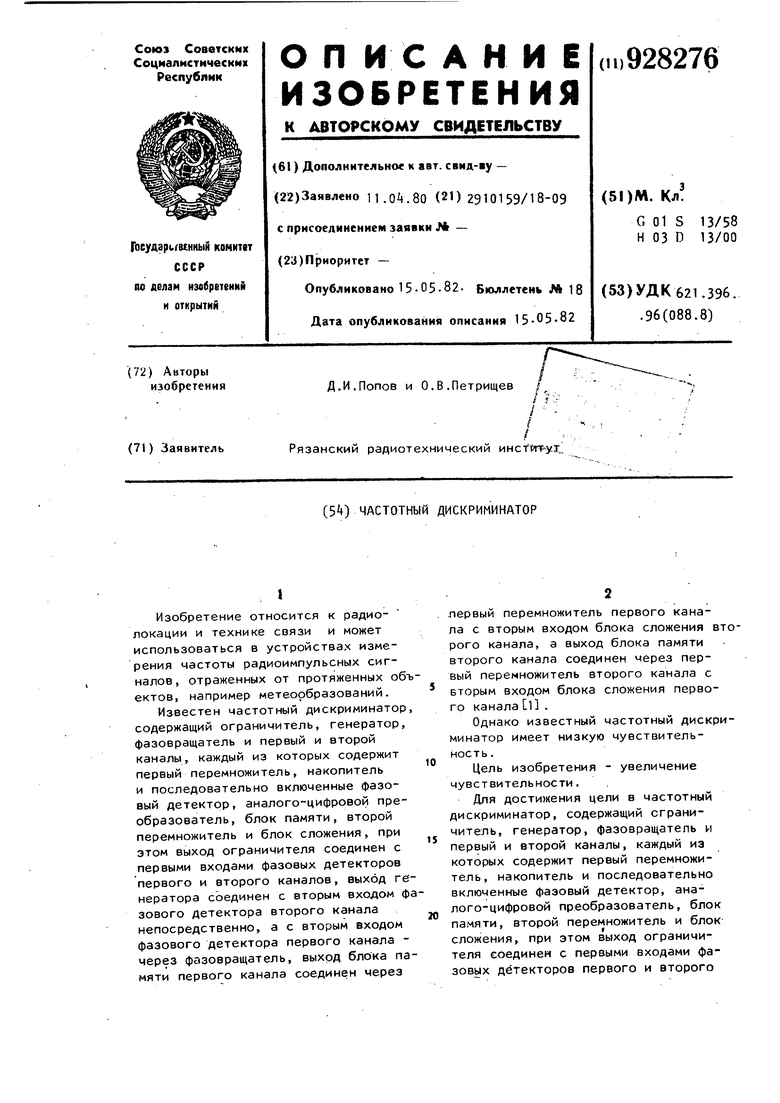

20 памяти, второй перемножитель и блок сложения, при этом выход ограничителя соединен с первыми входами фазовых детекторов первого и второго 3 каналов, выход генератора соединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом фазового детектор первого канала - через фазовращатель, выход блока памяти первого канала соединен через первый перемножитель первого канала с вторым входом блока сложения второго канала, а выход блока памяти второго канала соединен через первый перемн житель второго канала с вторым входом блока сложения первого канала, введены первый и второй регистры числа, блок вычитания, а в каждый I канал - первый блок вычитания, блок объединения и последовательно включенные второй и третий блоки вычита ния, при этом в каждом канале одноименные входы блока сложения и второго блока вычитания соединены межд собой, выход блока сложения соединен с входом накопителя через после довательно включенные первый блок в читания и блок объединения, выход аналого-цифрового преобразователя соединен с вторыми входами первого и третьего блоков вычитания, выходы накопителей первого и второго канал соединены с одноименными входами блока вычитания, выход третье о бло ка вычитания первого канала соедине с вторым входом блока объединения второго канала, выход третьего блока вычитания второго канала соединен с вторым входом блока объединения первого канала, а вторые входы одноименных перемножителей каждого канала соединены между собой и с вы ходом одноименного регистра числа. На фиг. 1 приведена структурная электрическая схема устройства, на фиг. 2 - статическая характеристика предложенного устройства (/sf Т- н мированная величина расстройки часто ть},) . Частотный дискриминатор содержит ограничитель 1, генератор 2, фазовращатель 3, первый и второй регистры и 5 числа, блок 6 вычитания, первый и второй каналы 7 и 8, каждый из которых содержит фазовый детектор 9, аналого-цифровой преобр зователь 10, блок 11 памяти, первый перемножитель 12, второй пере множитель 13, блок 14 сложения, пер вый, второй и третий блоки 15-17 вычитания, блок 18 объединения и на копитель 19Частотный дискриминатор работает следующим образом. Сигналы от протяженных объектов с несущей частотой F поступают на вход ограничителя 1, в котором происходит сжатие динамического диапазона исходных сигналов. Квадратурные составляющие сигнала с выхода фазовых детекторов 9 поступают в аналогоцифровые преобразователи 10, где квантуются по времени, и амплитуде. При этом на вторые входы фазовых детекторов 9 от генератора 2 непосредственно и через фазовращатель 3 поступает сигнал опорной частоты fo . Задержанные в блоках 11 памяти на интервал Т цифровые коды квадратурных составляющих х. (первый канал 7} , УК-Т (второй канал 8) поступают на первые входы первого и второго перемножителей 12 и 13. В первом и втором регистрах и 5 числа хранятся значения соответственно 51п8и cosQ В результате выполнения операций в первом и втором перемножителях 12 и 13 и блоке 14 сложения и втором блоке 16 вычитания происходит двумерный поворот квадратурных составляющих на углы - 0 и 9 .В первом и третьем блоках 15 и 17 вычитания данные составляющие вычитаются из незадержанных квадратурных составляющих XR, и y, поступающих непосредственно с выходов аналого-цифровых преобразователей 10. В результате на входах каждого блока 18 объединения образуются соответственно величиныURI Хн,-СЛк,н COSe- y K--I Sin0)j 1)м Ук-(УкН COSe-Av -i Slnd) для первого канала 7 и икг «.-( С0«9 -Ук-,), , 1)к2-Ук-(Ук-1С059 ) для второго канала 8. 3 блоках 18 объединения осуществляется вычисление величины для первого канала 7 voy: ь г 2для второго канала 8. В накопителях 19 производится накопление данных с N смежных элементов разрешения по дальности, что позволяет сгладить флюктуации поступающих сигналов и снизить влияние внутренних шумов приемника. После вычитания на выходе блока 6 образуется величина

гкг, которая зависит от величины . расстройки f ,

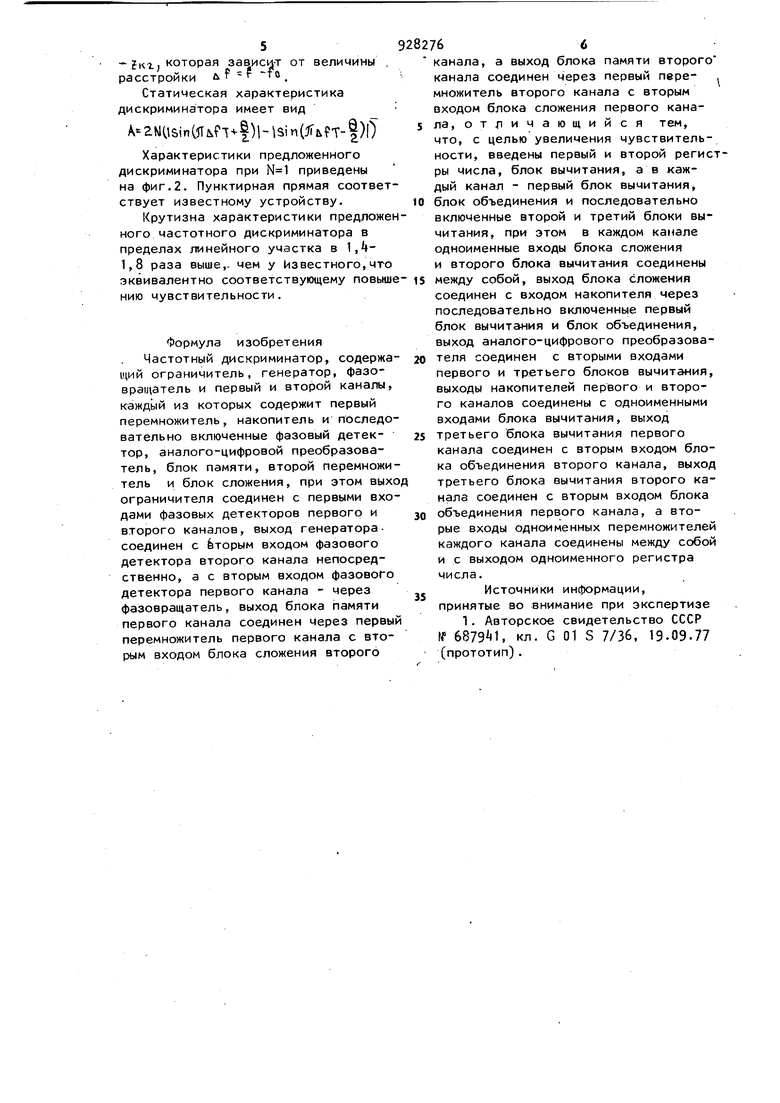

Статическая характеристика дискриминатора имеет вид

гNOsin()()lУ

Характеристики предложенного дискриминатора при приведены на фиг.2. Пунктирная прямая соответствует известному устройству,

Крутизна характеристики предложенного частотного дискриминатора в пределах линейного участка в l,,8 раза выше,- чем у Известного, что эквивалентно соответствующему повышению чувствительности.

1)ормула изобретения Частотный дискриминатор, содержащий ограничитель, генератор, фазовраи(атель и первый и второй каналы, каждый из которых содержит первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок памяти, второй перемножитель и блок сложения, при этом выхо ограничителя соединен с первыми входами фазовых детекторов первого и второго каналов, выход генераторасоединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом фазового детектора первого канала - через фазовращатель, выход блока памяти первого канала соединен через первый перемножитель первого канала с вторым входом блока сложения второго

канала, а выход блока памяти второго канала соединен через первый перемножитель второго канала с вторым входом блока сложения первого канала, отличающийся тем, что, с целью увеличения чувствительности, введены первый и второй регисры числа, блок вычитания, а в каждый канал - первый блок вычитания, блок объединения и последовательно включенные второй и третий блоки вычитания, при этом в каждом канале одноименные входы блока сложения и второго блока вычитания соединены между собой, выход блока сложения соединен с входом накопителя через последовательно включенные первый блок вычитания и блок объединения, выход аналого-цифрового преобразователя соединен с вторыми входами первого и третьего блоков вычитания, выходы накопителей первого и второго каналов соединены с одноименными входами блока вычитания, выход третьего блока вычитания первого канала соединен с вторым входом блока объединения второго канала, выход третьего блока вычитания второго канала соединен с вторым входом блока объединения первого канала, а вторые входы одноименных перемножителей каждого канала соединены между собой и с выходом одноименного регистра числа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР (f , кл. G 01 S 7/36, 19.03-77 (прототип).

JTiff

n

3-УЧИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный дискриминатор | 1981 |

|

SU1059661A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| СПОСОБ СОПРОВОЖДЕНИЯ ЦЕЛИ МОНОИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ | 1997 |

|

RU2117960C1 |

| Цифровой частотный дискриминатор | 1978 |

|

SU780153A1 |

| Устройство для подавления пассивных помех | 1976 |

|

SU578781A1 |

| Селектор эхо-сигнала движущихся целей для двухчастотного радиолокатора | 1984 |

|

SU1841292A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1977 |

|

SU778514A2 |

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУХКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2009 |

|

RU2427969C1 |

| Устройство для подавления пассивных помех | 1977 |

|

SU687941A2 |

| Устройство приема сигналов с двукратным разнесением | 1983 |

|

SU1092741A1 |

w

1

ri«

Авторы

Даты

1982-05-15—Публикация

1980-04-11—Подача