2. Дискриминатор по п.1, о т личающийс.я тем, что блок усреднения содержит N -J последовательно соединенных сумматоров, N-1 последовательно соединенных блоков задержки, .блок нормировки и блок памяти, причем первый вход первого сумматора и вхрд первого блока задержки объединены.и являются входом блока усреднения, выход каждого блока задержки соединен с вторым входом соответствующего сумматора, выход N-1-го сумматора соединен с первым входом блока нормировки, выход которого является выходом блока усреднения ,при этом второй вход блока нормировки соединен с выходом блока памяти ,а управляющие входы каждого блока задержки объединены и являются управляющим входом блока усреднения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2313184C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНЫХ УСТРОЙСТВ ПО НЕСУЩЕЙ И ТАКТОВОЙ ЧАСТОТАМ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ В УСЛОВИЯХ БОЛЬШОЙ НЕСТАБИЛЬНОСТИ ЧАСТОТ В КАНАЛЕ СВЯЗИ | 2011 |

|

RU2450446C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| Частотный дискриминатор | 1980 |

|

SU928276A1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

1.ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР, содержжций генератор опорной частоты, фазовращатель, генератор синхрониэируитих импульсов, ограиичитель и два измерительных канала, каждый из которых содержит последовательно соединенные фазовый детектор и аигиюго-цифровой преобразователь и последовательно соединенные первый блок задержки, первый перемножитель и первый сумматор, а также второй пе| емножитель н первый блок усреднения, причем первые, входы фазовых детекторов каждого канала соединены с выходом ограничителя, вход которого является входом цифрового частотного дискриминатора, вторые входы фазовых детекторов непосредственно и через фазовращатель соединены с генератором опорной частоты, управляющие входы аналогоцифровых преобразователей соединены С генератором синхронизирующих нмпульоо, а выход первого блока задержки каждого НАнала чер€1 п«р«множит«лъ оовдйн«н с вторым входом первого сумматора другого канала, отличающийся тем, что, с целью увеличения чувствительности, в него введены первый. второй и третий регистры числа и блок вычитания, а в каждый кангш третий перахножитель, второй сумматор, блок обработки сигналов, второй блок усреднения, четвертый перемножитЁль и последовательно включенные второй блок задержки, пятый перемножитель, третий сумматор, шестой перемиожитель и четвертый cjnotaTop, причем выход аналого-цифрового пр еобразователя в каждом канале соединен с первьвл входом второго и четвертого сумматоров, выход второго сумматора соединен с входом первого блока задержки и через первый бЛок усреднения с первым входом блока обработки сигналов, выход четвертого сумматора соединен с входом , второго блока з.гшержкн и через второй блок усреднення с вторым входом блока обработкн сигналов другого канала, выход первого сумматора через третий перемножнтель соединен с вторым входом второго сумматора, выход второго блока- задержки через четвертый перемножитель соединён с вторым входом третьего сумматора другого канала, выход первого регистра числасоединен с втосл рыми входами третьего и шестого ю ф .перемножителей каждого канг1ла, выход второго регистра чнсла - с вторыми входамипервого и пятого переОд множителей, выход третьего регистра чнсла -; с вторыми входами второго и четвертого перемножителей каждого канала,, при зтом выход генератора синхронизирующих импульсов соединен с управляющими входами первого и второго блоков задержки, перяого и BTOpoi-o блоков уереднеиня каждого канала а выхода блоков обработки сигналов каждого канала совднноны е входакш блока вычитания, выход которого является выходом цифрового частотного ди-, скрими атора.

1

Изобретение относится к ргщиотехнике и может использоваться в цифровых устройствах измерения частоты.

Известен цифровой частотный дискриминатор, содержащий ограничитель, генератор опорной частоты,, фазовращатель, реверсивный счетчик и два канала, каждый из которых содержит фазовый детектор и логические элементы цифровой техники l .

Однако цифровой частотный дискриминатор имеет низкую разрешающую способность.

Наиболее близким к предлагаемому по технической сущности является цифровой частотный дискриминатор/ сдержащий генератор опорной частоты, фазовращатель, генератор синхронизирующих импульсов, ограничитель и два измерительных канала, каждый из которых содержит последовательно соединенные фазовый детектор и аналого-цифровой .преобразователь и последовательно соединенные первый блок задержки, первый перемножителЬ и первый сумматор, а также второй перемножитель и первый блок усреднения, причем первые входы фазовых детекторов каждого канала соединены с выходом ограничителя, вход котрого является входом цифрового частотного дискриминатора, вторые входы фазовых детекторов непосредственно и через фазовращатель соединены с генератором опорной частоты, управляющие входы аналого-цифровых преобразователей соединены с генератором синхронизирующих импульсов, а выход первого блока задержки каждого канала через второй перемножитель соединен с вторым входом первого сумматора другого канала, причем выходы каждого канала подключены к соответствующим входам решающего блока, выход которого является выходом цифрового частотного дискриминатора 2J .

Однако известный цифровой частотный дискриминатор имеет недостаточную чувствительность.

Цель изобретения - увеличение чувствительности.

Для достижения цели в цифровой частотный дискриминатор, содержащий генератор опорной частоты, фад зовращатель, генератор синхронизирующих импульсов, ограничитель и два измерительных канала, каждый из которых содержит последовательно соединенные фазовый детектор и аналого-цифровой преобразователь и последовательно соединенные первый блок задержки, первый перемножитель и первый сумматор, а также второй перемножитель и первый блок усреднения, причем первые входы фазовых

детекторов каждого канала соединены с выходом ограничителя, вход ко; торого является входом цифрового частотного дискриминатора, вторые входы фазовых детекторов непосред5 ственно и через фазовращатель соединены с генератором опорной частоты, управляющие входы аналого-цифровых преобразователей соединены с генератором синхронизирующих им0 пульсов, а выход первого блока задержки каждого канала через второй перемножитель соединен с вторым входом первого сумматора другого канала, введены первый, второй и

5 третий регистры числа и блок вычитания, а в каждый канал - третий перемножитель, второй сумматор, блок обработки сигналов, второй блок усреднения, четвертый перемножитель и последовательно включенные второй блок задержки, пятый перемножитель, третий сумматор, шестой перемножитель и четвертый сумматор, причем выход аналого-цифрового преобразователя в каждом канале соединен

5 с первым входом второго и четвертого сумматоров, выход второго сумматора соединен с входом первого блока задержки и через первый блок .

усреднения с первым входом блока обработки сигналов, выход четвдртого сумматора соединен с входом второго блока задержки и через второй блок усреднения с вторым входом блока обработки сигналов другого канала, выход первого сумматора через третий перемножитель соединен с вторым входом второго сумматора, выход второго блока задержки через четвертый перемножитель соединен с вторым входом третьего сумматора другого канала, выход первого регистра числа соединен с вторыми входами третьего и шестого перемножителей каждого канала, выход второго регистра числа - с вторыми входами ггервого и пятого перемножителей, выход третьего регистра числа - с вторыми входами второго и четвертого перемножителей каждого канала, при этом выход генератора синхронизирующих импульсов соединен с управляющими входами первого и второго блоков задержки, первого и второго блоков усреднения каждого канала, а выходы блоков обработки сигналов каждого канала соединены с входами блока вычитания, выход которого является выходом цифрового частотного дискриминатора.

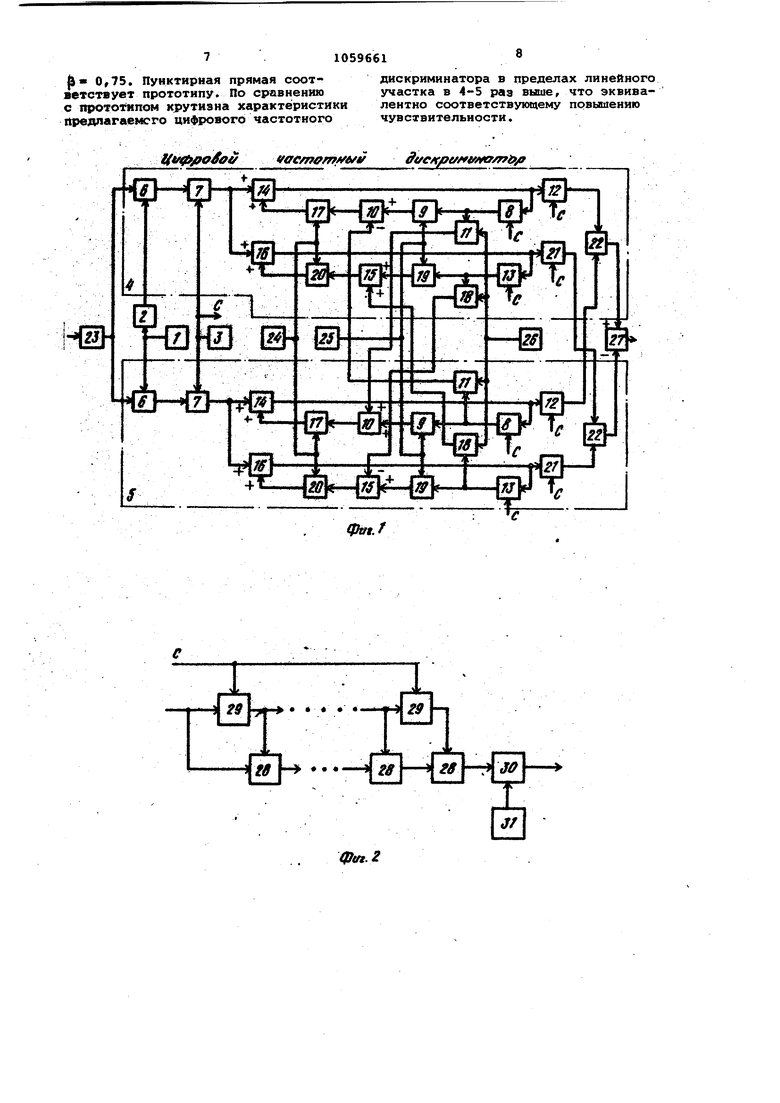

Кроме того, .блок усреднения содержит N-1 последовательно соединенных сумматоров, N-1 последовательно соединенных блоков задержки блок нормировки и блок памяти, причем первый вход первого сумматора и вход первого блока задержки объединены и являются входом блока усреднения, выход каждого блока задержки соединен с вторымвходом сооветствующего сумматора, (N-1)го сумматора соединен с первым входом блока нормировки, выход которого является выходом блока усреднения, при этом второй вход блока норлшровки соединен с выходом блока памяти, а управляющие входы каждого блока згщержки объединены и являются управляющим входом блока усреднения.

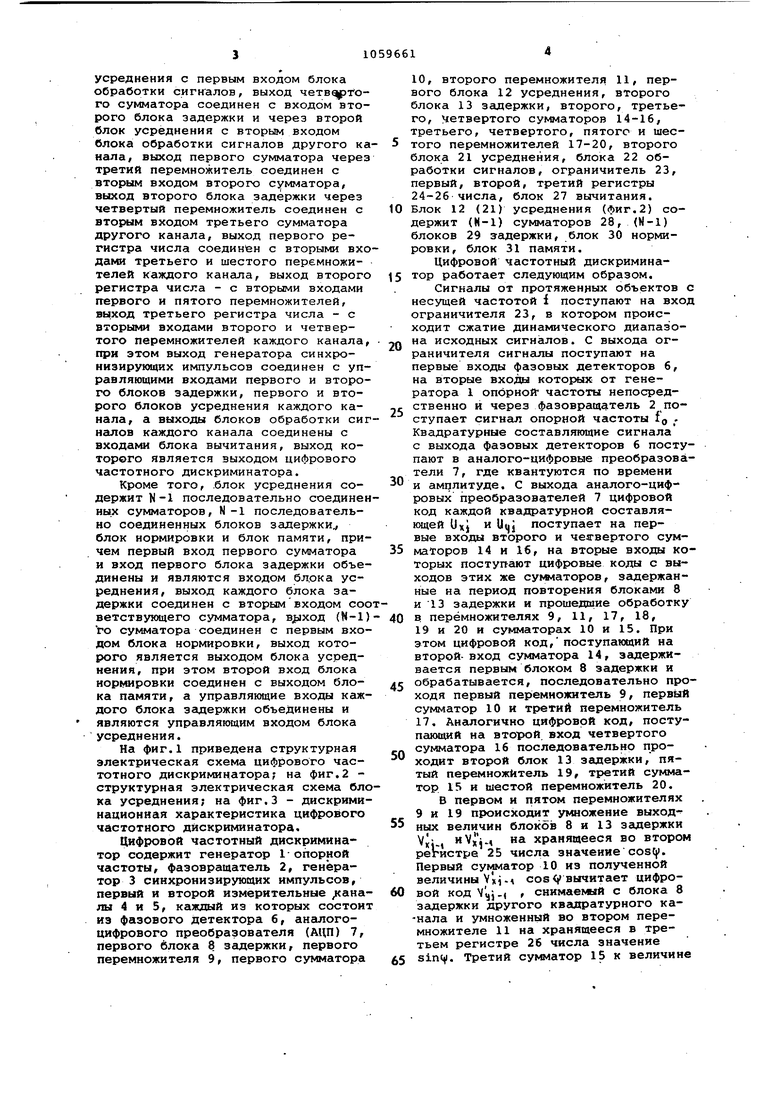

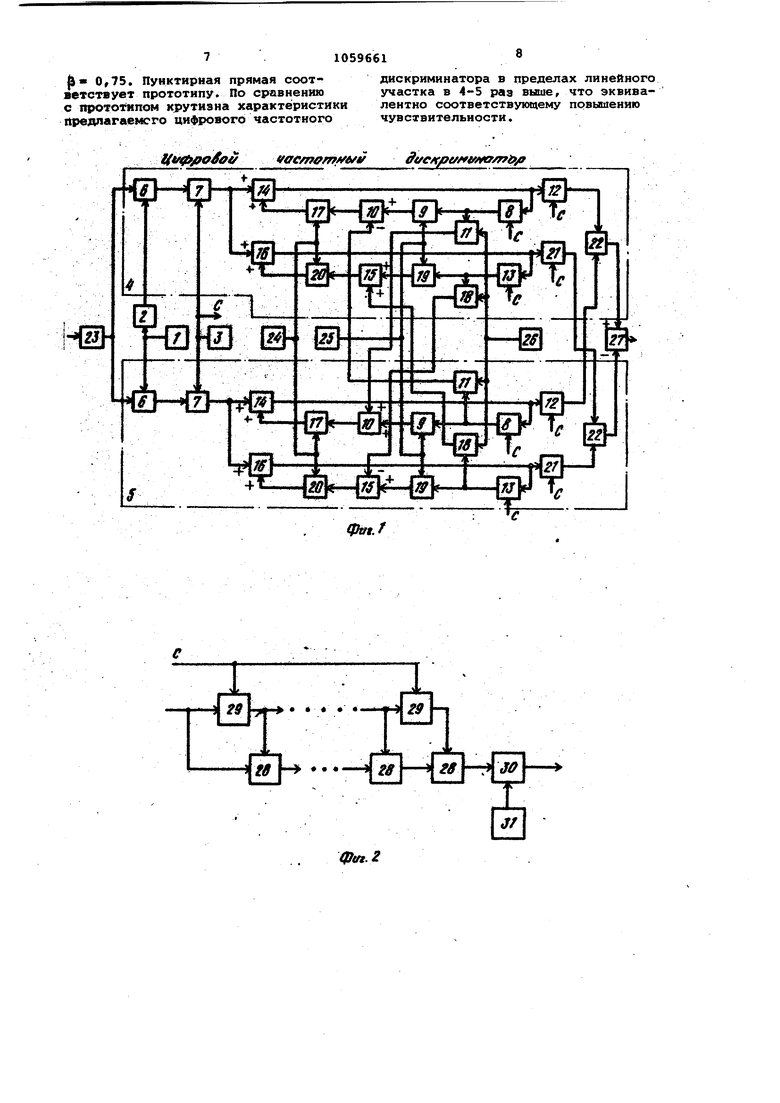

На фиг.1 приведена структурная электрическая схема цифрового частотного дискриминатора; на фиг.2 структурная электрическая схема блока усреднения; на фиг.З - дискриминационная характеристика цифрового частотного дискриминатора.

Цифровой частотный дискриминатор содержит генератор 1-опорной частоты, фазовращатель 2, генератор 3 синхронизирующих импульсов, первый и второй измерительные аналы 4 и 5, каждый из которых состоит из фазового детектора б, аналогоцифрового преобразователя (АЦП) 7, первого блока 8 задержки, первого перемножителя 9, первого сумматора

10, второго перемножителя 11, первого блока 12 усреднения, второго блока 13 задержки, второго, третьего, четвертого сумматоров 14-16, третьего, четвертого, пятого и шестого перемножителей 17-20, второго блока 21 усреднения, блока 22 обработки сигналов, ограничитель 23, первый, второй, третий регистры 24-26-числа, блок 27 вычитания.

0 Блок 12 (21) усреднения (фиг.2) содержит (Н-1) сумматоров 28, (Н-1) блоков 29 задержки, блок 30 нормировки, блок 31 памяти.

Цифровой частотный дискримина5 тор работает следующим образом.

Сигналы от протяженных объектов с несущей частотой i поступают на вход ограничителя 23, в котором происходит сжатие динамического диапазона исходных сигналов. С выхода ограничителя сигналы поступают на первые входы фазовых детекторов 6, на вторые входы котор ис от генератора 1 опорной- частоты непосред, ственно и через фазовращатель 2 поступает сигнал опорной частоты f . Квадратурные составляющие сигнала с выхода фазовых детекторов 6 поступают в аналого-цифровые преобразователи 7, где квантуются по времени

0 и амплитуде. С выхода аналого-цифровых преобразователей 7 цифровой код каждой квадратурной составляющей Uxj и U(jJ поступает на первые входы второго и чедгвертого сум5 маторов 14 и 16, на вторые входы которых поступают цифровые коды с выходов этих же сумматоров, згшержанные на период повторения блоками 8 и 13 задержки и прошедшие обработку

0 в перёмножителях 9, 11, 17, 18, 19 и 20 и сумматорах 10 и 15. При этом цифровой код, поступающий на второй-вход сумматора 14, задерживается первым блоком 8 задержки и

c обрабатывается, последовательно проходя первый перемиожитель 9, первый сумматор 10 и третий перемножитель 17. Анешогично цифровой код, поступгиощий на второй вход четвертого сумматора 16 последовательно проходит второй блок 13 задержки, пятый перемножйтель 19, третий сумматор 15 и шестой перемножитель 20.

В первом и пятом перемножителях 9 и 19 происходит умножение выход5 ных величин блоков 8 и 13 задержки Vi;., wVx., на хранящееся во втором регистре 25 числа значение созср. Первый сумматор 10 из полученной величины УИ-Л cosVвычитает цифро0 вой код Vijj-( , снимаемый с блока 8 згщержки другого квадратурного канала и умноженный во втором перемножителе 11 на хранящееся в третьем регистре 26 числа значение

5 81пц|. Третий сумматор 15 к величине Vjj., cosy прибавляет величину Vjjj sinif), получающуюсяв перемножителе 18 другого квадратурного канала. Во втором квадратурном канале первый сумматор 10 осуществляет сложение; а третий 15 - вычитание В результате выполнения операций в перемножителях 9, 11, 18 и 19 и сумматорах 10 и 15 происходит дву мерный поворот квадратурны с состав ляющих ., ., и v;- , ,V4JM соответственно на углы +у и В третьем и шестом перемножителях 17 и 20 выходные величины перв го и третьего сумматоров 10 и 15 у ножаются на хранящуюся в первом регистре 24 числа величину коэффиц та обратной связи fi , На выходах вторых и четвертых суммё торов 14 и 16 первого и второ квадратурных каналов образуются величины: ii iP «i- ° - 4iM3 4V, vjj -: и.и )- ;j-U,,,p(-v;j.,sinvrVj.,cos4). .Цифровые коды на выходах cyr«iaторов 14 и 16 в каждом периоде представляют собой результат сум- .мирования поступающих с аналого-цифровых преобразователей цифровых кодов квадратурных состав ляюцих текущего и предыдущих периодов, причем каждой операции суммирования предиествуют операции поворота фазы, полученной в предыдущем периоде сумгв на угол ((/ и ум ножения ее на коэффициент р . Комплексные величины, отображаеьме ква ратурными составляющими на выходах сумматоров 14 и 16, будут равны соответственно ,,. vi . .. Обработка производится раздельно для каждого элемента разрешения по дальности, что обеспечивает высокую разрешающую способность цифрового частотного дискриминатора, В блоках 12 и 21 усреднения . (фиг.2) производится накопление да ных с N смежнцх элементов разрешения по дальности г что позволяет сгладить флюктуации поотупающик ои налое и ецизить елияние 1нутрениих шумов приемника. Накопление проияводится путем задержки кодов в бло ках 29 задержки и суммирования их сумматорах 28. В блоке 30 нормиров ки производится деление выходной величины поцледиего сумматора на хранящееся в блоке 31 памяти число N. В блокг1Х 22 обработки сигналов, содержащих квадраторы, сумматоры и функциональные преобразователи, реализующие операцию вычисления квадратного корня, осуществляется вычисление величин . V «iLli М N Блок 27 вычитания вычисляет разность Д) v-vj . При частоте i принимаемого сигнала, равной „ , величины V HV оказываются и Aj 0. При f 1 величина А получается отличной от нуля и значение ее зависит от величины расстройки частоты &{ f-Ig. Работа цифровых блоков синхронизируется синхронизирующим импульсом, вырабатываемым генератором 3 синхронизирующих импульсов. Длительность синхронизирующих импульсов соответствует длительности кодового слова, период следования - длительности элемента разрешения по дал ности. Синхронизирующие импульсы поступают в аналого-цифровые преобразователи 7, в блоки 8 и 13 задержки, в блоки 12 и 21 усреднения. Во время действия синхронизирующих импульсов происходит сдвиг информации в элементах памяти блоков 8 и 13 эадержки и блоков 12 и 21 усреднения, приводящий к считыванию и записи цифровых кодов. Рассмотрим эффективность предлагаемого цифрового частотного дискриминатора. Выражение для дискриминационной характеристики имеет вид Nt {b-7(ico9(.4f (Ьсов(лт. На фиг.З приведены характеристики предлагаемого цифрового частотного дискриминатЪра, вычисленные при

« 0,75. Пунктирная прямая соответствует прототипу. По сравнению с прототипом крутизна характеристики йредлагаемсго цифрового частотного if€Fe/rfffmff6/v

-гЧ«1

Ф1П.2

дискриминатора в пределах линейного участка в 4-5 раз выше, что эквивалентно соответствующему повышению чувствительности. ffvcffpt/ffwfer/rfia fl

Фт 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| JbixapeB В.А.Цифровые мето- да н устройства в радиолокации | |||

| М., | |||

| Сов | |||

| радио, 1973, с.276, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , 2. | |||

| Цифровой частотный дискриминатор | 1978 |

|

SU780153A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| (прототип). | |||

Авторы

Даты

1983-12-07—Публикация

1981-11-18—Подача