(54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ОСТАТКА ПО ПЕРЕМЕННОМУ МОДУЛЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1989 |

|

SU1698991A1 |

| Устройство для контроля адресных шин интерфейса | 1984 |

|

SU1242963A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ (СОК) | 2009 |

|

RU2413279C1 |

| Преобразователь двоичного кода в код по модулю | 1980 |

|

SU902013A1 |

| Устройство для выделения остатка по переменному модулю | 1984 |

|

SU1270774A2 |

| Устройство для контроля информации в системе остаточных классов | 1984 |

|

SU1166117A1 |

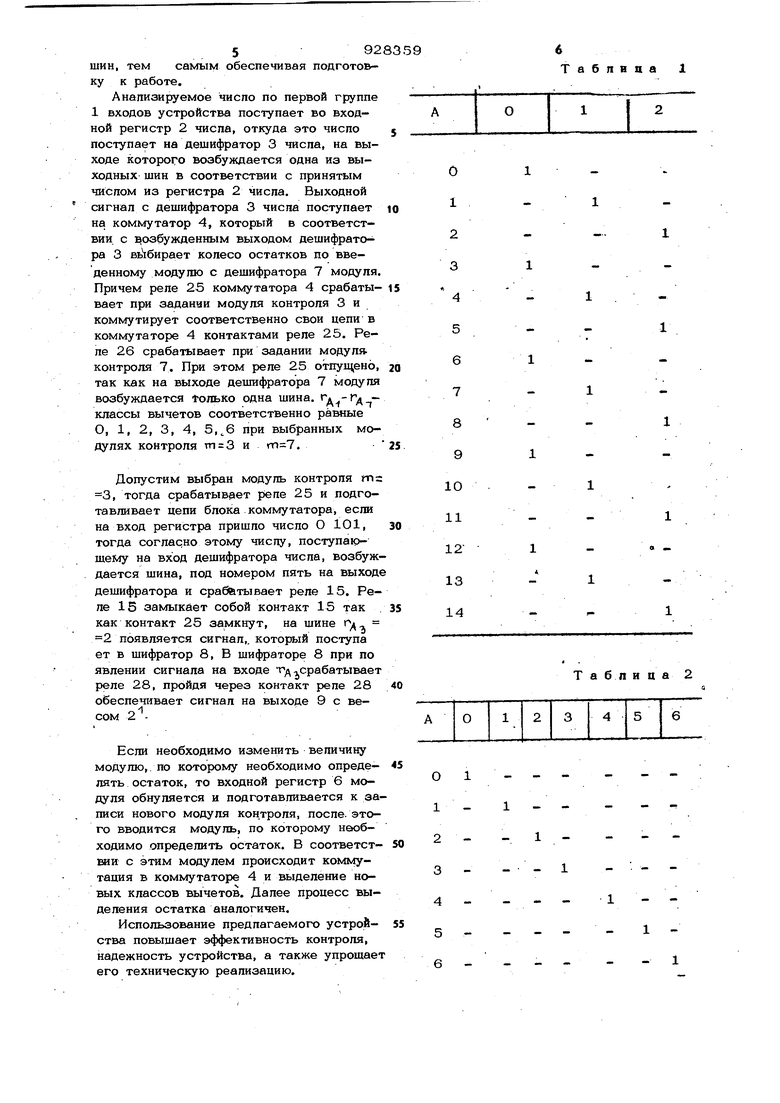

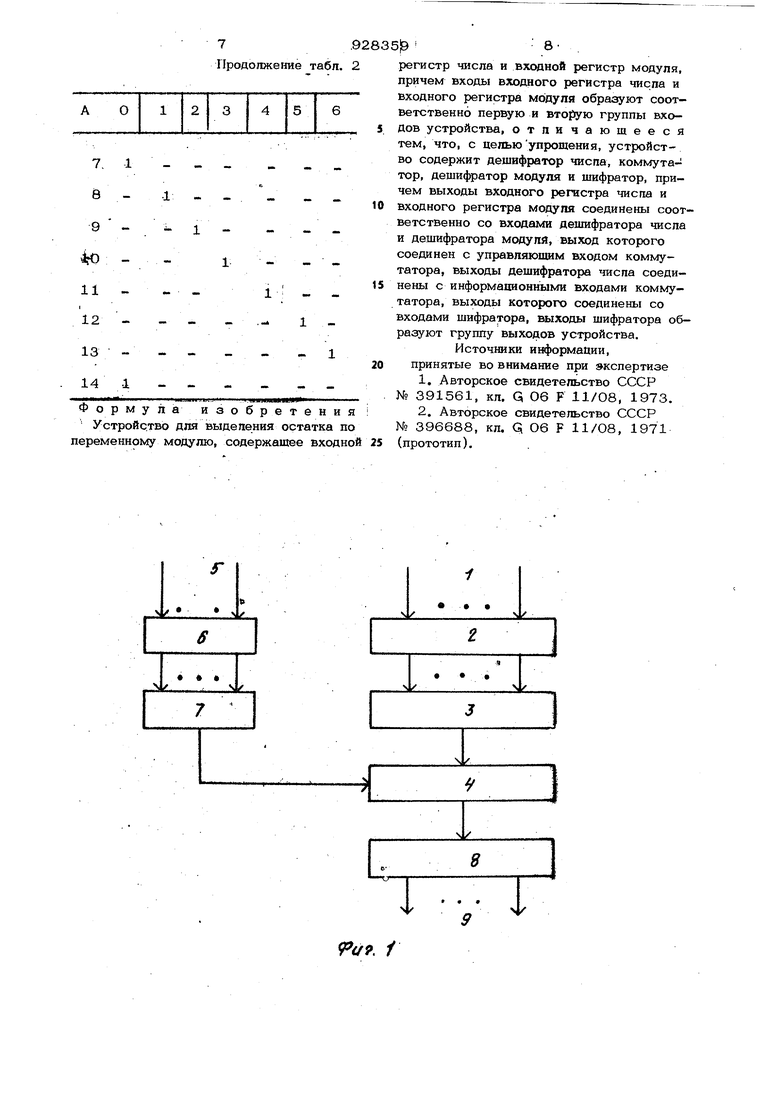

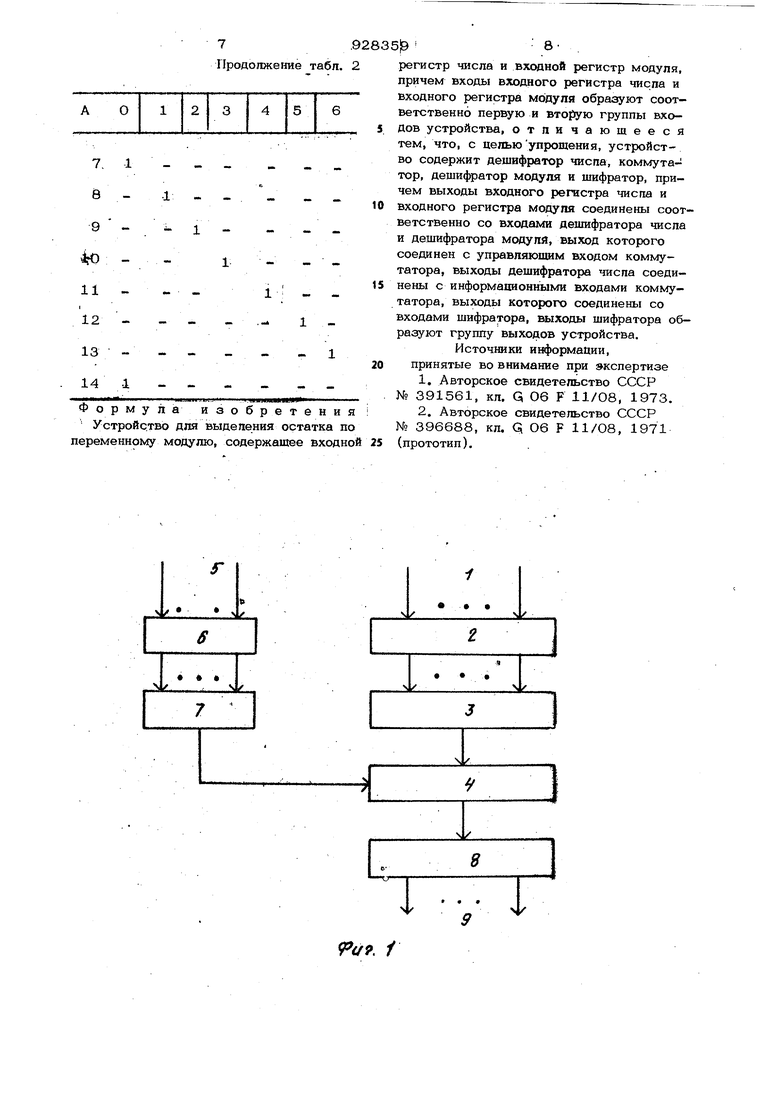

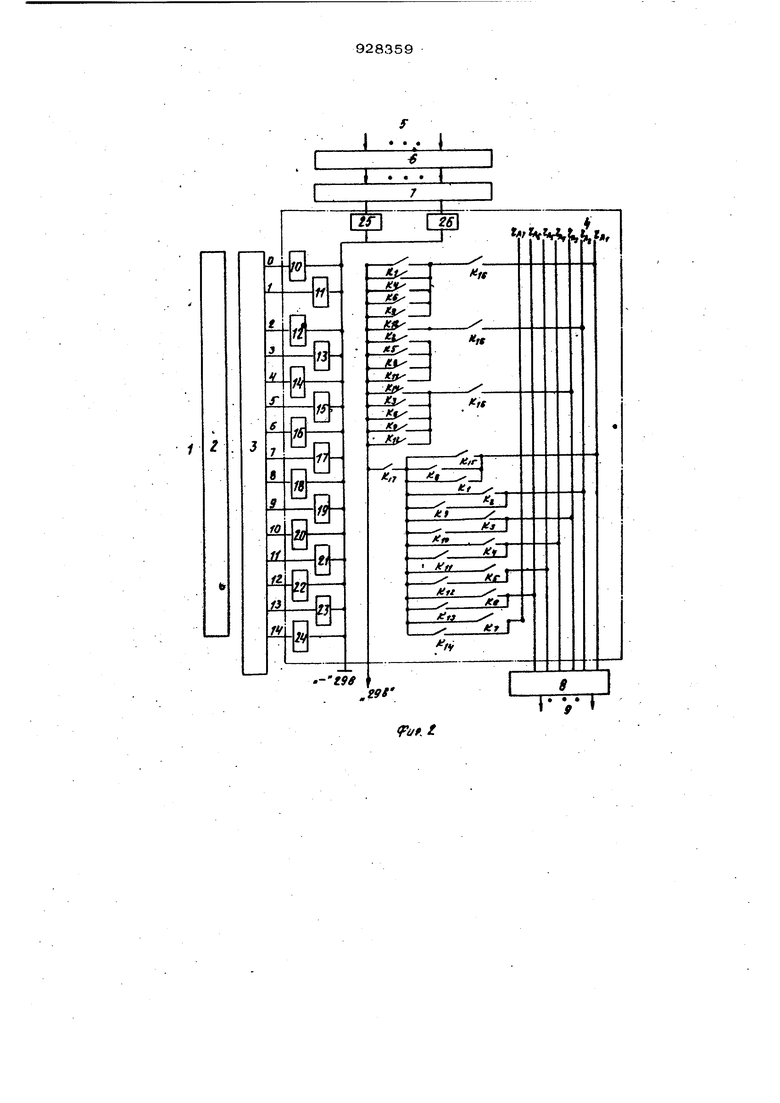

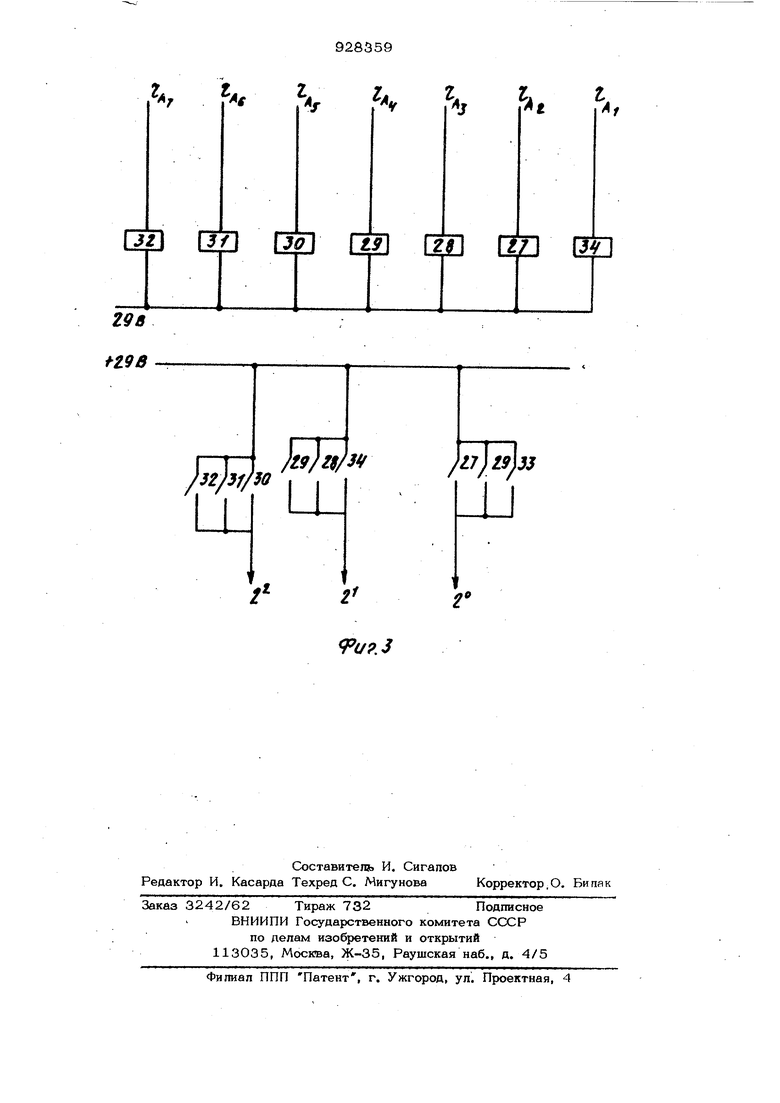

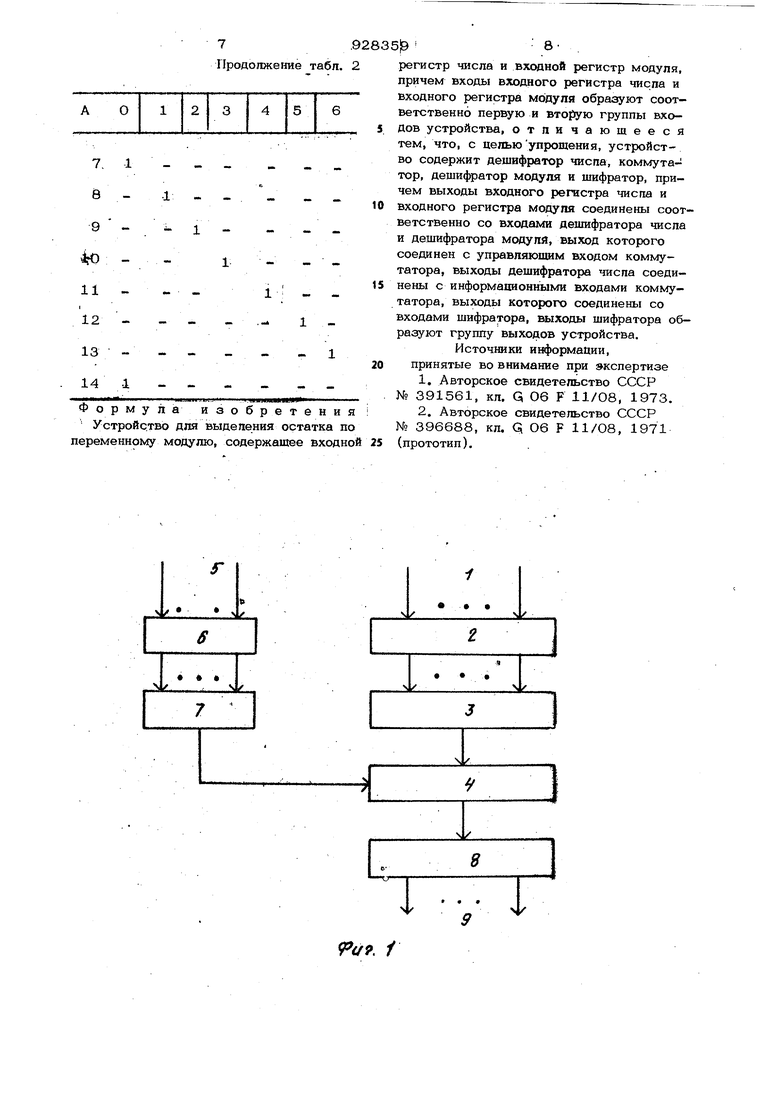

Изобретение относится к вычиспитель ной технике и может быть использовано для перевода двоично кодированных чисел из системы в систему остаточных классов и для свертки чисел в устройствах контроля по модулю. Известно устройство для выделения остатка по заданному модулю, содержащее регистр исходного числа, блоквычис ления частичных вычетов, выходы которо го соединены с входами сумматора. При этом блок исключения дополнительных (пар своими входами соединен с выхода- /ми регистра исходного числа, а выходы его соединены с входами блока частич- ного вычета 11. Недостатками данного устройства яв ляются его сложность и невозможность изменять величину модуля в процессе контроля. Наиболее близким к предлагаемому является устройство для определения вы четов числа по двум модулям, содержащее цепи приема числа, двоичный регист групповые схемы суммирования по модулю, групповые схемы коррекции, общую схему суммирования, .общую схему коррекции, сумматор, цепи выхода сумматора, Регистр соединен через групповые схе- мы суммирования по модулю с обшей схемой суммирования по модулю, выходы регистра соединены с входами групповых схем коррекции, выходы которых соединены с первыми входами обшей схемы коррекции, другие входы которой соединены с вторыми выходами групповых схем суммирования по модулю и вторыми выходами общей схемы суммирования по модулю и выходы общей схемы коррекции соединены с входами сумматора Г2. Недостатками указанного устройства являются больщая сложность его конструкции, а в связи с этим и низкая надежность. Цель изобретения - упрощение устройства, и повыщение надежности. Поставленная цепь достигается тем, что в устройство для выделения остатка по переменному модугао, содержащее вход ной регистр числа и входной регистр модуля, причем входы входного регистра числа и входного регистра модуля образуют соответственно первую и вторую группы входов устройства, введены дешифратор чиспа, коммутатор, дешифратор модуля и шифратор, причем выходы входного регистра чиспа и входного регистра модуля соединены соответственно со. входами дешифратора числа и дешифратора модуля, выход которого ; соединен с уп равляюшим входом коммутатора, выходы Дешифратора числа соединень)г с информационными входами ком мутатора, выходы которого соединены со входами шифратора, выходы шифратора образуют группу выходов устройства. .На фип 1 представлена структурная схема устройства для выделения остатка по переменному модулю; на фиг. 2 один из вариантов коммутатора; на фиг.З один из вариантов шифратора. Устройство содержит первую группу 1 входов устройства, входной регистр 2 .числа, дешифратор 3 числа, коммутатор 4, вторую группу 5 входов устройства, входной регистр 6 модуля, дешифратор 7 модуля, шифратор 8, группу 9 выходов устройства. Коммутатор 4 состоит из репе 10-26, а шифратор - из релле 27-34. Входной регистр 2 числа с воими входами соединен с группой входов 1 числа, остаток которого -подлежит выделению, а выходы подключены к дешифратору 3 чис ла, выход которого соединен с коммутатором 4. Вход коммутатора. 4 подключен к дешифратору ;7 модуля, а выход соединен с шифратором 8, который подключен к группе 9 выходов устройства. Входной регистр модуля своими входами соединен со входами 5 модуля по которому определяется остаток модуля, а выходом подключен к дешифратору 7 модуля. Первая группа 1 входов чиспа предназначена для введения во входной регистр 2 числа исходного числа. Регистр 2 числа предна значен для его хранения и выдачи на дешифратйр 3 числа. Разрядность регистра определяется максимальным числом, запи сываемым во входной регистр 2. Дешифратор 3 числа предназначен дл возбуждения одной из выходных шин в со ответствии с поступившим на вход кодом из входного регистра 2. Дешифратор 3 числа может быть выполнен как одноступенчатый, так и многоступенчатый. Коммутатор 4 осуществляет коммутацию с целью выделения остатка по выбранному модулю контроля. Все целые числа распределяются относительно данного модуля m на m классов, так что все числа одного и того же класса сравнимы друг с другом по модулю тп тогда как числа разных классов не сравнимы друг с другом по модулю т.. Если из каждого из Ifn классов, на которые распадаются все целые числа по мо дулю m взять по одному числу, то эти m чисел составляют полную систему вычетов по модулю т. Так как предел изменения величины числа, от которого ЕЫделяется остаток, определяется разрядностью регистра 2, то этот предел заранее известен. Поэтому известны в этом диапазоне чисел и остатки по выбранным модуля, которые определяются по классам. Та, например . для ичисла А, изменяющего от О до 14, остатки по модулю 3 разбиваются на три класса, а по модулю 7 - на 7 классов. Распределение остатков по данным моду- . ля представлены в табл. 1 и 2. Единица на пересечении -i строки с j столбцом говорит о том, что данное i число входит в j класс с остатком г д. Количество элементов блока 4 коммутации определяется максимальной разрядностью числа, от которого определяется остаток , и количеством модулей, от котоых определяется остаток группы. Группа 5 входов модуля предназначена для введения модуля контроля в регистр 6, Регистр 6. модуля предназначен для его хранения и выдачи его на дешифратор 7 модуля. Разрядность регистра 6 определяется максимальной длиной используемого модуля контроля. Дешифратор 7 предназначен для возбуждения одной из выходных шин . в соответствии с кодом, поступающим с регистра 6 модуля. Шифратор 8 предназначен для выделения.остатка в двоичном коде в соответствии с определенным классом 4 ь коммутаторе 4, в соответствии с выбранным модулем контроля. Группа 9 выходов устройства предназначена для выдачи остатка на другие узлы контролируемой аппаратуры, Устройство работает следующим образом. Во входной регистр 6 модуля предварительно записывается модуль, по которому необходимо выделить остаток VAjИнформация о модуле контроля с р гистра поступает на дешифратор 7 модуля, который возбуждает одну из выходных

592

шин, тем самым обеспечивая подготовку к работе.

Анализируемое число по первой группе 1 входов устройства поступает во входной регистр 2 числа, откуда это число поступает на дешифратор 3 числа, на выходе которого возбуждается одна из выходных шин в соответствии с принятым числом из регистра 2 числа. Выходной сигнал с дешифратора 3 числа поступает на коммутатор 4, который в соответствии с возбужденным выходом дешифратора 3 вь бирает колесо остатков по введенному модулю с дешифратора 7 модуля. Причем реле 25 коммутатора 4 срабаты- вает при задании модуля контроля 3 и коммутирует соответственно свои цепи в коммутаторе 4 контактами реле 25. Реле 26 срабатывает при задании модуля, контроля 7. При этом реле 25 отпущено, так как на выходе дешифратора 7 модуля возбуждается только одна шина. - классы вычетов соответственно равные О, 1, 2, 3, 4, 5,6 при выбранных модулях контроля т 3 и .

Допустим выбран модуль контроля тг 3, тогда срабатывает реле 25 и подготавливает цепи блока коммутатора, если на вход регистра пришло число О 101, тогда согласно этому числу, поступаюшему на вх:од дешифратора числа, возбуждается шина, под номером пять на выходе дешифратора и срабатывает реле 15. Реле 15 замыкает собой контакт 15 так как контакт 25 замкнут, на шине - появляется сигнал,, который поступа ет в шифратор 8, В шифраторе 8 при по явлении сигнала на входе тд срабатывает реле 28, пройдя через контакт реле 28 обеспечивает сигнал на выходе 9 с весом 2.

Если необходимо изменить величину модулю,, по которому необходимо опреде- лять остаток, то входной регистр 6 модуля обнуляется и подготавливается к записи нового модуля коцтроля, после, этого вводится модуль, по которому необходимо определить остаток. В соответстИ1И с этим модулем происходит коммутация в коммутаторе 4 и выделение новых классов вычетов. Далее процесс выделения остатка аналогичен.

Использование предлагаемого устройства повышает эффективность контроля, надежность устройства, а также упрощает его техническую реализацию.

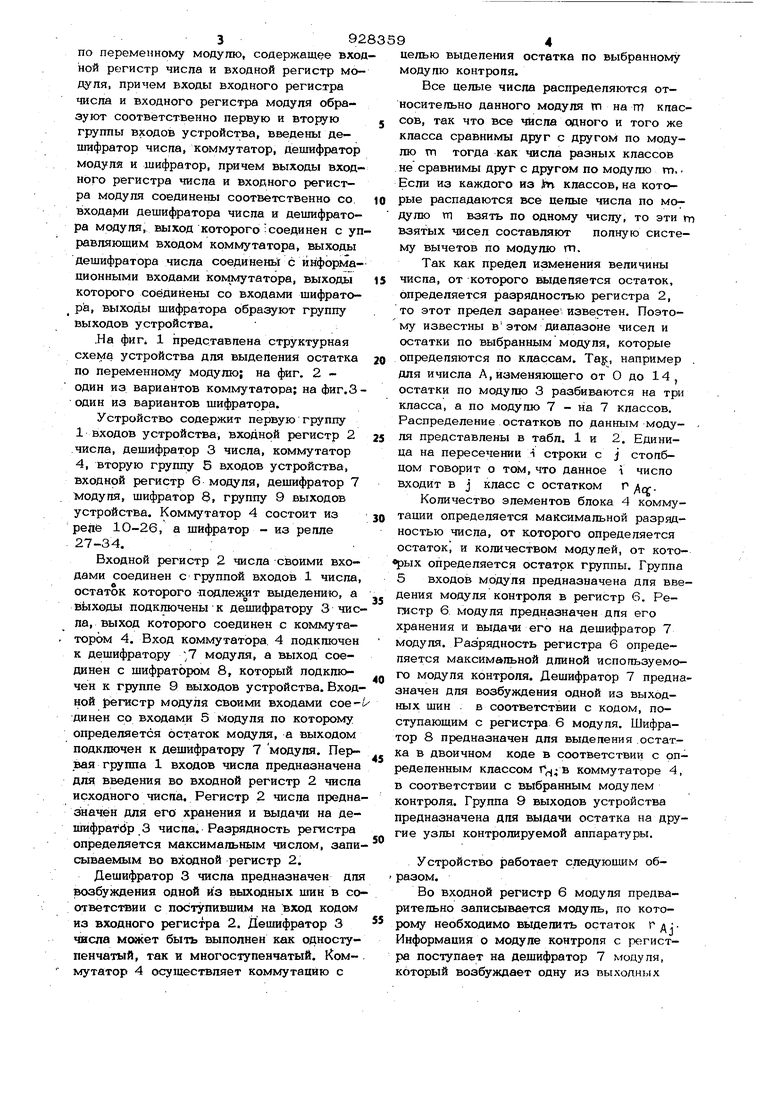

Таблица 1

О 1 2 3

4 5 6 7 8 9

10 11 1213 14

Таблица 2

1

1 - 1 - - 1

1 - 1

11 12 13 14 1 Фор - Устро переменн

J/ . ч1/

|/Ч

J

8

Г-v i

. i регистр числа и входной регистр модуля, причем входы входного регистра числа и входного регистра модуля образуют соответственно первую и вторую группы входов устройства, отличающееся тем, что, с целью упрощения, устройство содержит дешифратор числа, коммутатор, деши(}фатор модуля и щифратор, причем выходы входного регистра чиспа и входного регистра модуля соединены соответственно со входами дешифратора числа и дешифратора модуля, выход которого соединен с управляющим входом коммутатора, выходы дешифратора чиспа соединены с информационными входами коммутатора, выходы которого соединены со входами шифратора, выходы шифратора образуют группу выходов устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 391561, кл. G 06 F 11/О8, 1973. 2.Авторское свидетельство СССР № 396688, кп. Q Об F 11/О8, 1971 (прототип).

П9В

J

19/3

)sz)

Pu,3

/

JJ

Авторы

Даты

1982-05-15—Публикация

1980-07-16—Подача