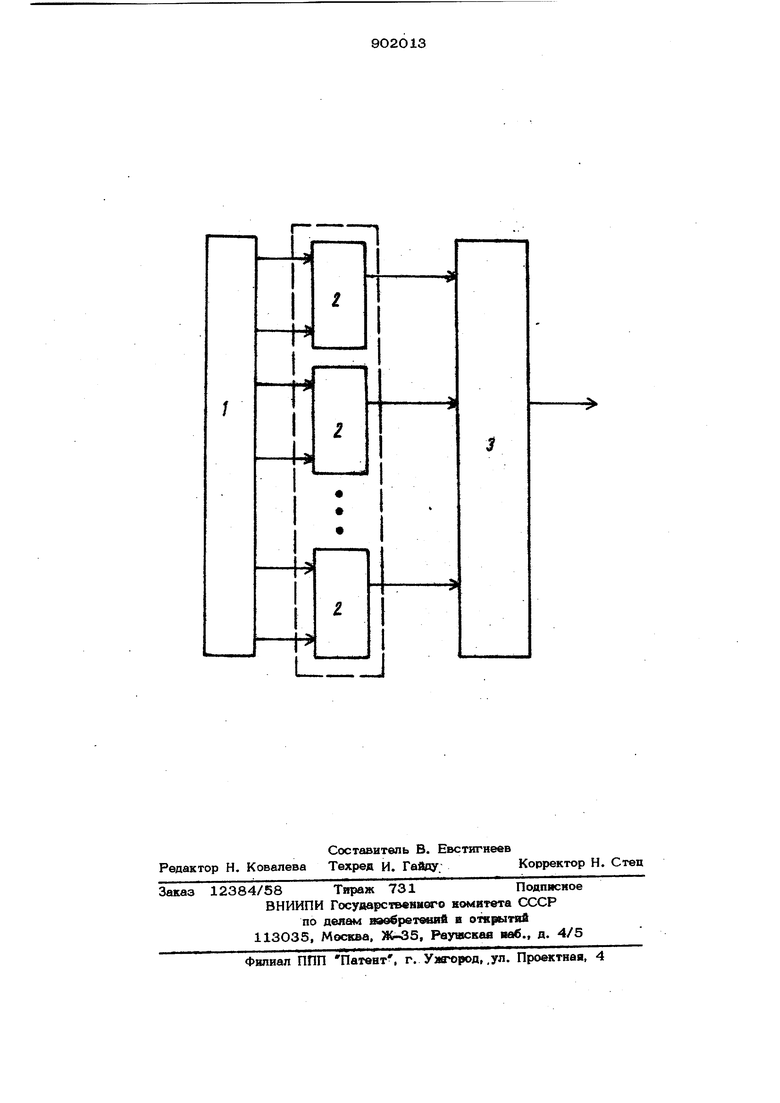

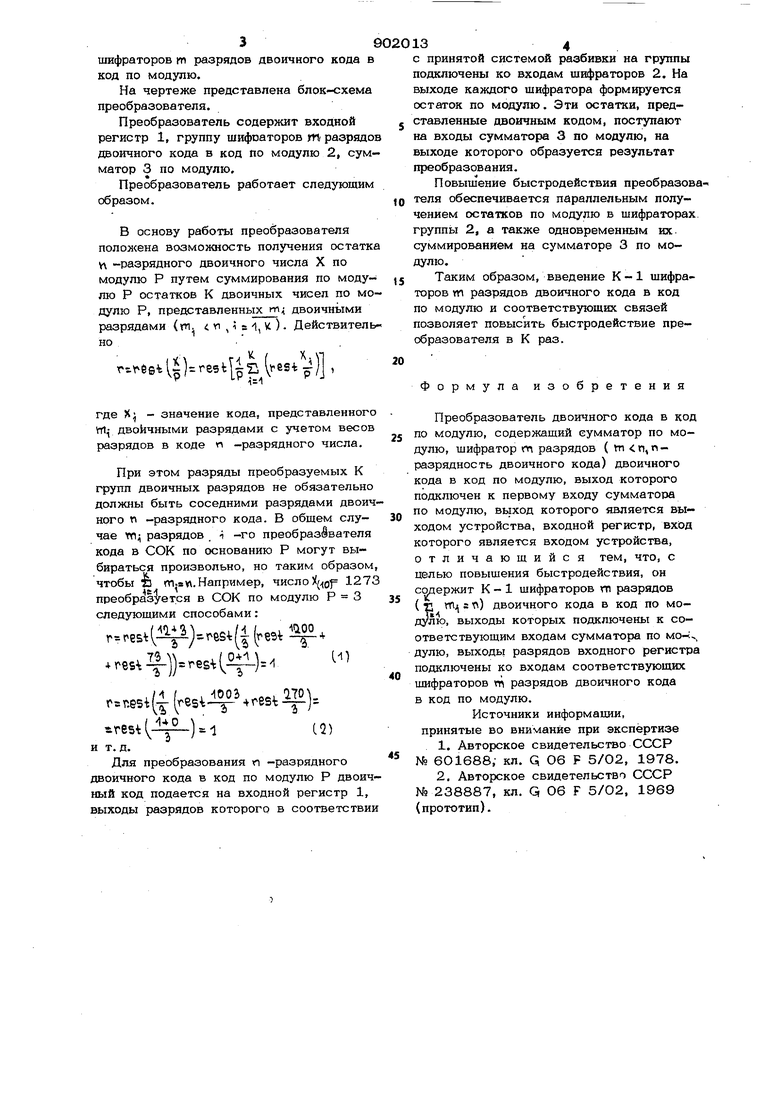

Изобретение относится к вычислительной технике. Известен преобразователь позиционных кодов в код системы остаточных классов содержащий группу накаппиваюших сум-« маторов, блок вычитания кодов, группу элементов И с соответствующими связями 1 . Наиболее близким к предлагаемому является устройство для преобразования чисел из позиционной системы счисления в систему счисления остаточных классов, содержащее блок суммирования, регкст ры, блок двоичного кодирования и дешифраторы, причем регистр исходной информации со сдригом на четыре разряда впра во соединен через дешифратор двоичных тетрад со вторым дешифратором, ко входам которого подключены шины сигналов, соответствующих весам разрядов преобразуемого числа, выходы второго дешифратора подключен, к блоку двоичного кодирования разрядов числа в системе счисления остаточн),тх классов, выходы которого связаны с приемными регистоами блока суммирования, состоящего из независимых устройств суммирования, соответствующих основаниям систем счисления остаточных классов 121 . Недостатком известных устройств является низкое быстродействие. Цель изобретения - повьпиение быст родействия. Поставленная цель достигается тем, что устройство, содержащее сумматор по модулю, шифратор m разрядов ( m п, п - разрядность двоичнго кода) двоичного кода в код по модулю, выход которого подключен к первому входу сумматора по модулю, выход которого является выходом устройства, входной регистр, вход которого является входом устройства, содержит К - 1 шифраторов m раар5щов (т, W, S v) двоичного кьда в код по модулю, выходы которых подключены к соответствующим входам сумматора по модулю, выходы разрядов входного регистра подключены ко входам соответствующих . игафраторов m разрядов двоичного кода в код по модулю. На чертеже представлена блок-схема преобразователя. Преобразователь содержит входной регистр 1, группу шифраторов m разрядо двоичного кода в код по модулю 2, сумматор 3 по модулю. Преобразователь работает следующим образом. В основу работы преобразователя положена возможность получения остатка V -разрядного двоичного числа X по модулю Р путем суммирования по модулю Р остатков К двоичных чисел по мо дулю Р, представленных пл двоичными разрядами (т. п , i s 1, к ). Действитель )S5t i2 iesi) где Х - значение кода, представленного W двоичными разрядами с учетом весов разрядов в коде г -разрядного числа. При этом разряды преобразуемых К групп двоичных разрядов не обязательно должны быть соседними разрядами двоич ного Г1 -разрядного кода. В общем случае «1;; разрядов . i -го преобраз1§вателя кода в СОК по основанию Р могут выбираться произвольно, но таким образом, чтобы Z1 m.sv.Например, число 1273 преобразуется в СОК по модулю Р 3 следующими способами: r-res j-esHih T r«t2|- res4Sf)И) (i(.esi ..estM „,ы(-)1(5) Для преобразования п -разрядного двоичного кода в код по модулю Р двоичный код подается на входной регистр 1, выходы разрядов которого в соответствии с принятой системой разбивки на группы подключены ко входам шифраторов 2, На выходе каждого шифратора формируется остаток по модулю. Эти остатка, представленные двоичным кодом, поступают на входы сумматора 3 по модулю, на выходе которого образуется результат преобразования. Повышение быстродействия преобразователя обеспечивается параллельным получением остатков по модулю в шифраторах, группы 2, а также одновременным их. суммированием на сумматоре 3 по модулю. Таким образом, введение К -1 шифраторов w разрядов двоичного кода в код по модулю и соответствующих связей позволяет повысить быстродействие преобразователя в К раз. Формула изобретения Преобразователь двоичного кода в код по модулю, содержащий сумматор по модулю, шифратор m разрядов ( m п, празрядность двоичного кода) двоичного кода в код по модулю, выход которого подключен к первому входу сумматора по модулю, выход которого является выходом устройства, входной регистр, вход которого является входом устройства, отличающийся тем, что, с целью повышения быстродействия, он содержит К - 1 шифраторов m разрядов гч S т) двоичного кода в код по мо- упю, ВЫХОДЫ которых подключены к соответствующим входам сумматора по мо-i дулю, выходы разрядов входного регистра подключены ко входам соответствующих шифраторов тп разрядов двоичного кода в код по модулю. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 601688.- кл. Q 06 F 5/02, 1978. 2.Авторское свидетельство СССР № 238887, кл. Q 06 F 5/О2, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Устройство для определения позиционных признаков непозиционного кода | 1983 |

|

SU1142827A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1982 |

|

SU1151948A1 |

| Преобразователь кодов из системыОСТАТОчНыХ КлАССОВ B дВОичНыйпОзициОННый КОд | 1979 |

|

SU813408A1 |

| Преобразователь полиадического кодаВ КОд СиСТЕМы ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU809154A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ (СОК) | 2009 |

|

RU2413279C1 |

| Преобразователь числа из двоичной системы счисления в систему остаточных классов | 1983 |

|

SU1125621A1 |

| Устройство для выделения остатка по переменному модулю | 1980 |

|

SU928359A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

Авторы

Даты

1982-01-30—Публикация

1980-06-30—Подача