() УСТРОЙСТВО для ВРЕМЕННОГО КОМПАНДИРОВАНИЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для временного компандирования | 1981 |

|

SU1072279A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Устройство приема пакетной информации системы спутниковой связи | 1986 |

|

SU1506561A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029370C1 |

| Система передачи данных с множественным доступом | 1985 |

|

SU1309323A1 |

| Устройство ввода асинхронного цифрового потока | 1987 |

|

SU1474658A1 |

| Устройство для восстановления скорости цифрового потока | 1988 |

|

SU1601764A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

I

Изобретение относится к радиотехнике и может использоваться в спутниковых системах связи с многостанционным доступом и временным уплотнением (МДВУ) сигналов земных станций.(ЗС) в стволе ретранслятора.

Известно устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты, блок перебора адресов записи, первый элемент И, -элемент ИЛИ, блок памяти и первый регистр, управляющий вход которого объединен с управляющим входом второго регистра, ин(|юрмационные входы которого соединены с соответствующими выходами блока памяти, информационные входы которого соединены с соответствующими выходами третьего регистра, последовательно соединенные второй делитель частоты, блок перебора адресов считывания и второй элемент И, выход которого

соединен с вторым входом элемента ИЛИ, и третий и четвертый элементы И, первые входы которых являются входами сигнала огибающей ГП.

Однако известное устройство имеет длительное время компандирования и сложно.

Цель изобретения - сокращение времени компандирования и упрощение устройства за счет уменьшения общего числа элементов.

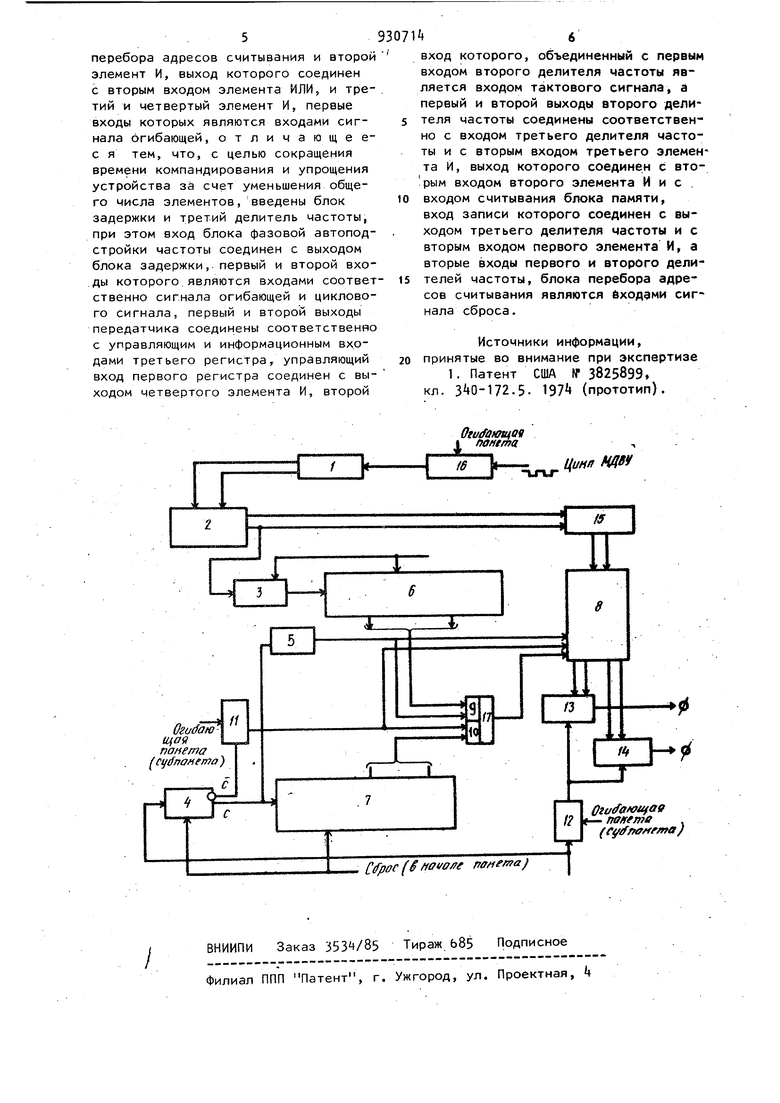

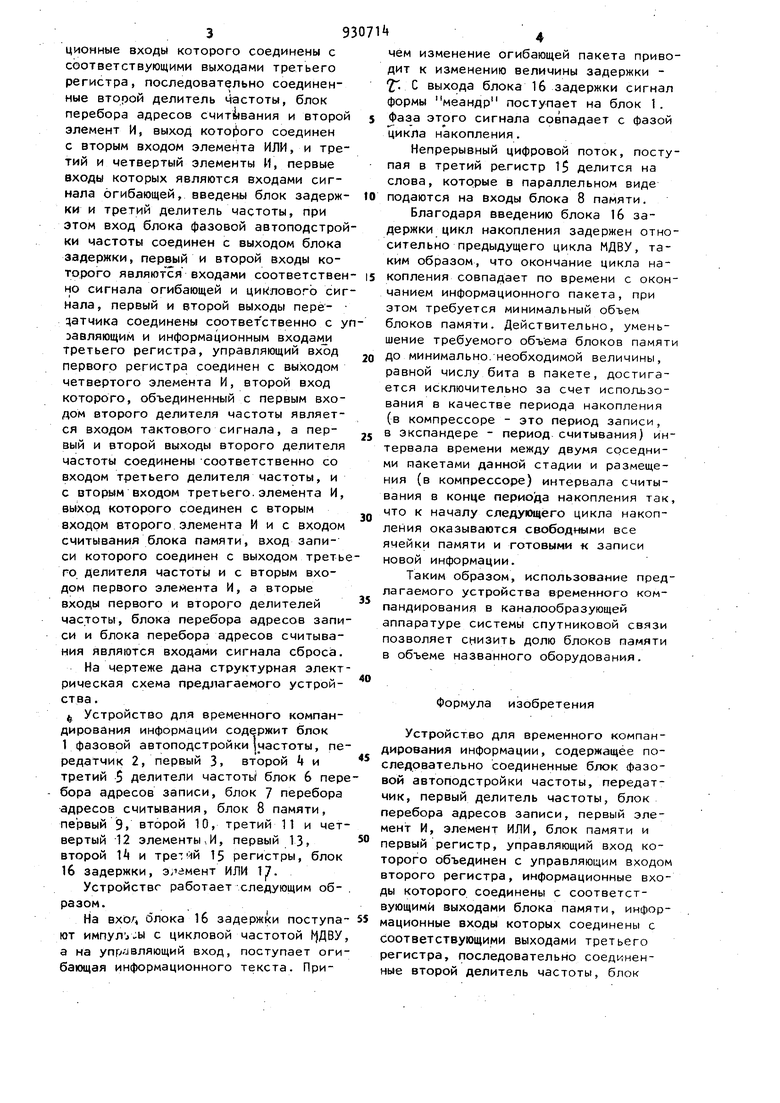

Поставленная цель достигается тем, что в устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты,блок перебора адресов записи, первый элемент И, элемент ИЛИ, блок памяти и первый регистр, управляющий вход которого объединен с управляющим входом второго регистра, информационные входы которого соединены с соответствующими выходами блока памяти, информациоииые входы которого соединены с соответствующими выходами третьего регистра, последовательно соединенные второй делитель частоты, блок перебора адресов счит4|вания и второй элемент И, выход которого соединен с вторым входом элемента ИЛИ, и третий и четвертый элементы И, первые входы которых являются входами сигнала огибающей, введены блок задержки и третий делитель частоты, при этом вход блока фазовой автоподстрой ки частоты соединен с выходом блока задержки, первый и второй входы которого являются входами соответствен но сигнала огибающей и циклового сиг нала, первый и второй выходы пере- цатчика соединены соответственно с у эавляющим и информационным входами третьего регистра, управляющий вход первого регистра соединен с выходом четвертого элемента И, второй вход которого, объединенный с первым входом второго делителя частоты является входом тактов.ого сигнала, а первый и второй выходы второго делителя частоты соединены -соответственно со входом третьего делителя частоты, и с вторым входом третьего.элемента И, выход которого соединен с вторым входом второго элемента И и с входом считывания блока памяти, вход записи которого соединен с выходом треть го делителя частоты и с вторым входом первого элемента И, а вторые входы первого и второго делителей частоты, блока перебора адресов запи си и блока перебора адресов считывания являются входами сигнала сброса. На чертеже дана структурная элект рическая схема предлагаемого устройства , Устройство для временного компандирования информации содержит блок 1 фазовой автоподстройки (частоты, пе редатчик 2, первый 3, второй k и третий 5 делители частоть блок 6 пер бора адресов записи, блок 7 перебора адресов считывания, блок 8 памяти, первый 9, второй 10, третий 11 и чет вертый 12 элементы,И, первый 13, второй и тре-;йй 15 регистры, блок 16 задержки, элемент ИЛИ 1J7. Устройстве работает следующим образомНа блока 16 задержки поступа ют импулл-Ы с цикловой частотой )ДВУ а на yпr Jвляющий вход, поступает оги бающая информационного текста. Причем изменение огибающей пакета приводит к изменению величины задержки 1. С выхс)да блока 16 задержки сигнал формы меандр поступает на блок 1. Фаза этого сигнала совпадает с фазой цикла накопления. Непрерывный цифровой поток, поступая в третий регистр 15 делится на слова, которые в параллельном виде подаются на входы блока 8 памяти. Благодаря введению блока 16 задержки цикл накопления задержем относительно предыдущего цикла МДВУ, таким образом, что окончание цикла накопления совпадает по времени с окончанием информационного пакета, при этом требуется минимальный объем блоков памяти. Действительно, уменьшение требуемого объема блоков памяти до минимально, необходимой величины, равной числу бита в пакете, достигается исключительно за счет использования в качестве периода накопления (в компрессоре - это период записи, в экспандере - период.считывания) интервала времени между двумя соседними пакетами данной стадии и размещения (в компрессоре) интервала считывания в конце периода накопления так, что к началу следукмдего цикла накопления оказываются свободными асе ячейки памяти и готовыми « записи новой информации. Таким образом, использование предлагаемого устройства временного компандирования в каналообразующей аппаратуре системы спутниковой связи позволяет снизить долю блоков памяти в объеме названного оборудования. Формула изобретения Устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты, блок перебора адресов записи, первый элемент И, элемент ИЛИ, блок памяти и первый регистр, управляющий вход которого объединен с управляющим входом второго регистра, информационные входы которого соединены с соответствующими выходами блока памяти, информационные входы которых соединены с соответствующими выходами третьего регистра, последовательно соединенные второй делитель частоты, блок перебора адресов считывания и второй элемент И, выход которого соединен с вторым входом элемента ИЛИ, и третий и четвертый элемент И, первые входы которых являются входами СИ1- нала огибающей, отличающеес я тем, что, с целью сокращения времени компандирования и упрощения устройства за счет уменьшения общего числа элементов, введены блок задержки и третий делитель частоты, при этом вход блока фазовой автоподстройки частоты соединен с выходом блока задержки, первый и второй входы которого.являются входами соответ ственно сигнала огибающей и циклового сигнала, первый и второй выходы передатчика соединены соответственно с управляющим и информационным входами третьего регистра, управляющий вход первого регистра соединен с выходом четвертого элемента И, второй

dJ-

Oгufвющa9 nofftma

Цинп

f6

vrw

tZJ 6 вход которого, объединенный с первым входом второго делителя частоты является входом тактового сигнала, а первый и второй выходы второго делителя частоты соединены соответственно с входом третьего делителя частоты и с вторым входом третьего элемента И, выход которого соединен с входом второго элемента И и с . входом считывания блока памяти, вход записи которого соединен с выходом третьего делителя частоты и с вторым входом первого элемента И, а вторые входы первого и второго делителей частоты, блока перебора адресов считывания являются входами сигнала сброса. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3825899, кл. BtO-iya.S. 197 (прототип).

Авторы

Даты

1982-05-23—Публикация

1980-07-23—Подача