(Л

3150656

1ой аппаратуры, введены два блока 7, 8 памяти, два блока 9, 10 адресов записи, два элемента задержки 11, 12, инвертор 13, элемент ИЛИ 14, блок 15 5 адресов считывания, два ключа 16, 17, два перемножителя 18, 19, два интегратора 20, 21 и блок 22 сравнения. Считывание информации из блоков 7 и 8 осуществляется с задержкой относи- 10 тельно начала на время, равное длине пакета Г . Задержка обеспечивается синхронизацией блока 15

задержанным элементом задержки 11 на in сигналом с выхода элемента ИЛИ 1А. По тактам блок 15 синхронизируется системными тактовыми сигналами, не имеющими неоднородностей тактовых фронтов. Так как управление записью осуществляется в один блок памяти тактовыми сигналами с прямой фазой, а в другой с инверсной, то в одном из вариантов запись будет произведена с лучшими, с точки зрения фазовых соотношений, условиями. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХПРОВОДНАЯ ДУПЛЕКСНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ | 1991 |

|

RU2037966C1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1992 |

|

RU2067316C1 |

| Устройство для временного компандирования | 1981 |

|

SU1072279A1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Автокоррелятор | 1990 |

|

SU1833894A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

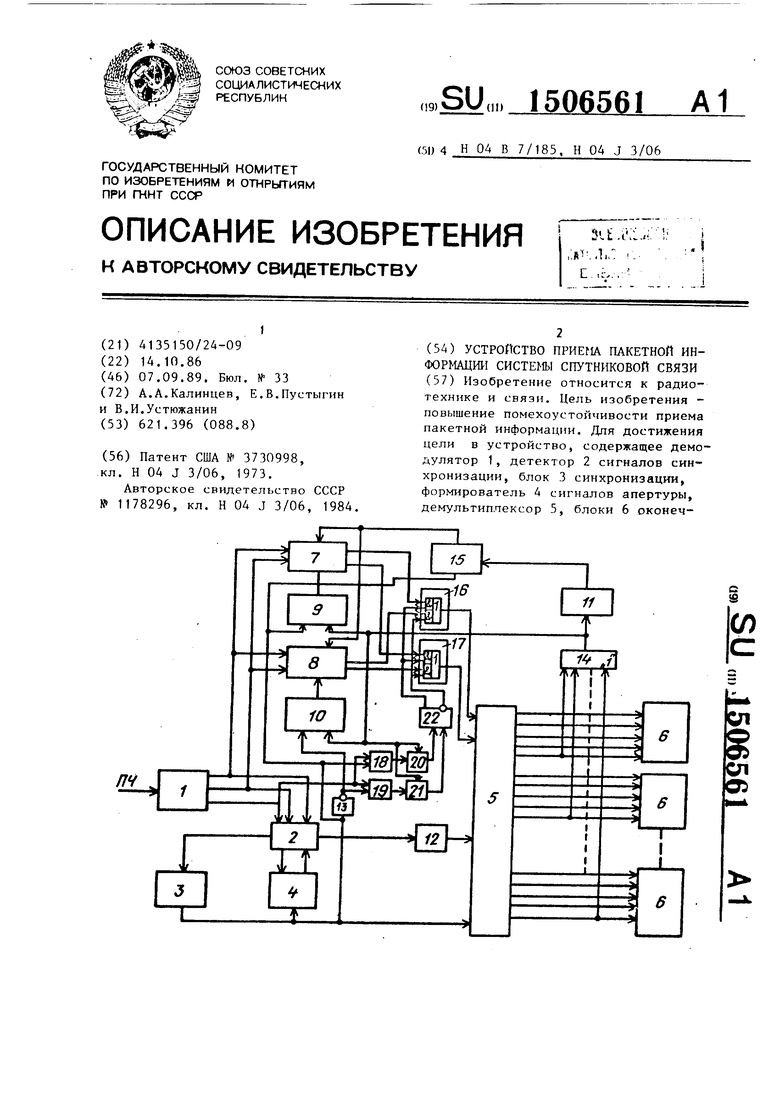

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение помехоустойчивости приема пакетной информации. Для достижения цели в устройство, содержащее демодулятор 1, детектор 2 сигналов синхронизации, блок 3 синхронизации, формирователь 4 сигналов апертуры, демультиплексор 5, блоки 6 оконечной аппаратуры, введены два блока 7, 8 памяти, два блока 9, 10 адресов записи, два элемента задержки 11, 12, инвертор 13, элемент ИЛИ 14, блок 15 адресов считывания, два ключа 16,17, два перемножителя 18, 19, два интегратора 20, 21 и блок 22 сравнения. Считывание информации из блоков 7 и 8 осуществляется с задержкой относительно начала записи на время, равное длине пакета τN. Задержка обеспечивается синхронизацией блока 15 задержанным элементом задержки 11 на τN сигналом с выхода элемента ИЛИ 14. По тактам блок 15 синхронизируется системными тактовыми сигналами, не имеющими неоднородностей тактовых фронтов. Так как управление записью осуществляется в один блок памяти тактовыми сигналами с прямой фазой, а в другой с инверсной, то в одном из вариантов записи будет произведена с лучшими, с точки зрения фазовых соотношений, условиями. 1 ил.

Изобретение относится к радиотехнике и связи и может быть использовано в системе радиосвязи с многостанционным доступом и временным уплотнением сигналов различных станций в стволе ретранслятора,в частности в системе спутниковой связи.

Цель изобретения - повьш1ение помехоустойчивости приема пакетной информации.

На чертеже приведено устройство приема пакетной информации системы спутниковой связи.

Устройство содержит демодулятор 1, детектор 2 сигналов синхрониза- , ции, блок 3 синхронизации, формиро- Iватель сигналов апертуры 4, демуль- типлексор 5, блоки 6 оконечной аппаратуры, первый и вторбй блоки 7 и 8 памяти, первый и второй блоки 9 и 10 гздресов записи, первый и второй элементы 11 и 12 задержки, инвертор 13, элемент ИЛИ 14, блок 15 адресов считывания, первый и второй ключи 16 и 17, первый и второй перемножители 18 и 19, первый и второй интеграторы 20 и 21, блок 22 сравнения.

Устройство приема пакетной информации системы спутниковой связи работает следующим образом.

Сигнал промежуточной частоты поступает на вход демодулятора 1, который осуществляет декодирование сигналов и формирует сопровождающую пакетную тактойую последовательность. При 4-фазной относительной фазовой манипуляции на выходе демодулятора 1 образуется два информационных канала Сигналы с выхода демодулятора 1 поступают на детектор 2 сигналов синхронизации, который осуществляет обработку с помощью сигнала апертуры синхропакетов ведущей и периферийно

0

0

земных станций. Детектированные сигналы синхронизации поступают в блок 3 и используются в качестве опорных для петли фазовой автоподстройки частоты, входящей в его состав. Сформированные блоком 3 непрерывные и системно-стабильные тактовые сигналы

5 подаются на демультиплексор 5 и формирователь 4 сигналов апертуры, который синхронизируется по циклам детектором 2 и вырабатывает стробирую- щие сигналы, используемые для временной селекции синхропакетов.

Тактовые сигналы с выхода демодулятора 1 поступают на первый и вто- рой перемножители 18 и 19, на вторые входы которых подаются непрерывные прямые и инверсные системные такто5 вые сигналы от блока 3 и инвертора 13 соответственно. Выходы первого и второго перемножителей 18 и 19 соединены соответственно с первым вторым интеграторами 20 и 21, которые осуществляют интегрирование результата перемножения на интервале времени, равном длине принимаемого пакета. Этот интервал определяется как сумма разнесенных по времени сигналов

5 апертуры, формируемых демультиплек- . сором 5, соединенных, элементом ИЛИ 14. При этом каждый сигнал апертуры соответствует временному положению информационных пакетов в цикле обра0 зующих один из передаваемых цифровых потоков и определяется расписанием связи, действующим в данное время. Сигналы апертуры вьфабатываются де- мультиплексором 5 с помощью сигналов

Сигналы с выходов первого и второго интеграторов 20 и 21 поступают на

0

5

блок 22 сравнения, который сравнива- ет два входных сигнала по уровням, если, например, сигнал с выхода пер- вого интегратора 20 больше сигнала с выхода второго интегратора 21, то на первом выходе блока 22 устанавливается логическая 1, а на втором - логический О, и наоборот.

В силу того,что информационный си нал от пакета к пакету флуктуирует по фазе в пределах защитного интервала между пакетами и мгновенное значение фазы сигналов задающих генераторов на передачу остальных земных станций отличаются друг от друга, демодулятор 1 формирует тактовые сигналы, фаза которых изменяется от пакета к пакету относительно тактовых сигналов, вырабатываемых блоком 3. Информационные сигналы с выхода демодулятора 1 поступают параллельно на входы первого и второго блоков 7 и 8, управляемых на запись первым и вторым блоками 9 и 10. Первый и вто- рой блоки 9 и 10 синхронизируются по циклу сигналом с выхода элемента ИЛИ 14, а по тактам - прямыми и инверсными тактовыми сигналами с выхода блока 3 и инвертора 13. Считывание информации из первого и второго блоков 7 и 8 осуществляется с задержкой относительно начала записи на время, равное длине пакета „ . Задержка обеспечивается синхронизацией блока 15 задержанным первым элементом задержки 11 на С сигналом с выхода элемента ИЛИ 14. По тактам блок 15 синхронизируется системными тактовыми сигналами, не имеющими неоднородное- .тей тактовых фронтов Считывание производится одновременно из первого и второго блоков 7 и В.

Состояние блока 22 определяет первый или второй блОк 7 или 8 памяти.

при записи в который фаза тактового

сигнала оказалась оптимальной по отношению к фазе принимаемого информационного сигнала. Так как управление записью осуществляется в один блок памяти тактовыми сигналами с прямой фазой, а в другой - с инверсной, то в одном из вариантов запись производится с лучшими, с точки зрения фазовых соотношений, условиями. Эти лучшие условия сложатся в том блоке памяти, у которого на выходе первого или второго перемножителей 18 и 19 окажется больший по уровню сигнал

0 5 0 5 о Q

..

5

5

0

5

616

Имтегриропамие сигналя перемножения первым и вторым интограт-орами 20 и

21исключает влияние фазовых ноодпп- родностей в тактовых сигргалах. Блок

22через первый и второй ключи 16 и 17 подключает выход первого или второго блоков 7 или 8 к информационным входам демультиплексора 5.

Сигнал цикла поступает с демультиплексора 5 на вход блоков 6 с задержкой на которую обеспечивает второй элемент 12 задержки. Демуль- типлексор 5 коммутирует временные информационные пакеты. Деьгультиплексор 5 вырабатывает также для каждого блока 6 временные окна, которые выделяют информационные пакеты, образующие одно направление связи. Формула изобретения

Устройство приема пакетной информации системы спутниковой связи, содержащее демодулятор, первый и второй информационные выходы и тактовый выход которого соединены соответственно с первым, вторым и третьим входами детектора сигналов синхронизации, первый выход которого соединен с блоком синхронизации, выход которого соединен с первым входом формирователя сигналов апертуры и тактовым входом демультиплексора, причем каждая группа выходов демультиплексора, состоящая из первого и второго информационных выходов, тактового выхода, выхода сигналов апертуры и выходов сигналов цикла, соединена с входами соответствующего блока оконечной аппаратуры, при этом выход формирователя сигналов апертуры соединен с четвертым входом детектора сигналов синхронизации, второй выход которого соединен с вторым входом формирователя сигналов апертуры, отличающееся тем, что, с целью повышения помехоустойчивости приема пакетной информации, введены первый и второй блоки памяти, первый и второй блоки адресов записи, первый и второй ключи, последовательно соединенные первые перемножитель и интегратор, и последовательно соединенные вторые перемножитель и интегратор, блок сравнения, инвертор, блок адресов считывания, первый и второй элементы задержки и элемент ИЛИ, причем первый и второй информационные выходы демодулятора соедине

ны с первым и вторым входпни первого и второго блоков памяти, первый выход первого блока памяти соединен с первым входом первого ключа, выход которого соединен с первым информационным входом демультиплексора, второй выход первого блока памяти соединен с первым входом второго ключа, выход которого соединен с вторым информационным входом демультиплексора, выходы сигналов апертуры каждой группы выходов которого соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первыми вхо дами первого и второго блоков адресов записи, вторыми входами первого и второго интеграторов и входом первого элемента задержки, выход которого соединен с первым входом блока адресов считывания, выход которого соединен с третьими входами первого и второго блоков памяти, первый и второй выхо- ды второго блока памяти соединены соответственно с вторыми входами пер- вого и второго ключей, при этом так

товый выход демодулятора соединен с первыми входами первого и второго перемножителей, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами блока сравнения, первый выход которого соединен с третьими входами первого и второго ключей, второй выход блока сравнения соединен с четвертыми входа1 и первого и второго кшочей, выход блока синхронизации соединен с входом инвертора и вторыми входами первого перемножителя, блока адресов считывания и первого блока адресов записи, выход которого соединен с четвертым входом первого блока памяти, выход инвертора соединен с вторыми входами второго перемножителя и второго блока адресов записи, выход которого соединен с четвертым входом второго блока памяти, третий выход детектора Сигналов синхронизации соединен с входом второго элемента задержки, выход которого соединен с входом сигналов цикла демультиплексора.

| Патент США № 3730998, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР № 1178296, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1986-10-14—Подача