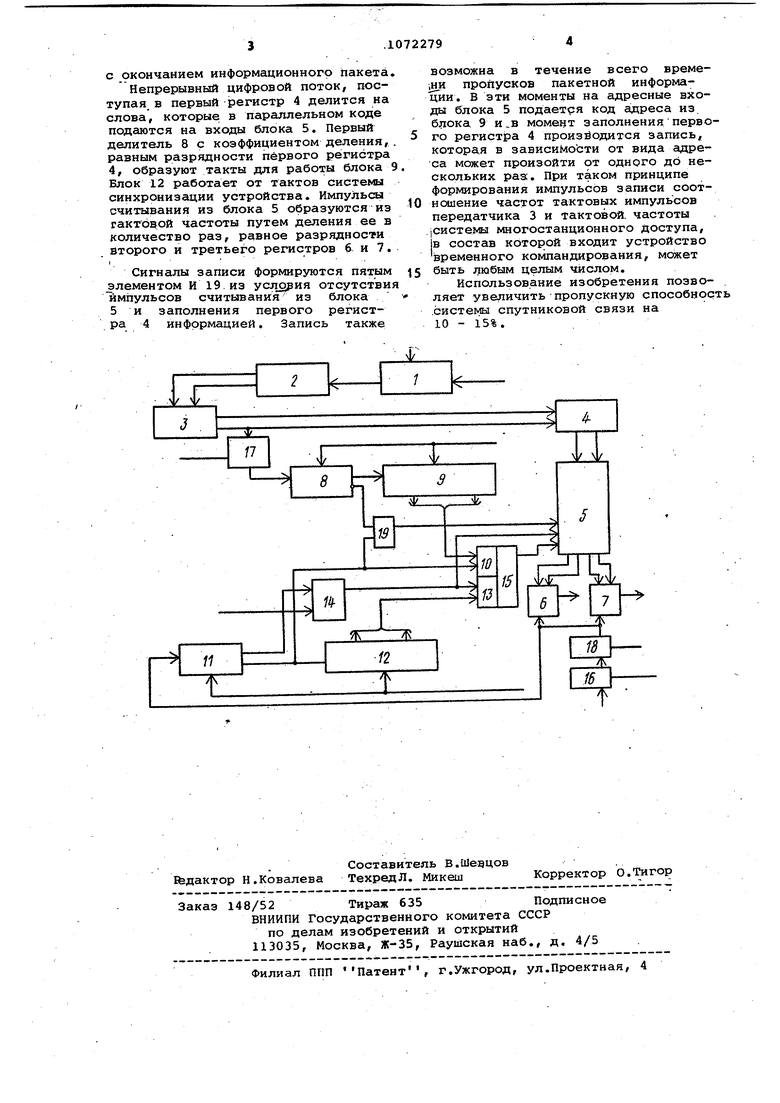

Изобретение относится к радиотех нике и связи и может быть использовано в системах передачи информации с временным разделением каналов, в частности в спутниковых системах связи с многостанционным доступом в Стволе ретранслятора. Известно устройство для временно го компандирования, содержащее па раллельно соединенные динамические сдвигающие регистры, блок управлеНИИ записью и источник информации, выходы которого соединены с входами динамических сдвигающих регистров l Недостатком данного устройства для временного компандирования явля ется низкая пропускная способность. Наиболее близким к предлагаемому является устройство для временного компандирования, содержащее последо вательно соединенные блок управляемойЗадержки, блок фазовой автоподстройки частоты, передатчик, первый регистр, блок памяти, выходы которо го соединены .с входами второго и Iтретьего регистров, управляющие вхо ды которых объединены, последовател но соединенные первый делитель частоты и блок перебора адресов записи, выход которого соединен с первым входом первого элемента И, последовательно соединенные второй делитель частоты и блок перебора адресов считывания, выход которого соединен с первым входом второго элемента И, причем инверсный выход второго делителя частоты через третий элемент И соединен с вторым вхо доМ второго элемента И и с входом считывания блока памяти, -выходы первого и второго, элементов И через элемент ИЛИ соединены с управляющим входом блока памяти, синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены между собой, синхронизирующие входы второго делителя часто ты и блока перебора адресов считыва ния соединены между собой, а также четвертый элемент И 2 . . Недостатком известного устройства для временного компандирования является низкая прогтускная способность из-за наличия жесткой связи между сигналами считывания и записи в блоке памяти. Цель изобретения - повышение пропускной способности. Поставленная цель достигается тем что в устройство для временного компандирования, содержащее последовательно соединенные блок управляемой задержки, блок фазовой автоподстройки частоты, передатчик, первый регистр, блок памяти, выходы которого соединены с входами второго и третье го регистров, управляющие входы кото рых объединены, последовательно соединенные первый делитель частоты и блок перебора адресов записи, выход которого соединен с -первым .входом первого элемента И, последовательно соединенные второй делитель частоты и блок перебора адресов считывания, выход которого соединен с первым входом второго элемента И, причем инверсный выход второго делителя частоты через третий элемент И соединен с вторым входом второго элемента И и с входом считывания блОка памяти; выходы первого и второго элементов И через элемент ИЛИ соединены с управляющим входом блока памяти, синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены между собой, синхронизирующие входы второго делителя частоты и блока перебора адресов считывания соединены между собой, а также четйертый элемент И, введены два элемента запрета и пятый элемент И, причем первый элемент- запрета включён между тактовым выходом передатчика я входом первого делителя частоты, управляющий вход первого элемента запрета соединен с входом Огибактщая пропусков низкочастотной информации устройства, второй элемент запрета включен между выходом четвертого элемента И и управляющими входами второго и третьего регистров, которые также соединены с входом второго делителя частоты, выход коTOi oro через пятый элемент И соединен с входом запись блока памяти, а второй вход пятого элемента И соединен с инверсным выходом первого делителя частоты. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство содержит блок 1 управляемой задержки, блок 2 фазовой автопоДстройки частоты, передатчик ,3, первый регистр 4, блок 5 памяти, второй регистр 6, третий регистр 7, первый . делитель 8 частоты, блок 9 перебора адресов записи, первый элемент И 10, второй делитель 11 частоты, блок 12. перебора адресов считывания, второй элемент И 13, третий элемент И 14, элемент ИЛИ 15, четвертьй элемент И 16, первый элемент 17 запрета, второй элемент 18 запрета, пятый элемент И 19. Устройство работает следующим образом. На вход блока 1 поступают импуль сы с цикловой частотой передачи, на управляющий вход данного блока поступает огибающая информационного пакета . С выхода блока 1 сигнал формы меандр поступает на блок 2, фаза которого совпадает с фазой цикла накопления. Таким образом, окончание цикла накопления совпадает по фазе

с ркончанием информационного пакета. Непрерывный цифровой поток, поступая в первый регистр 4 делится на слова, которые в параллельном коде подаются на входы блока 5. Первый делитель 8 с коэффициентом деления,. равным разрядности первого регистра 4, образуют такты для работы блока 9, Блок 12 работает от тактов системы синхронизации устройства. Импульсы считывания из блока 5 образуются из гактоцой частоты путем деления ее в количество раз, равное разрядности второго и третьего регистров 6 и 7.

i - .

Сигналы записи формируются пятым лементом И 19 из услория отсутствия импульсов считывания из блока 5 и заполнения первого регистра 4 информацией. Запись также

/7

возможна в течение всего времеjHH пропусков пакетной информации. В эти моменты на адресные входы блока 5 подается код адреса из б:г1ока 9 и.в момент заполнения первого регистра 4 производится запись, которая в зависимости от вида адреса может произойти от одного до нескольких раз. При таком принципе формирования импульсов записи соот0 ношение частот тактовых импульсов передатчика 3 и тактовой, частоты .(Системы многостанционного доступа, в состав которой входит устройство временного компандирования, может

5 быть любым целым числом.

Использование изобретения позволяет увеличить пропускную способность .системы спутниковой связи на 10 - 15%.

Ф

W Х/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для временного компандирования информации | 1980 |

|

SU930714A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Система временного компандирования | 1981 |

|

SU1078647A1 |

| Устройство приема пакетной информации системы спутниковой связи | 1986 |

|

SU1506561A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для контроля инкубаторов | 1983 |

|

SU1212394A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| Устройство для передачи и приема цифровой информации | 1987 |

|

SU1481832A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1243159A2 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО КОМПАНДИРОВАНИЯ, содержащее последовательно соединенные блок управл яемой задержки, блок фазовой. автоподстройки частоты, передатчик, первый регистр; блок памяти, выходы которого соединены с входами второго и третьего регистров, управляющие входы которых объединены, последовательно соединенные первый делитель частоты и блок перебора адресов записи, выход которого сЬединен с первым входом первого элемента И, последовательно соединенные второй делитель частоты и блок nepedqpai адресов считывания, выход которого соединен с первым входом второго элемента. И, причем инверсный выход второго делителя частоты через третий ,элемент И соединен с вторым входом ; второго элемента И. и с входом считывания блока памяти, выходы первого и второго элементов И через элемент .ИЛИ соединены с управлякхцим входом блока памяти,синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены собой, синхронизирующие входы второго делителя частоты и блока перебора адресов счишвания соединены между собой, а также четвертый элемент И, о.тличающееся тем, что, с целью повышения пропускной способности, в него введены два элемента запрета и пятый элемент И, причем пер)Ый элемент запрета включен между тактовым выводом пе редатS чика и входом первого делителя частоты, управляюодай вход первого элемерта запрета соединен с входом Огибающая пропусков низкочастотной информации устройства, второй элемент запрета включен между выходом четвертого элемента И и управляющими входами второго и третьего регистров, которые также соединены с входом второго делителя частоты, вькод которого через пятый элемент D ч И соединен с входом запись блока .памяти, а второй вход пятого элемента И соединен с инверсным выходом riepSD 0 вого делителя частоты. ;о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент QUA 3778795, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для временного компандирования информации | 1980 |

|

SU930714A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-07—Публикация

1981-09-25—Подача