1

Изобретение относится к радио- технике и может быть использовано для статистического моделирования систем передачи дискретных, сообщений.

Известны устройства моделирования состояний канала на основе процессов восстановления и накопления 11,

Однако эти устройства не позволяют воспроизвести всю сложную закономерность возникновения ошибок в реальных каналах связи, ,

Наиболее близким по технической сущности к предлагаемому является имитатор стационарного симметричного канала, содержащий М + 1 источников хэшибок, различающихся числейными значениями параметров модели, выходы которых подключены к входам источника марковского коммутирующего процесса, а выход с входом сумматора по.модулю два, на второй вход которого подаются информационные символы 2.

Недостатком данного имитатора является то, что в нем используется М + 1 независимых -источников ошибок что делает устройство сложным в реализации и, следовательно, ненещежным.

Цель изобретения - упрощение имитатора.

поставленная цель достигается тем, что в известный имитатор дискретного канала связи, содержащий cyMTvidTOp по модулю два, выход и первый вход которого являются соответственно выходом и- первым входом имитатора, блок синхронизации,первый

o вход которого является вторым входом имитатора, а выход блока синхронизации соединен с входом х енератора марковской последовательности, первый выход которого соединен с втоsрым входом блока синхронизации и с входом датчика случайных чисел, введены блок промежуточной памяти, пороговый сумматор.и элемент И, выход которого соединен с вторым входом

0 сумматора по. модулю два, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последова5тельности, третий выход которого через блок промежуточной памяти соединен .с первым входом порогового сумматора, второй вход которого подключен к выходу датчика случайных

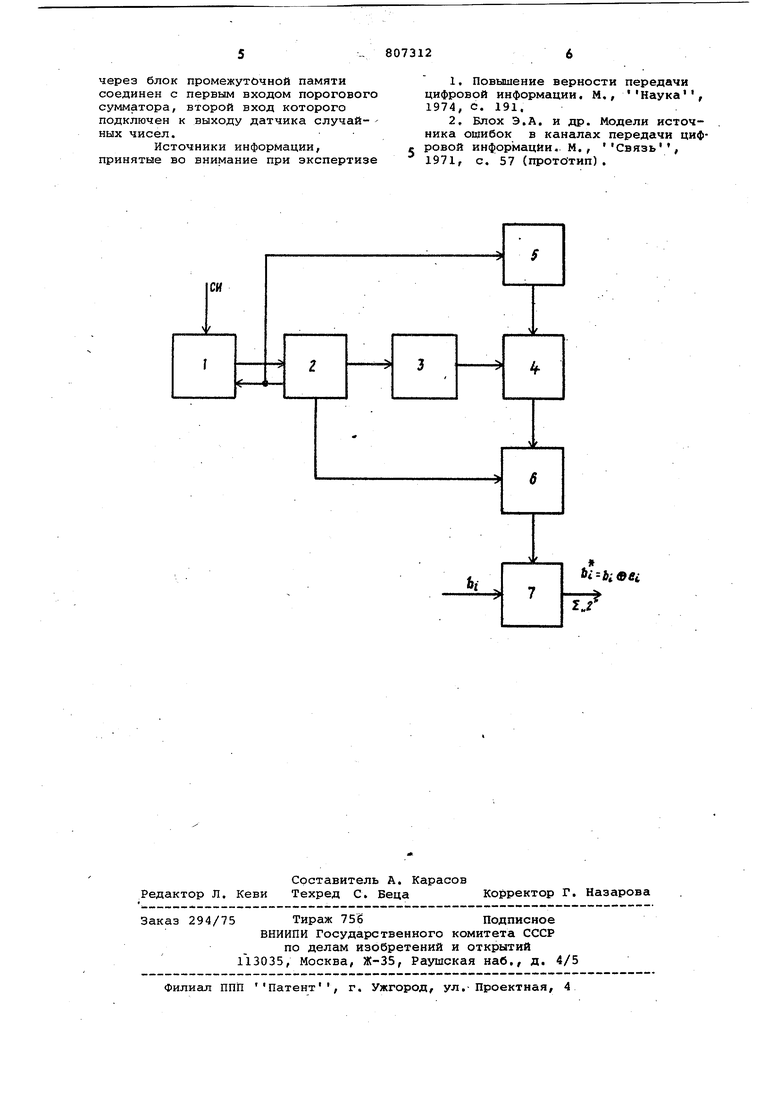

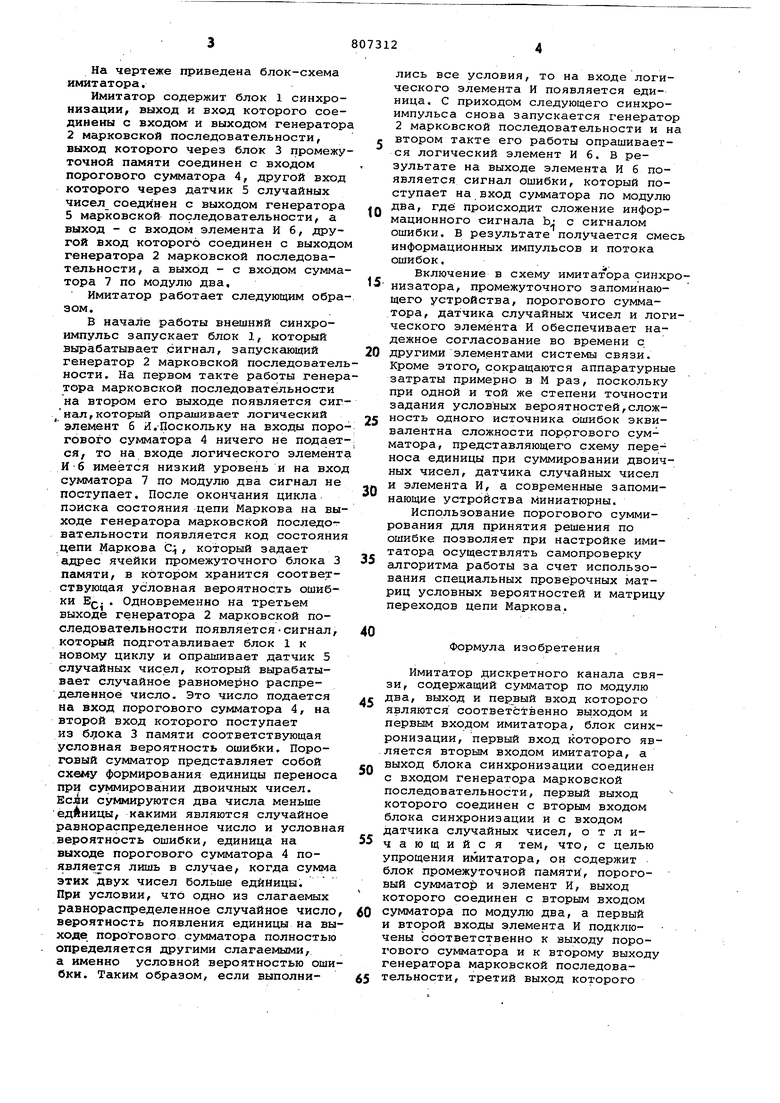

0 чисел. На чертеже приведена блок-схема имитатора. Имитатор содержит блок 1 синхронизации, выход и вход которого соединены с ВХОДОМ и выходом генератор 2 марковской последовательности, выход которого через блок 3 промежу точной памяти соединен с входом порогового сумматора 4, другой вход которого через датчик 5 случайных чисел соединен с выходом генератора 5 марковской последовательности, а выход - с входом элемента И б, другой вход которого соединен с выходо генератора 2 марковской последовательности, а выход - с входом сумма тора 7 по модулю два. Имитатор работает следующим обра зом, В начале работы внешний синхроимпульс запускает блок 1, который вырабатывает сигнал, запускающий генератор 2 марковской последовател ности. На первом такте работы генер тора марковской последовательности на втором его выходе появляется сиг нал,который опрашивает логический элемент б И,Поскольку на входы поро гового сумматора 4 ничего не подает ся, то на входе логического элемент И-б имеется низкий уровень и на вход сумматора 7 по модулю два сигнал не поступает. После окончания цикла поиска состояния цепи Маркова на вы ходе генератора марковской последовательности появляется код состояния цепи Маркова С , который задает адрес ячейки промежуточного блока 3 памяти, в котором хранится соответствующая условная вероятность ошибки EQ., Одновременно на третьем выходе генератора 2 марковской последовательности появляетсясигнал, который подготавливает блок 1 к новому циклу и опрашивает датчик 5 случайных чисел, который вырабатывает случайное равномерно распределенное число. Это число подается на вход порогового сумматора 4, на второй вход которого поступает из 6j;iOKa 3 памяти соответствующая условная вероятность ошибки. Пороговый сумматор представляет собой схему формирования единицы переноса при суммировании двоичных чисел. Если суммируются два числа меньше единицы, какими являются случайное равнораспределенное число и условная вероятность ошибки, единица на выходе порогового сумматора 4 появляется лишь в случае, когда сумма этих двух чисел больше единицы, При условии, что одно из слагаемых равнораспределенное случайное число вероятность появления единицы на выходе порогового сумматора полностью определяется другими слагаемыми, а именно условной вероятностью ошибки. Таким образом, если выполнилиев все условия, то на входе логического элемента И появляется единица, С приходом следующего синхроимпульса снова запускается генератор 2 марковской последовательности и на втором такте его работы опрашивается логический элемент И 6, В результате на выходе элемента И 6 появляется сигнал ошибки, который поступает на вход сумматора по модулю два, где происходит сложение информационного сигнала Ь- с сигналом ошибки, В результате получается смесь информационных импульсов и потока ошибок. Включение в схему имитатора синхронизатора, промежуточного запоминающего устройства, порогового сумматора, датчика случайных чисел и логического элемента И обеспечивает надежное согласование во времени с другими элементами системы связи. Кроме этого, сокращаются аппаратурные затраты примерно в М раз, поскольку при одной и той же степени точности задания условных вероятностей,сложность одного источника ошибок эквивалентна сложности порогового сумматора, представляющего схему переноса единицы при суммировании двоичных чисел, датчика случайных чисел и элемента И, а современные запоминающие устройства Миниатюрны, Использование порогового суммирования для принятия решения по ошибке позволяет при настройке имитатора осуществлять самопроверку алгоритма работы за счет использования специальных проверочных матриц условных вероятностей и матрицу переходов цепи Маркова, Формула изобретения Имитатор дискретного канала связи, содержащий сумматор по модулю два, выход и первый вход которого являются соответственно выходом и первым входом имитатора, блок синхронизации, первый вход которого является вторым входом имитатора, а выход блока синхронизации соединен с входом генератора марковской последовательности, первый выход которого соединен с вторым входом блока синхронизации и с входом датчика случайных чисел, отличающийся тем, что, с целью упрощения имитатора, он содержит блок промежуточной памяти , пороговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по модулю два, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последовательности, третий выход которого

через блок промежуточной памяти соединен с первым входом порогового сумматора, второй вход которого подключен к выходу датчика случайных чисел.

Источники информации, принятые во внимание при экспертизе

1.Повышение верности передачи цифровой информации. М., Наука, 1974, с. 191.

2,Блох Э.А. и др. Модели источника ошибок в каналах передачи цифровой информации. М., Связь, 1971, с. 57 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретного канала связи | 1988 |

|

SU1562926A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

Авторы

Даты

1981-02-23—Публикация

1978-10-23—Подача