Э

Ы У1

N3 Ч

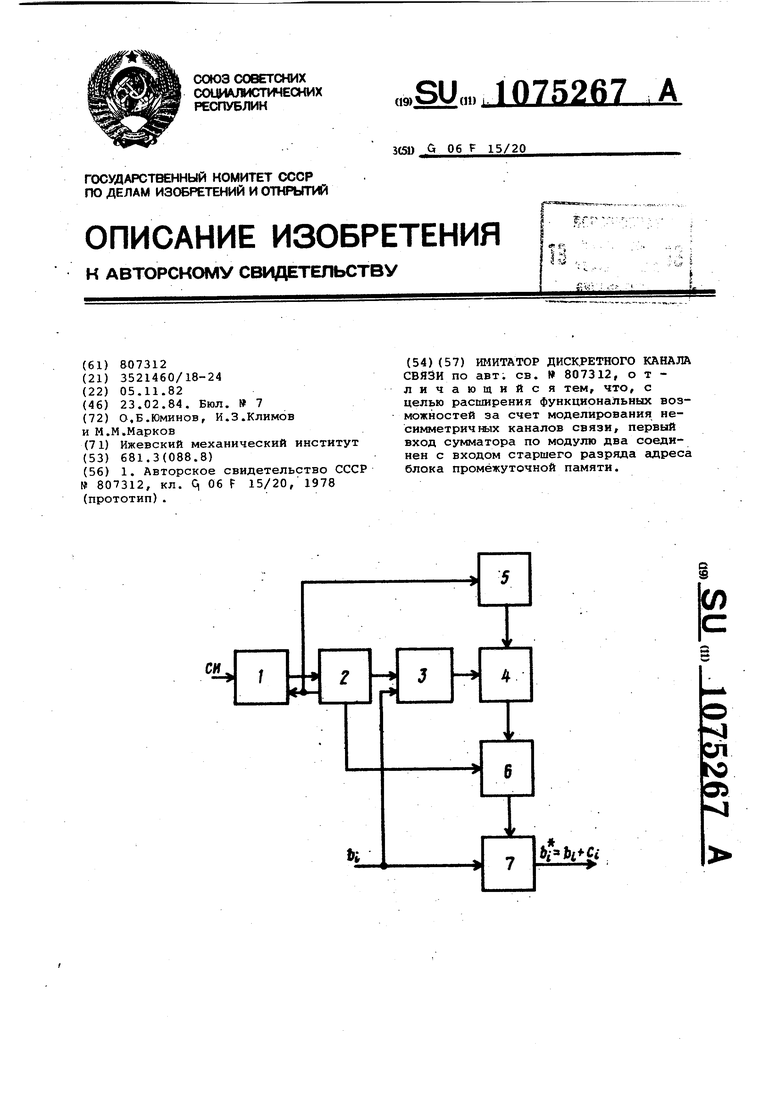

t . bi bji-Ci Изобретение относится к радиотех нике и может быть использовано для анализа помехоустойчивости систем передачи дискретных сообщений. По основному авт. св. 807312 известен имитатор дискретного канал связи, содержащий сумматор по модулю два, выход и первый вход которого являются соответственно выходом и первым входом имитатора, блок син хронизации, первый вход которого является вторым входом имитатора, а выход блока синхронизации соединен со входом генератора марковской последовательности, первый выход которого соединен с вторым входом блока синхронизации и с входом датчика случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по мо дулю два, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последовательности, третий выход которого через блок промежуточной памяти соединен с первым входом .порогового сумматора, второй вход которого подключен к выходу датчика случайных чисел l , Недостатком известного имитатора является то, что он моделирует ошиб ки трансформации только в симметрич ном канале и не учитывает несимметричность дискретного канала, котора проявляется в том, что вероят юсть преобразования нуля в единицу и еди ницы в нуль разная, что снижает Достоверность моделирования дискретно канала. Целью изобретения является расши рение функциональных возможностей имитатора за счет моделирования несимметричных каналов связи. Цель достигается тем, что в имитаторе первый вход сумматора по модулю два соединен со входом старшего разряда адреса блока промежуточной памяти. На чертеже приведена структурная схема имитатора. - Имитатор содержит блок 1 синхронизации, выход и второй вход которо го соединены со входом и первым выходом генератора 2 марковской после довательйости, третий выход которого соединен с входом блока 3 промежуточной памяти, выход которого сое динен с одним входом порогового сум матора 4, другой вход которого чере датчик 5 случайных чисел соединен с третьим выходом генератора 2 марков ской последовательности, элемент И первый вход которого соединен с выходом порогового «55мматора 4, а выход - с вторым входом сумматора 7 п модулю два, первый вход которого соединен со входом старшего разряда адреса блока 3 промежуточной памяти. Имитатор работает следующим образом. В начале работы запускает.ся блок 1, который вырабатывает сигнал, запускающий генератор 2 марковской последовательности. После окончания цикла поиска состояния цепи Маркова на выходе генератора марковскойпоследовательности появляется код состояния, который задает младшие разряды адреса ячейки блока 3 промежуточной памяти. Старший разряд адреса определяется входной информацией Ь; . Если , то для данного сортояния цепи Маркова выбирается ячейка памяти, в которой записана вероятность преобразования из О в если , то для того же состояния цепи Маркова выбирается ячейка памяти, в которой записана вероятность преобразования из i в О. Одновременно с опросом блока 3 на выходе генератора 2 марковской последовательности появляется сигнал, который подготавливает блок 1 к новому циклу и опрашивает датчик 5 случайных чисел, который вырабатывает случайное равномерно распределенное число. Это число подается на второй вход порогового сумматора 4, на первый вход которого поступает из блока 3 соответствующая условная вероятность ошибки. 11 Пороговый сумматор вырабатывает единицу на выходе при условии, что сумма слагаемых на его входах превысит единицу. В остальных случаях на выходе порогового сумматора нуль. Если одно из слагаемых - равнордспределенное случайное число, то вероятность появлениу единицы на выходе порогового сумматора 4 полностью определяется величиной другого слагаемого, а именно, условной вероятностью ошибки в символе. Сформированные таким образом либо единица, либо нуль с выхода порогового сумматора 4 через элемент И 6, который стробируется сигналом с выхода генератора 2 марковской последовательности, поступают на вход сумматора 7 по модулю два, где происходит сложение информационного сигнала Ь, с сигналом ошибки Ь; .с приходом следующего синхроимпульса от блока 1 цикл работы повторяется. В результате получается смесь информационных импульсов и потока ошибок, причем трансформироваться в i и в О для данного состояния канала связи будут с разными вероятностями.

ЕСЛИ В ячейках памяти, относящих- Введение в схему имитатора связи

ся к одному и тому же состоянию цепимежду первьм входом сумматора по моМаркова, будут записаны одинаковыедалю два и входом старшего разряда

вероятности трансформации символов,адреса блока 3 позволяет генерирото в данном случае моделируется пе-вать ошибки как в симметричном, так

редача информации по симм етричному 5и в несимметричном каналах свяканалу связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1661788A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи | 1985 |

|

SU1324033A1 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1651293A1 |

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

ИМИТАТОР ДИСКРЕТНОГО КАНАЛА СВЯЗИ по авт; св. № 807312, о т личающийс я тем, что, с целью расширения функциональных воз можностей за счет моделирования несимметричных каналов связи, первый вход сумматора по модулю два соединен с входом старшего разряда адреса блока промежуточной памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-11-05—Подача