Изобретение относится к вычислительной технике, в частности к запо- минающим устройствам5 и может быть использовано для проведения автоматизированных испытаний блоков памя ти в условиях действия дестабилизирующих факторов

Цель изрбретё ия - повышение дос товерности контроля при испытаниях блоков памяти за увеличения объ ема дестабилизирующих факторов учи™ тываемых в процессе испытаний.

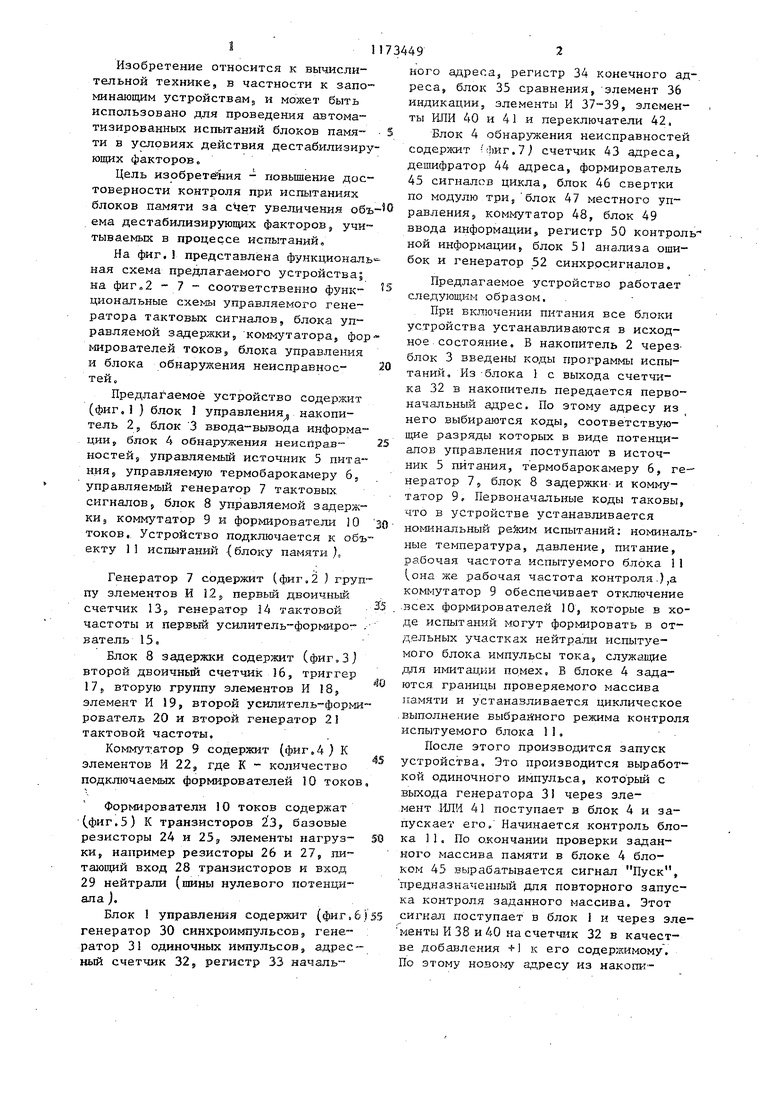

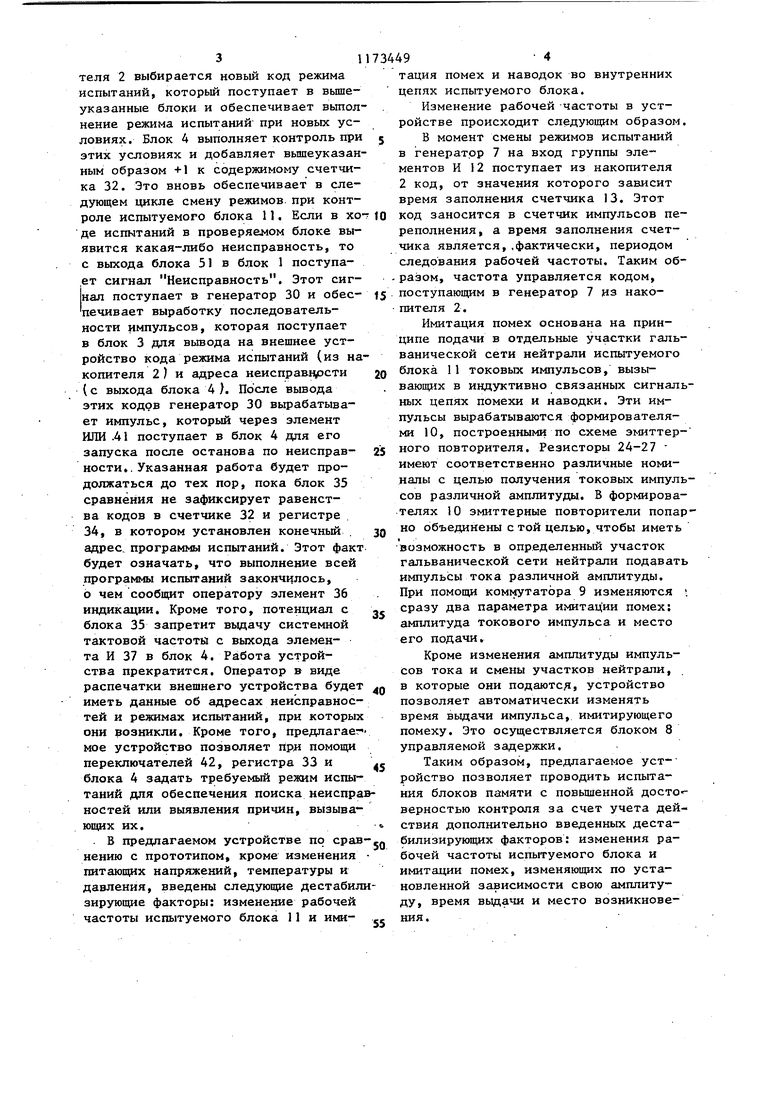

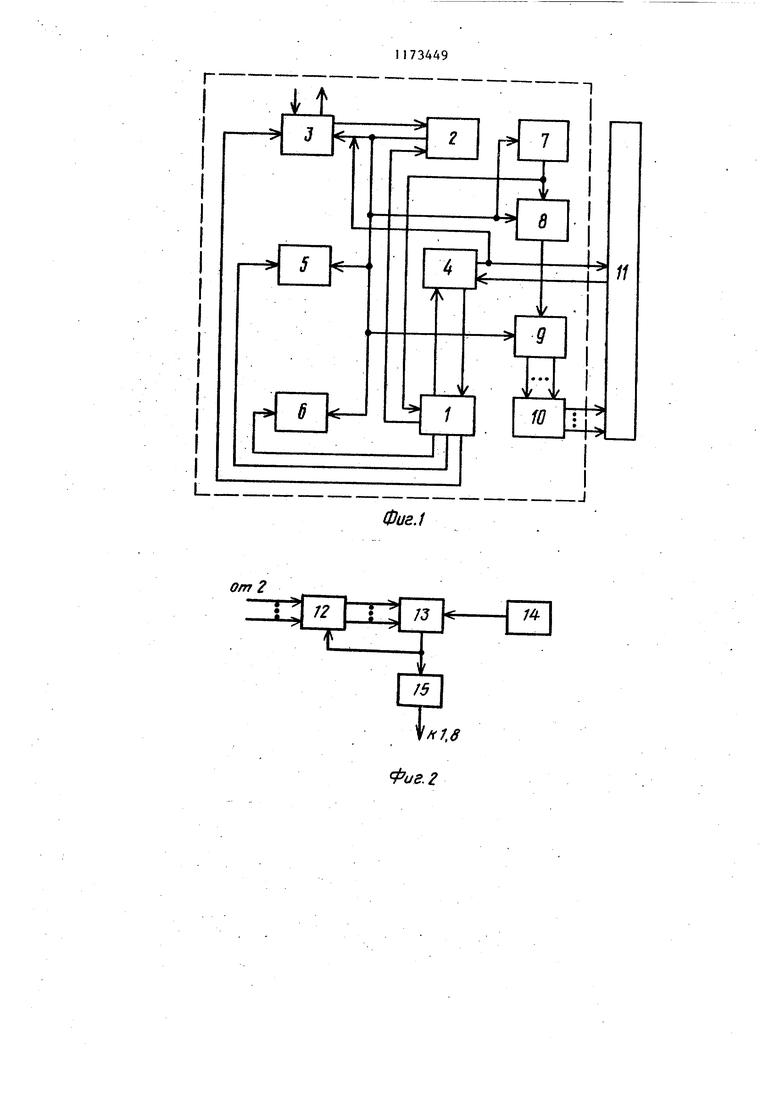

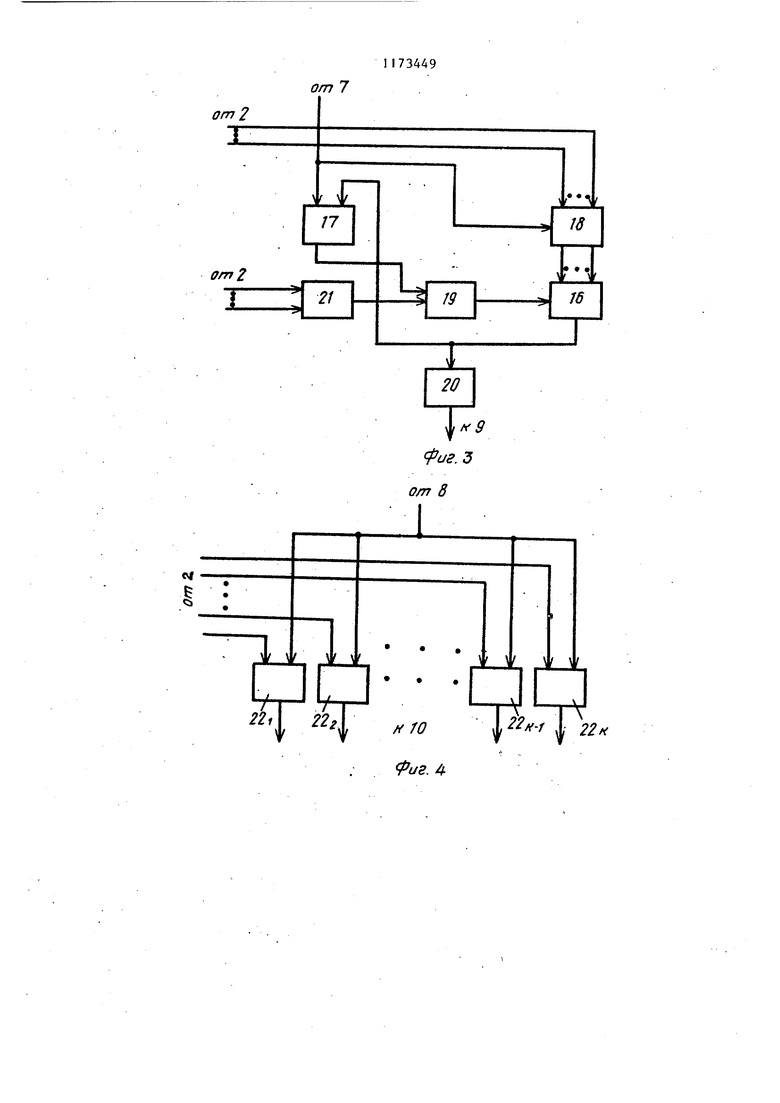

На фиг. представлена функциональная схема предлагаемого устройства; на фиг„2 - 7 - соответственно фзшкциональные схемы управляемого генератора тактовых сигналов, блока управляемой задержки, KOf-iMyTaTopa, формирователей токов, блока управления и блока обнаружения неисправноетей.

Предлагаемое устройство содержит (фиг,1 ) блок 1 управления накопитель 2, блок 3 ввода-вывода информации, блок 4 обнаружения неисйравностей, управляемьй источник 5 питания, управляемую термобарокамеру 6, управляемьй генератор 7 тактовых сигналов, блок 8 управляемой задержки j коммутатор 9 и формирователи 10 токов. Устройство подключается к объекту 1 1 испытаний { блоку памяти ),

Генератор 7 содержит (фиг.2 ) группу элементов И 12 первьш двоичный счетчик 13, генератор 14 тактовой частоты и первый усилитель-формирователгэ 15,

Блок 8 задержки содержит (фиг.З) второй двоичный счетчик 16, триггер 17f вторую группу элементов И IB, элемент И 19, второй усилитель-формирователь 20 и второй генератор 21 тактовой частоты.

Коммутатор 9 содержит (фиг.4} К элементов И 22, где К - количество подключаемых формирователей 10 токов

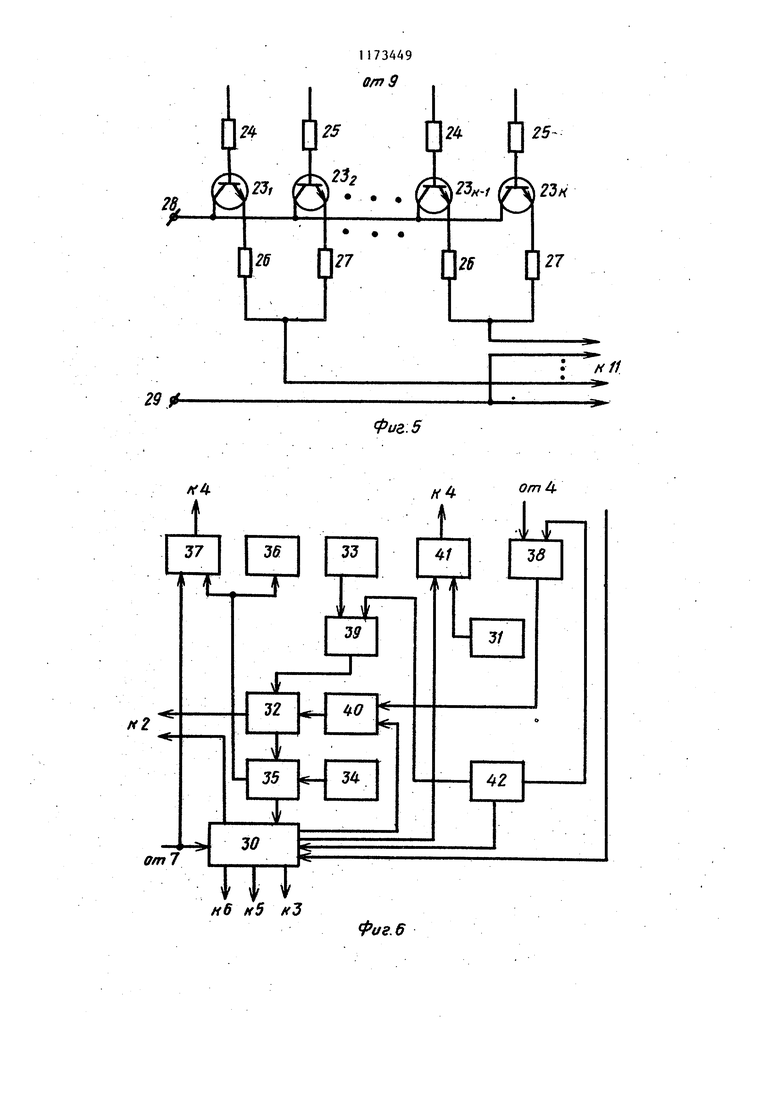

Формирователи 10 токов содержат (фиг.5) К транзисторов 2f3, базовые резисторы 24 и 25 элементы нагрузки, например резисторы 26 и 27, питающий вход 28 транзисторов и вход 29 нейтрали (шины нулевого потенциала ),

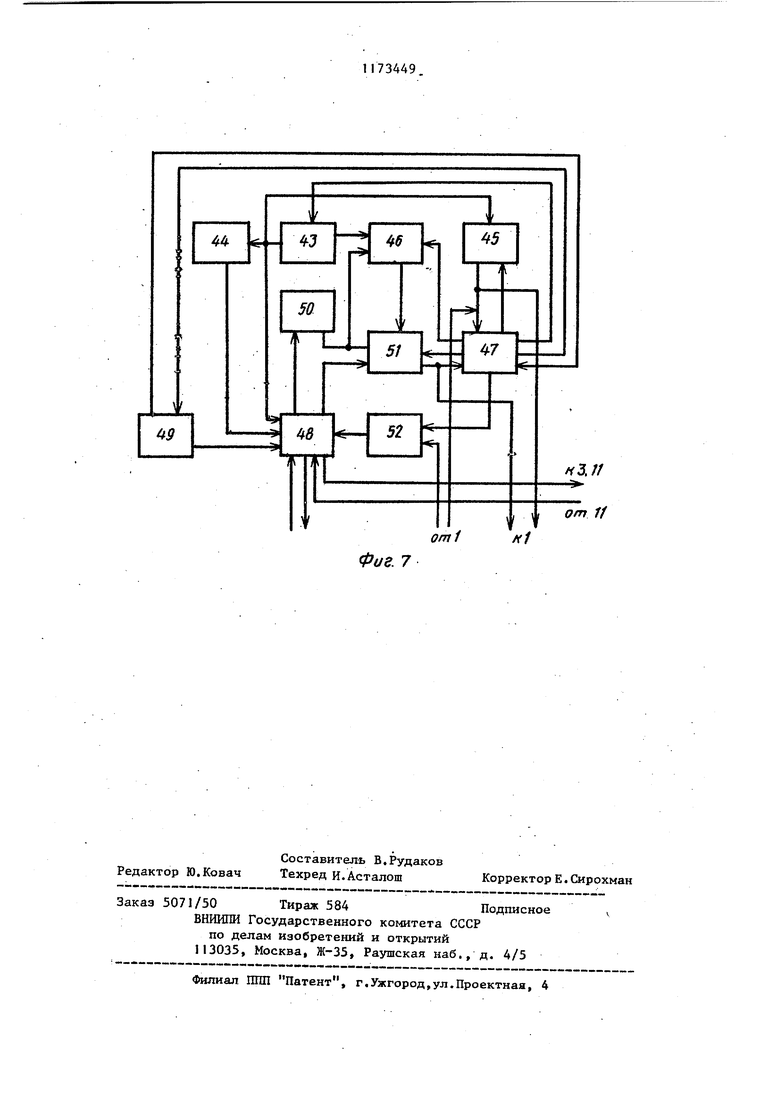

Блок 1 управления содержит (фиг.6 генератор 30 синхроимпульсов генератор 31 одиночных импульсов, адресный счетчик 32, регистр 33 начального адреса, регистр 34 конечного адреса, блок 35 сравнения, элемент 36 индикации, элементы И 37-39, элементы ИЛИ 40 и 41 и переключатели 42.

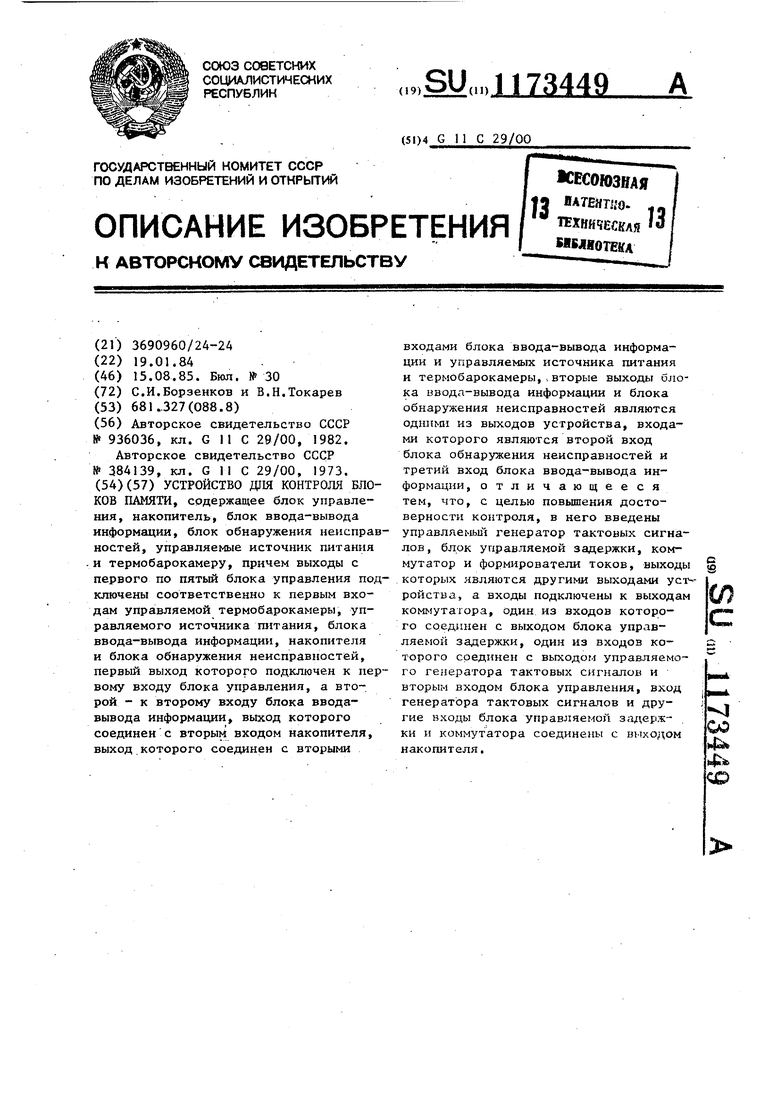

Блок 4 обнаружения неисправностей содержит фиг.7 счетчик 43 адреса, дешифратор 44 адреса, формирователь 45 сигналов цикла, блок 46 свертки по модулю три,блок 47 местного управления, коммутатор 48, блок 49 ввода информации, регистр 50 контрольной информации, блок 51 анализа ошибок и генератор 52 синхросигналов.

Предлагаемое устройство работает следующим образом.

При включении питания все блоки устройства устанавливаются в исходное состояние, В накопитель 2 черезблок 3 введены коды программы испытаний. Из -блока 1 с выхода счетчика 32 в накопитель передается первоначальный адрес. По этому адресу из него выбираются коды, соответствующие разряды которых в виде потенциалов управления поступают в источник 5 питания, термобарокамеру 6, генератор 7, блок 8 задержки-и коммутатор 9 Первоначальные коды таковы, что в устройстве устанавливается номинальный рейсим испытаний: номинальные температура, давление, питание, рабочая частота испытуемого блока 11 (она же рабочая частота контроля.),а коммутатор 9 обеспечивает отключение .всех формирователей 10, которые в ходе испытаний могут формировать в отдельных участках нейтрали испытуемого блока импульсы то.ка, служащие для имитации помех, В блока 4 задаются границы проверяемого массива памяти и устанавливается циклическое .выполнение выбранного режима контроля испытуемого блока 11.

После этого производится запуск устройства. Это производится выработкой одиночного импульса, который с выхода генератора 3 через элемент .МИ 41 поступает в блок 4 и запускает его. Начинается контроль блока 11. По о.кончании проверки заданного массива памяти в блоке 4 блоком 45 вьфабатывается сигнал Пуск, предназначенный для повторного запуска контроля заданного массива. Этот сигнал поступает в блок 1 и через элеMBHTbi И 38 и 40 на счетчик 32 в качестве добавления + к его содержимому. По этому новому адресу из накопителя 2 выбирается новый код режима испытаний, который поступает в вьше- указанные блоки и обеспечивает вьтол нение режима испытаний при новых условиях. Блок 4 выполняет контроль при этих условиях и добавляет вьшеуказан ным образом +1 к содержимому счетчика 32, Это вновь обеспечивает в следующем цикле смену режимов, при контроле испытуемого блока 11. Если в хо да испытаний в проверяемом блоке выявится какая-либо неисправность, то с выхода блока 51 в блок 1 поступает сигнал Неисправность. Этот сигнал поступает в генератор 30 и обеспечивает выработку последовательности импульсов, которая поступает в блок 3 для вывода на внешнее устройство кода режима испытаний (из на копителя 2 ) и адреса неисправности (с выхода блока 4 ). После вывода этих кодов генератор 30 вьфабатывает импульс, который через элемент ИЛИ .41 поступает в блок 4 для его запуска после останова по неисправности.. Указанная работа будет продолжаться до тех пор, пока блок 35 сравнения не зафиксирует равенства кодов в счетчике 32 и регистре 34, в котором установлен конечньй . адрес программы испытаний. Этот факт будет означать, что выполнение всей программы испытаний закончилось, о чем сообщит оператору элемент 36 индикации. Кроме того, потенциал с блока 35 запретит выдачу системной тактовой частотй с выхода элемента И 37 в блок 4. Работа устройства прекратится. Оператор в виде распечатки внешнего устройства будет иметь данные об адресах неисправностей и режимах испытаний, при которых они возникли. Кроме того, предлагаетмое устройство позволяет прл помощи переключателей 42, регистра 33 и блока 4 задать требуемый режим испытаний для обеспечения поиска неиспра ностей или выявления причин, вызыва ющих их. . в предлагаемом устройстве по срав нению с прототипом, кроме изменения питающих напряжений, температуры и давления, введены следующие дестабил зирующие факторы: изменение рабочей частоты испытуемого блока 11 и имитация помех и наводок во внутренних цепях испытуемого блока. Изменение рабочей -частоты в устройстве происходит следующим образом. В момент смены режимов испытаний в генератор 7 на вход группы элементов И 12 поступает из накопителя 2 код, от значения которого зависит время заполнения счетчика 13. Этот код заносится в счетчик импульсов переполнения, а время заполнения счетчика является,.фактически, периодом следования рабочей частоты. Таким образом, частота управляется кодом, поступающим в генератор 7 из накопителя 2. Имитация помех основана на принципе подачи в отдельные участки гальванической сети нейтрали испытуемого блока 11 токовых импульсов, вызывающих в индуктивно связанных сигнальных цепях помехи и наводки. Эти импульсы вырабатываются формирователями 10, построенными по схеме эмиттерного повторителя. Резисторы 24-27 имеют соответственно различные номиналы с целью получения токовых импульсов различной амплитуды. В формирователях 10 эмиттерные повторители попарно объединены с той целью, чтобы иметь возможность в определенный участок гальванической сети нейтрали подавать импульсы тока различной амплитуды. При помощи коммутатора 9 изменяются сразу два параметра имитации помех: амплитуда токового импульса и место его подачи. Кроме изменения амплитуды импульсов тока и смены участков нейтрали, в которые они подаютсд, устройство позволяет автоматически изменять время выдачи импульса, имитирующего помеху. Это осуществляется блоком 8 управляемой задержки. Таким образом, предлагаемое устройство позволяет проводить испытания блоков памяти с повышенной досто верностью контроля за счет учета действия дополнительно введенных дестабилизирующих факторов: изменения рабочей частоты испытуемого блока и имитации помех, изменяющих по установленной загвисимости свою амплитуду, время вьщачи и место возникновения .

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля памяти | 1984 |

|

SU1238164A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1336020A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ, содержащее блок управления, накопитель, блок ввода-вывода информации, блок обнаружения неисправностей, управляемые источник питания и термобарокамеру, причем выходы с первого по пятый блока управления подключены соответственно к первым входам управляемой термобарокамеры, управляемого источника питания, блока ввода-вывода информации, накопителя и блока обнаружения неисправностей, первый выход которого подключен к первому входу блока управления, а второй - к второму входу блока вводавывода информации, выход которого соединен с вторым входом накопителя, выход которого соединен с вторыми входами блока ввода-вывода информации и управляемых источника питания и термобарокамеры,.вторые выходы блока ввода-вывода информации и блока обнаружения неисправностей являются одн11№1 из выходов устройства, входами которого являются второй вход блока обнаружения неисправностей и третий вход блока ввода-вывода информации, отличающееся тем, что, с целью повышения достоверности контроля, в него введены управляемьш генератор тактовых сигналов, блок угфавляемой задержки, комi мутатор и формирователи токов, выходы которых являются другими выходами уст ройства, а входы подключены к выходам коммутатора, один из входов котороС го соединен с выходом блока управляемой задержки, один из входов которого соединен с выходом управляемого генератора тактовых сигналов и вторым входом блока управления, вход генератора тактовых сигналов и дру гие входы блока управляемой з;вдерж-00 ки и коммутатора соединены с выходом «4 накопителя. 4

от 2

-г12

-г/4

/J

-г/5 .

,8

Фиг. Z

Г

f

17

21

ц

j:

18

k

16

9

I

фиг. от 8

p.vyi

f i 22f

/f ГО

иг. 4

л4

м6 н5 кЪ .

фиг: 5

от 4

фиг. 6

О ml

/f/

Фиг. 7

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Солесос | 1922 |

|

SU29A1 |

| АВТОМАТИЧЕСКАЯ СИСТЕМА ДЛЯ ИСПЫТАНИЙ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 0 |

|

SU384139A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1985-08-15—Публикация

1984-01-19—Подача