Изобретение относится к вычислительной технике и может быть использовано для контроля блоков памяти.

Цель изобретения - повышение достоверности контроля и быстродействия устройства.

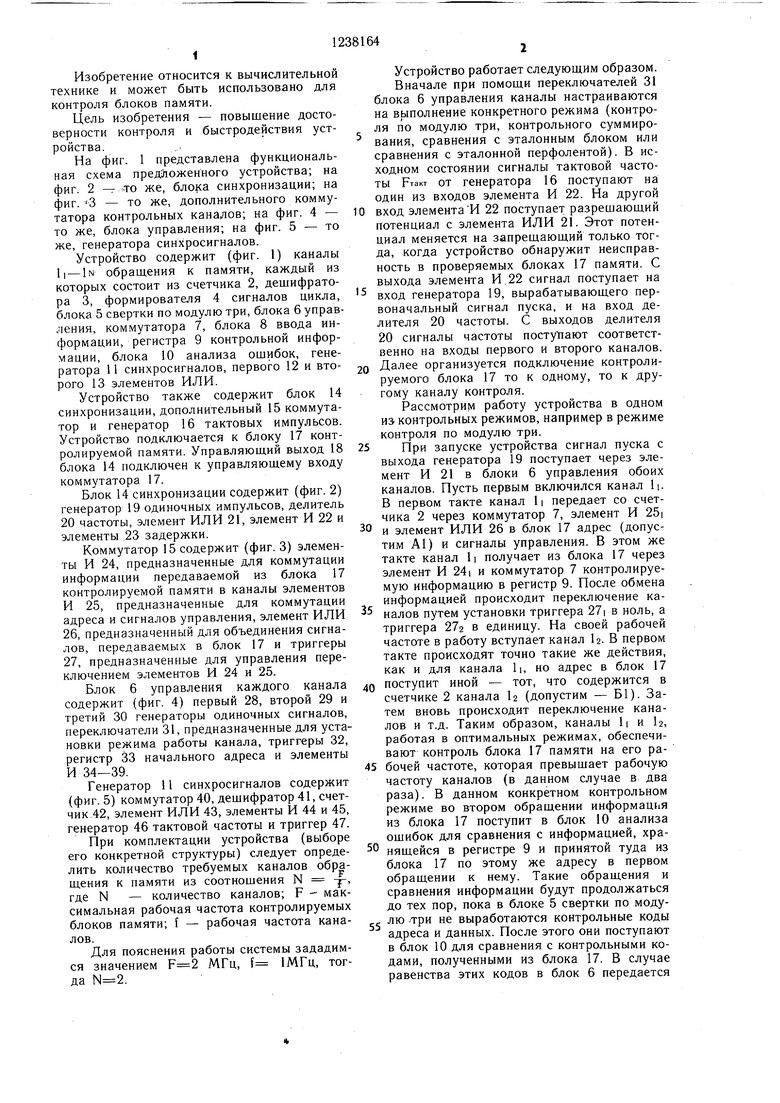

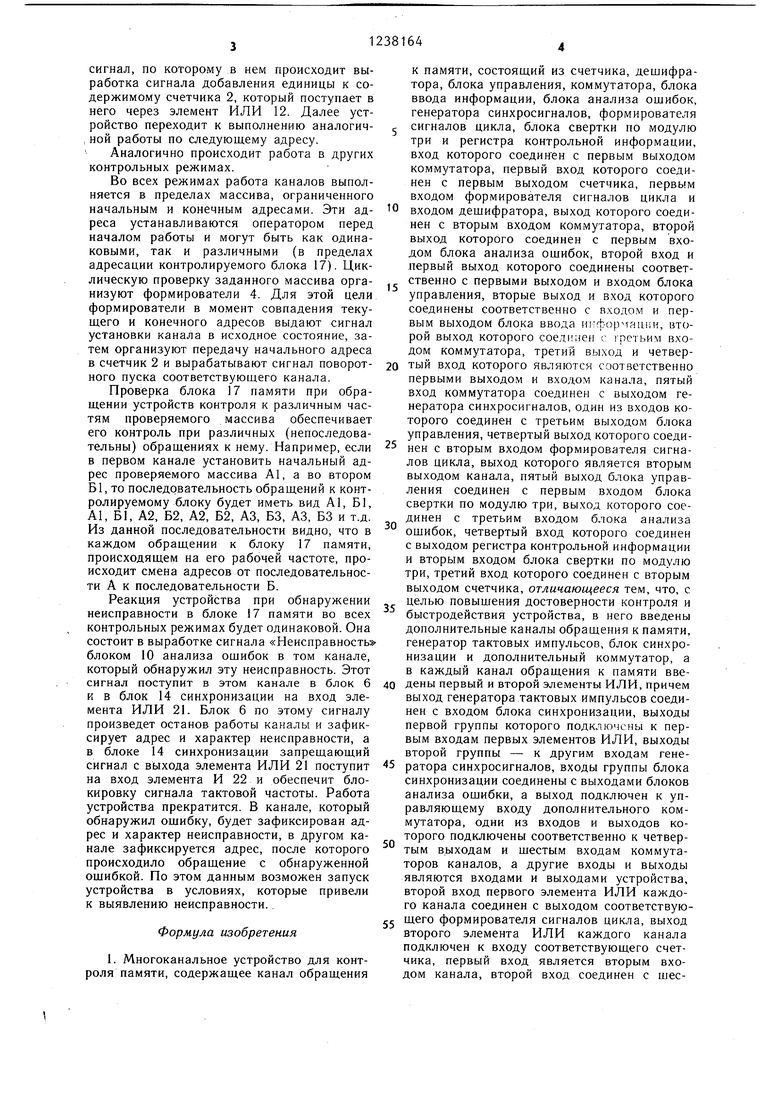

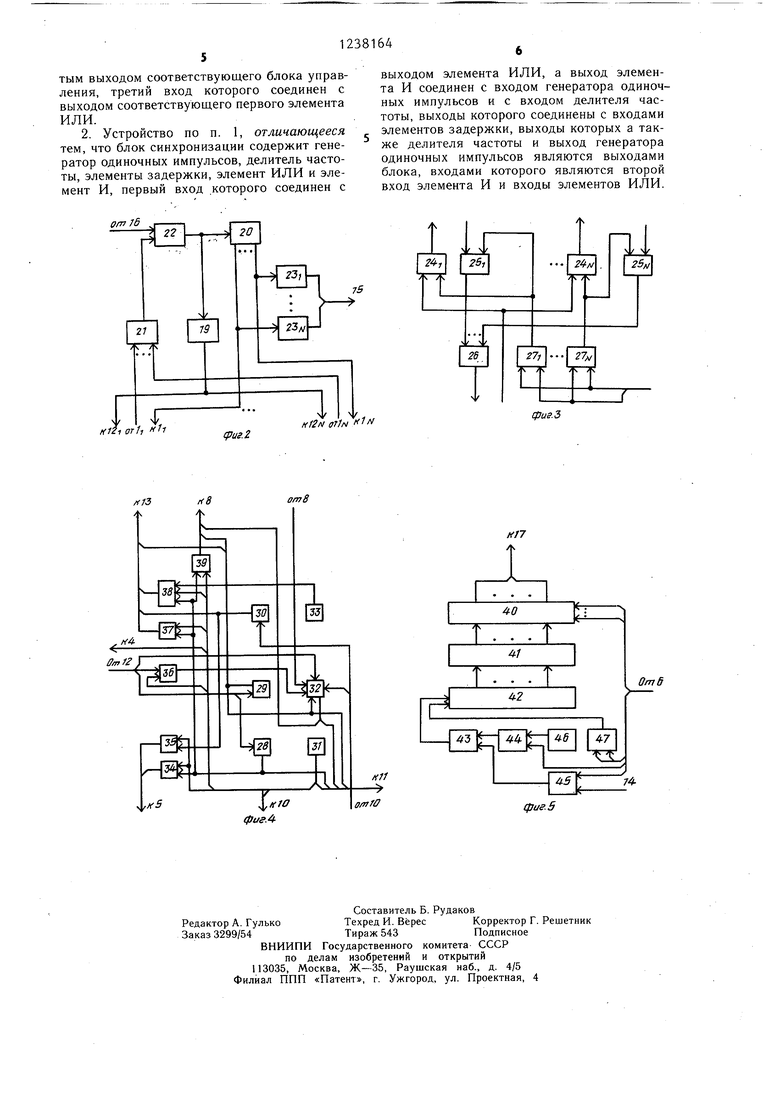

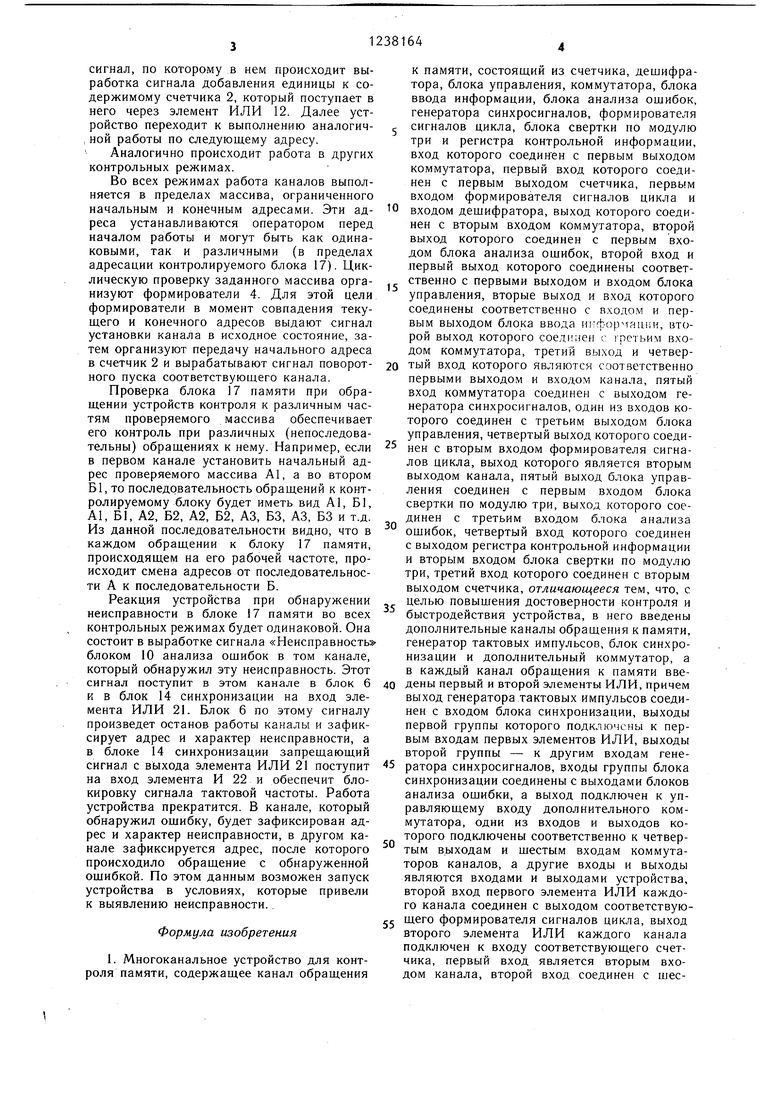

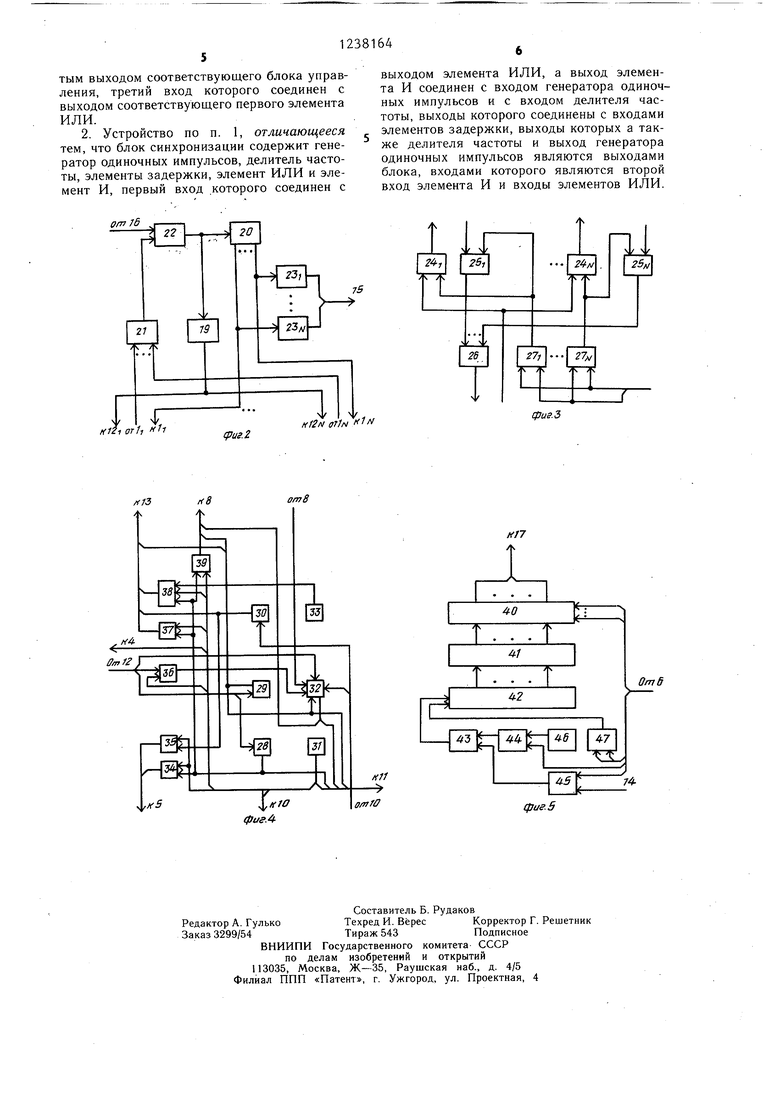

На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2 - то же, блока синхронизации; на фиг. 3 - то же, дополнительного коммуУстройство работает следующим образом.

Вначале при помощи переключателей 31 блока 6 управления каналы настраиваются на вьшолнение конкретного режима (контроля по модулю три, контрольного суммирования, сравнения с эталонным блоком или сравнения с эталонной перфолентой). В исходном состоянии сигналы тактовой частоты Ртакт от генератора 16 поступают на один из входов элемента И 22. На другой

татора контрольных каналов; на фиг. 4 - Ю вход элемента И 22 поступает разрешающий

то

то же, блока управления; на фиг. 5 же, генератора синхросигналов.

Устройство содержит (фиг. 1) каналы li - IN обращения к памяти, каждый из которых состоит из счетчика 2, дешифратопотенциал с элемента ИЛИ 21. Этот потенциал меняется на запрещающий только тогда, когда устройство обнаружит неисправность в проверяемых блоках 17 памяти. С выхода элемента И.22 сигнал поступает на

ра 3, формирователя 4 сигналов цикла, вход генератора 19, вырабатывающего пер- блока 5 свертки по модулю три, блока 6 управ- воначальный сигнал пуска, и на вход деления, коммутатора 7, блока 8 ввода ин-лителя 20 частоты. С выходов делителя формации, регистра 9 контрольной инфор-20 сигналы частоты поступают соответст- мации, блока 10 анализа ощибок, гене-венно на входы первого и второго каналов, ратора 11 синхросигналов, первого 12 и вто- jo Далее организуется подключение контроли- рого 13 элементов ИЛИ.руемого блока 17 то к одному, то к друУстройство также содержит блок 14гому каналу контроля,

синхронизации, дополнительный 15 коммутатор и генератор 16 тактовых импульсов. Устройство подключается к блоку 17 контролируемой памяти. Управляющий выход 18 25 блока 14 подключен к управляющему входу коммутатора 17.

Блок 14 синхронизации содержит (фиг. 2) генератор 19 одиночных импульсов, делитель 20 частоты, элемент ИЛИ 21, элемент И 22 и элементы 23 задержки.

Коммутатор 15 содержит (фиг. 3) элементы И 24, предназначенные для коммутации информации передаваемой из блока 17 контролируемой памяти в каналы элементов

Рассмотрим работу устройства в одном из контрольных режимов, например в режиме контроля по модулю три.

При запуске устройства сигнал пуска с выхода генератора 19 поступает через элемент И 21 в блоки 6 управления обоих каналов. Пусть первым включился канал li. В первом такте канал 1i передает со счетчика 2 через коммутатор 7, элемент И 25i 30 и элемент ИЛИ 26 в блок 17 адрес (допустим А1) и сигналы управления. В этом же такте канал 1 получает из блока 17 через элемент И 24i и коммутатор 7 контролируемую информацию в регистр 9. После обмена

И 25, предназначенные для коммутацииинформацией происходит переключение каадреса и сигналов управления, элемент ИЛИ налов путем установки триггера 27| в ноль, а 26, предназначенный для объединения сигна-триггера 27 в единицу. На своей рабочей

частоте в работу вступает канал Ь. В первом такте происходят точно такие же действия, как и для канала , но адрес в блок 17

Блок 6 управления каждого канала до поступит иной - тот, что содержится в содержит (фиг. 4) первый 28, второй 29 исчетчике 2 канала Ь (допустим - Б1). Залов, передаваемых в блок 17 и триггеры 27, предназначенные для управления переключением элементов И 24 и 25.

третий 30 генераторы одиночных сигналов, переключатели 31, предназначенные для установки режима работы канала, триггеры 32, регистр 33 начального адреса и элементы И 34-39.

Генератор 11 синхросигналов содержит (фиг. 5) коммутатор 40, дещифратор 41, счетчик 42, элемент ИЛИ 43, элементы И 44 и 45, генератор 46 тактовой частоты и триггер 47.

При комплектации устройства (выборе его конкретной структуры) следует определить количество требуемых каналов обращения к памяти из соотношения N -j-, где N - количество каналов; F - максимальная рабочая частота контролируемых

тем вновь происходит переключение каналов и т.д. Таким образом, каналы Ь и Ь, работая в оптимальных режимах, обеспечивают контроль блока 17 памяти на его ра45 бочей частоте, которая превышает рабочую частоту каналов (в данном случае в два раза). В данном конкретном контрольном режиме во втором обращении информация из блока 17 поступит в блок 10 анализа ощибок для сравнения с информацией, хра5 нящейся в регистре 9 и принятой туда из блока 17 по этому же адресу в первом обращении к нему. Такие обращения и сравнения информации будут продолжаться до тех пор, пока в блоке 5 свертки по модулов.

блоков памяти; f - рабочая частота кана- „ лю .три не выработаются контрольные коды

адреса и данных. После этого они поступают в блок 10 для сравнения с контрольными кодами, полученными из блока 17. В случае равенства этих кодов в блок 6 передается

Для пояснения работы системы зададимся значением МГц, f 1МГц, тогда .

Устройство работает следующим образом.

Вначале при помощи переключателей 31 блока 6 управления каналы настраиваются на вьшолнение конкретного режима (контроля по модулю три, контрольного суммирования, сравнения с эталонным блоком или сравнения с эталонной перфолентой). В исходном состоянии сигналы тактовой частоты Ртакт от генератора 16 поступают на один из входов элемента И 22. На другой

вход элемента И 22 поступает разрешающий

гому каналу контроля,

Рассмотрим работу устройства в одном из контрольных режимов, например в режиме контроля по модулю три.

При запуске устройства сигнал пуска с выхода генератора 19 поступает через элемент И 21 в блоки 6 управления обоих каналов. Пусть первым включился канал li. В первом такте канал 1i передает со счетчика 2 через коммутатор 7, элемент И 25i и элемент ИЛИ 26 в блок 17 адрес (допустим А1) и сигналы управления. В этом же такте канал 1 получает из блока 17 через элемент И 24i и коммутатор 7 контролируемую информацию в регистр 9. После обмена

информацией происходит переключение катем вновь происходит переключение каналов и т.д. Таким образом, каналы Ь и Ь, работая в оптимальных режимах, обеспечивают контроль блока 17 памяти на его рабочей частоте, которая превышает рабочую частоту каналов (в данном случае в два раза). В данном конкретном контрольном режиме во втором обращении информация из блока 17 поступит в блок 10 анализа ощибок для сравнения с информацией, хранящейся в регистре 9 и принятой туда из блока 17 по этому же адресу в первом обращении к нему. Такие обращения и сравнения информации будут продолжаться до тех пор, пока в блоке 5 свертки по модулю .три не выработаются контрольные коды

сигнал, по которому в нем происходит выработка сигнала добавления единицы к содержимому счетчика 2, который поступает в него через элемент ИЛИ 12. Далее устройство переходит к выполнению аналогич- ной работы по следующему адресу. Аналогично происходит работа в других контрольных режимах.

Во всех режимах работа каналов выполняется в пределах массива, ограниченного начальным и конечным адресами. Эти ад- реса устанавливаются оператором перед началом работы и могут быть как одинаковыми, так и различными (в пределах адресации контролируемого блока 17). Циклическую проверку заданного массива орга- низуют формирователи 4. Для этой цели формирователи в момент совпадения текущего и конечного адресов выдают сигнал установки канала в исходное состояние, затем организуют передачу начального адреса в счетчик 2 и вырабатывают сигнал поворот- ного пуска соответствующего канала.

Проверка блока 17 памяти при обращении устройств контроля к различным частям проверяемого массива обеспечивает его контроль при различных (непоследовательны) обращениях к нему. Например, если в первом канале установить начальный адрес проверяемого массива А1, а во втором Б1, то последовательность обращений к контролируемому блоку будет иметь вид А1, Б1, А1, Б1, А2, Б2, А2, Б2, A3, БЗ, A3, БЗ и т.д. Из данной последовательности видно, что в каждом обращении к блоку 17 памяти, происходящем на его рабочей частоте, происходит смена адресов от последовательности А к последовательности Б.

Реакция устройства при обнаружении неисправности в блоке 17 памяти во всех контрольных режимах будет одинаковой. Она состоит в выработке сигнала «Неисправность блоком 10 анализа ощибок в том канале, который обнаружил эту неисправность. Этот сигнал поступит в этом канале в блок 6 и в блок 14 синхронизации на вход элемента ИЛИ 21. Блок 6 по этому сигналу произведет останов работы каналы и зафиксирует адрес и характер неисправности, а в блоке 14 синхронизации запрещающий сигнал с выхода элемента ИЛИ 21 поступит на вход элемента И 22 и обеспечит блокировку сигнала тактовой частоты. Работа устройства прекратится. В канале, который обнаружил ощибку, будет зафиксирован адрес и характер неисправности, в другом канале зафиксируется адрес, после которого происходило обращение с обнаруженной ощибкой. По этом данным возможен запуск устройства в условиях, которые привели к выявлению неисправности. ,

Формула изобретения

I. Многоканальное устройство для контроля памяти, содержащее канал обращения

О , 0

5

0 5

5

к памяти, состоящий из счетчика, дещифра- тора, блока управления, коммутатора, блока ввода информации, блока анализа ощибок, генератора синхросигналов, формирователя сигналов цикла, блока свертки по модулю три и регистра контрольной информации, вход которого соединен с первым выходом коммутатора, первый вход которого соединен с первым выходом счетчика, первым входом формирователя сигналов цикла и входом дещифратора, выход которого соединен с вторым входом коммутатора, второй выход которого соединен с первым входом блока анализа ощибок, второй вход и первый выход которого соединены соответственно с первыми выходом и входом блока управления, вторые выход и вход которого соединены соответственно с входом и первым выходом блока ввода инф Ор чации, второй выход которого соединен с третьим входом коммутатора, третий выход и четвертый вход которого являются соответственно первыми выходом и входом канала, пятый вход коммутатора соединен с выходом генератора синхросигналов, один из входов которого соединен с третьим выходом блока управления, четвертый выход которого соединен с вторым входом формирователя сигналов цикла, выход которого является вторым выходом канала, пятый выход блока управления соединен с первым входом блока свертки по модулю три, выход которого соединен с третьим входом блока анализа ощибок, четвертый вход которого соединен с выходом регистра контрольной информации и вторым входом блока свертки по модулю три, третий вход которого соединен с вторым выходом счетчика, отличающееся тем, что, с целью повыщения достоверности контроля и быстродействия устройства, в него введены дополнительные каналы обращения к памяти, генератор тактовых импульсов, блок синхронизации и дополнительный коммутатор, а в каждый канал обращения к памяти введены первый и второй элементы ИЛИ, причем выход генератора тактовых импульсов соединен с входом блока синхронизации, выходы первой группы которого подключены к первым входам первых элементов ИЛИ, выходы второй группы - к другим входам генератора синхросигналов, входы группы блока синхронизации соединены с выходами блоков анализа ощибки, а выход подключен к управляющему входу дополнительного коммутатора, одни из входов и выходов которого подключены соответственно к четвертым выходам и щестым входам коммутаторов каналов, а другие входы и выходы являются входами и выходами устройства, второй вход первого элемента ИЛИ каждого канала соединен с выходом соответствующего формирователя сигналов цикла, выход второго элемента ИЛИ каждого канала подключен к входу соответствующего счетчика, первый вход является вторым входом канала, второй вход соединен с щестым выходом соответствующего блока управления, третий вход которого соединен с выходом соответствующего первого элемента ИЛИ.

2. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит генератор одиночных импульсов, делитель частоты, элементы задержки, элемент ИЛИ и элемент И, первый вход .которого соединен с

выходом элемента ИЛИ, а выход элемента И соединен с входом генератора одиночных импульсов и с входом делителя частоты, выходы которого соединены с входами элементов задержки, выходы которых а также делителя частоты и выход генератора одиночных импульсов являются выходами блока, входами которого являются второй вход элемента И и входы элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1173449A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Резервированное устройство для контроля и управления | 1991 |

|

SU1830535A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

Изобретение относится к . вычислительной технике и может быть использовано при контроле запоминающих устройств. Цель изобретения - повышение достоверности контроля и быстродействия устройства. Устройство содержит каналы Ь - IN обращения к памяти, подключаемые через коммутатор 15 к блоку 17 контролируемой памяти. Синхронизация работы каналов осуществляется блоком 14 синхронизации и генератором 16 тактовых импульсов. Контроль блока 17 осуществляется последовательным подключением к нему каналов, что позволяет вести контроль блока 17 на максимально допустимой для него рабочей частоте и при различных сочетаниях адресов. Устройство может работать в режимах контроля по модулю три, контрольного суммирования, сравнения с эталонной информацией. 1 з.п.ф-лы, 5 ил. СО 1C со 00 О5 4:

н1Эк 8

отВ

КП

От б

omfO

фае. 5

| Устройство для контроля блокапОСТОяННОй пАМяТи | 1979 |

|

SU799019A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-15—Публикация

1984-10-17—Подача