(5) ИНТЕГРАЛЬНАЯ МИКРОСХЕМА И Л МИКРОПРОЦЕССОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И СВЯЗИ | 2008 |

|

RU2400805C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для контроля импульсных параметров магнитных сердечников | 1981 |

|

SU981908A1 |

| УСТРОЙСТВО ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2221318C2 |

| Устройство для контроля сложных объектов | 1987 |

|

SU1509833A1 |

| Формирователь адресных токов | 1979 |

|

SU924752A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2005 |

|

RU2344532C2 |

| МИКРОПРОЦЕССОРНОЕ РЕЛЕЙНОЕ УСТРОЙСТВО ИМПУЛЬСНОЙ СИГНАЛИЗАЦИИ | 2000 |

|

RU2195707C2 |

1

Изобретение относится к микроэлектронике и может быть использовано при построении больших интегральных микросхем микропроцессоров на основе интенционной логики.

Известно устройство, построенное на элементах .изопланарной интенционной логики и содержащее оперативные блоки, узел управления и операционный регистр 1.

Известно таюхе устройство, построенное на элементах интенционной логики И Л содержащее К узлов опера.7ивных блоков, узел управления, имеющий К групп управляющих ,5 выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами оперативных блоков, управляющие выходы каждой i-й группы узла управления 20 соединены с управляющими входами соответствующей 1-й группы разрядов операционного регистра, управляющие выходы каждой i-й группы разрядов которого соединены с управлящими входами соответствующего }-го узла опе,рационных блоков С2.

Недостатками известных устройств является большая потребляемая мощность.

Цель изобретения - уменьшение потребляемой мощности.

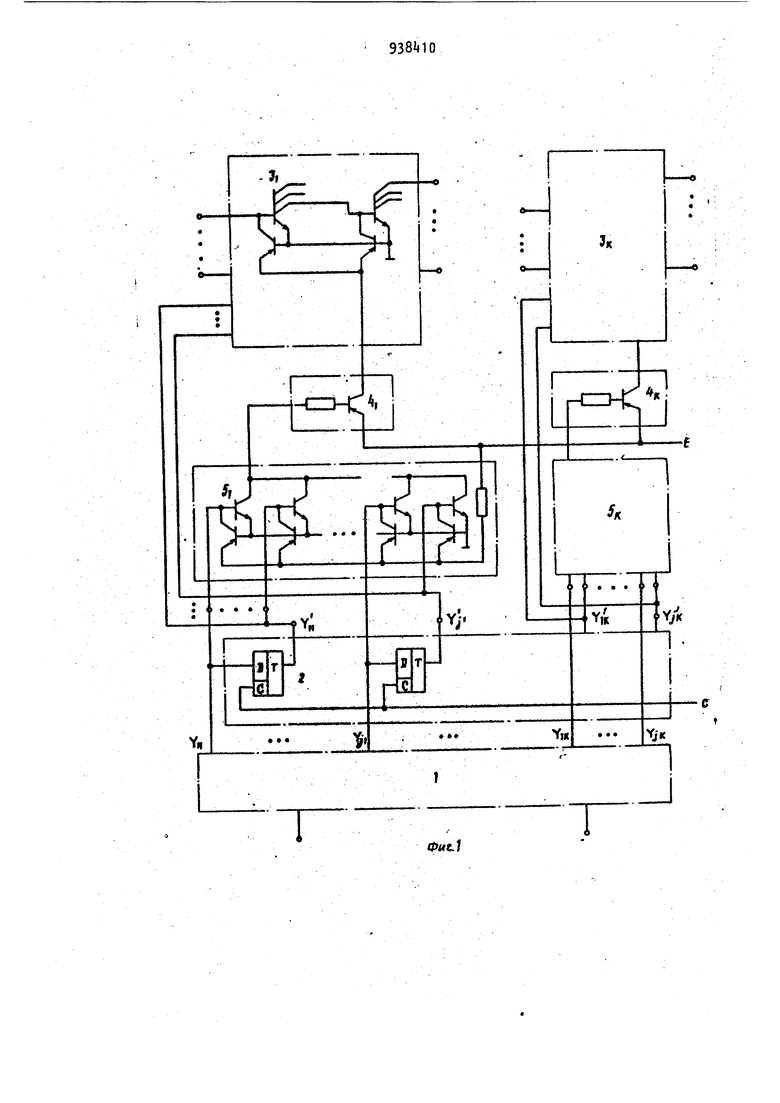

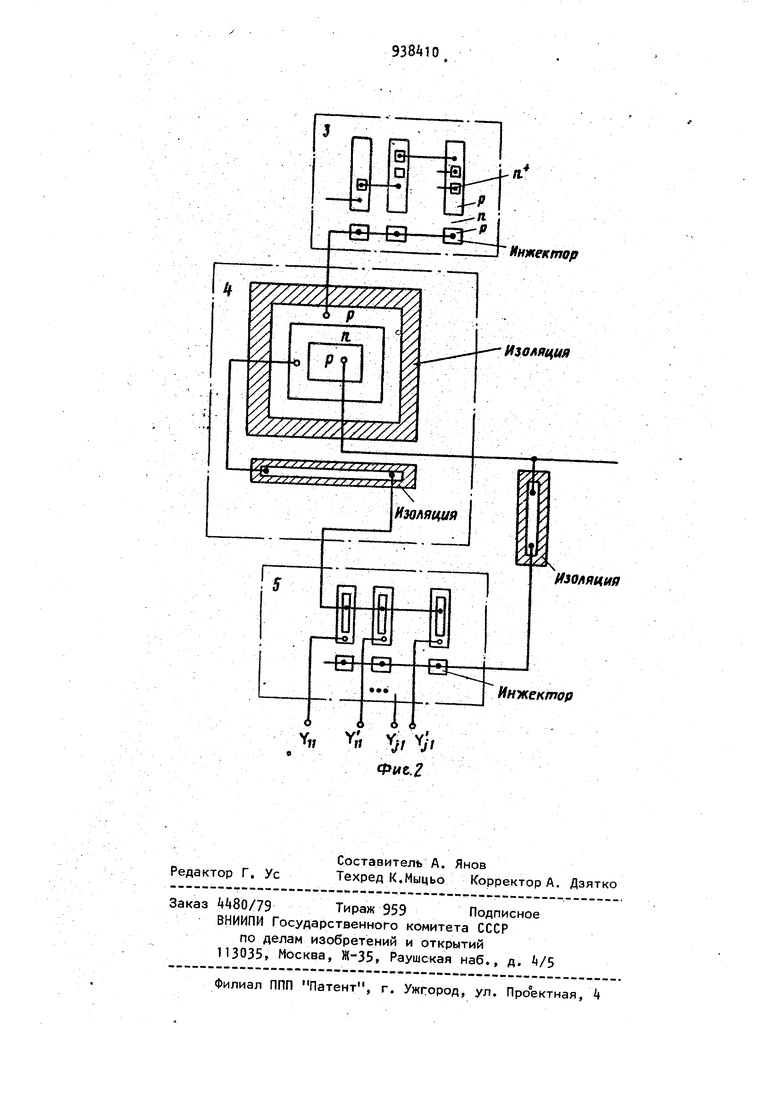

Поставленная цель достигается тем, что в устройство, содержащее К узлов оперативных блоков, узел управления, имеющий К групп управляющих выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами оперативных блоков, управляющие выходы каждой 1-й группы узла управления соединены с управляющими входами соответствующей i-й группы разрядов операционного регистра, управляющие выходы каждой i-й группы разрядов KOTOpoj-o соединены с управляющими .вводами соответствующего 1-го узла операционных блоков, введены К ключей коммутации тока питания и К элементов ИЛИ-НБ, причем входы каждого 1-го элемента ИЛИ-НЕ соединены с управляющими выходами 1-й группы узла управления и с выходами 1-й группы разрядов .операционного регистра, выходы каждого 1-го элемента ИЛИ-НЕ соединены с управляющими входом 1-го ключа коммутации тока питания, токовый выход каждого i-го ключа коммутации тока питания соединен с входом питания 1-го узла оперативных блоков, токовый вход всех К ключей коммутации тока питания соединен с входом питания устройства, при этом в качестве элементов ИЛИ-НЕ используются инверторы ИЛ, входы которых соединены с соответствующими входами 1-й группы узла управления и операционного регистра, выходы инверторов ,, подключенных к выходу элемента ИЛИ-НЕ, в качестве ключей коммутации тока питания используются р-п-р транзисторы, базы каждого из которых через резисторы соединена с управляющими входами соответствующе о ключа коммутации тока питания, коллектор и эмиттер каждого транзистора соединены соответственно с токовым выходом и токовым входом соответствующего ключа коммутации тока питания. На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - фрагмент топологии интегральной микросхемы микропроцессора. . Устройство содержит узел 1 управ ления, операционный регистр 2, К уз лов оперативных блоков 3 ключи k коммутации тока питания, элементы ИЛИ-НЕ 5 и шины питания. Управляющи выходы узла управления 1 разделены на К , причем сигналы каждой 1-й группы выходов управляют работой 1-го узла оперативных блоков 3. Каждая -я группа выходов узла 1 уп равления соединена с управляющими входами соответствующей I-и группы разрядов операционного регистра 2 и с входами i-го элемента ИЛИ-НЕ 5. Управляющие выходы каждой 1-й группы разрядов операционного регистоа соединены с. управляющими входами со ответствующего узла оперативных бло ков 3 и с входами f-ro элемента ИЛИ-НЕ 5. Выходы каждого 1-го элемента ИЛИ-НЕ 5 соединены с входом управления соответствующего ключа k коммутации тока питания. Токовые входы всех ключей 4 коммутации тока питания соединены с шиной питания, которая подключается к источнику наряжения. Токовый выход каждого i-ro ключа k коммутации тока питания соединен с входом питания |-гЬ узла оперативных блоков 3Разбиение структуры микропроцессора на узлы оперативных блоков 3 осуществляется по функциональным признакам: узел арифметико-логического блока/ значения, узлы коммутаторов и т.д. Каждый узел оперативных блоков 3 содержит от 10 до 300 элементов ИЛ, показанных на фиг. J. Путем соединения элементов Ил образуется оперативный блок 3, выполняющий требуемый набор логических функций. Узел 1 управления, также построенный на элементах И Л осуществляет выбор и дешифрацию команд, поступающих в микропроцессор, преобразуя их в комбинацию управляющих сигналов (управляющее слово.Каждая 1-я группа выходов узла 1 управления выдает сигналы , ,... для управления i-M оперативным блоком 3, которые записываются в 1-ю группу разрядов операционного регистра 2. Каждый разряд операционного регистра 2 представляет собой тактируемый D-триггер, построенный на элементах .,.-,-, .Ил. Сигналы , 2,- ,,.. выходов - поступают на управляющие входы 1-го узла оперативных блоков 3. Элемент ИЛИ-НЕ 5 образуется из инверторов , соединенные выходы которых реализуют операцию монтажное И. В результате на выходе элемента на входы инверторов И Л поступают сигналы ( , . ..)и( , Yii,...j, а на выходе образуется функция F(Yii Y.. v- (. ,...) YiY +Yi-i,..., т.е. реализуется операция ИЛИ-НЕ. Выход I-го элемента ИЛИ-НЕ 5 соединен с ,/правляющим входом i-ro ключа коммутации токов питания и состоящего из р-п-р-транзистора, база которого через резистор соединена с управляющим входом ключа. Коллектор каждого р-п-р-транзистора служит токовым выходом соответствующего 1-го ключа f коммутации токов питания и соединен с т ковым входом питания элементов ИТ1 1-го узла оперативных блоков 3. 5 Реализация элемента ИЛИ-НЕ 5f кл ча k коммутации тока питания и част элементов И узла оперативных блоков 3 показана на фиг.2. Инверторы И Л,образующие элемент ИЛИ-НЕ имеют такую же физическую структуру, как элементы И Л, используемые в уз лах 1-3. Транзисторы ключей k коммутации тока питания располагаются в изолированных областях полупровод ника, которые размещаются на периферии кристалла микросхемы. Так как К-число узлов оперативных блоков 3 относительно невелико (обычно на дв порядка меньше общего числа элементов в микропроцессоре, то возрастание площади кристалла из-за введе ния, дополнительных элементов и ключей не превышает нескольких процентов, j Микросхема И Л микропроцессора работает следующим образом. При поступлении команды на управляющие входы микропроцессора узел управления 1 вырабатывает упра ляющие сигналы (Y, , 2,...), (Y|i , Yjj... )... ( , Yi...) каждая группа которых управляет работой соответствующего i-ro узла оперативных блоков 3. Для узлов оперативных блоков 3, не участвующих в выполнении данной команды, все управляющие сигналы имеют значение логического О (низкий потенциал земли): (. Y-z... .)00... При поступлении тактового сигнала С значения всех управляющих сигналов записываются в со ответствующие разряды операционного регистра 2, и хранятся там в течение всего цикла обработки информации Управляющие сигналы Yji с выходов оп рационного регистра 2 поступают на управляющие входы узлов оперативных блоков 3 которые в соответствии с этими сигналами производят необходимые операции для выполнения данной команды. При этом на управляющие входы микропроцессора поступает новая (последующая) команда выполняемой программы, и на выходах узла управления 1 образуются новые значения управляющих сигналов Yj4 , определяющие выполнение этой команды.( Таким образом, сигналы YJIM на выходах операционного регистра и узла управления определяют, соответственно, выполнение текущей и послед ющей команды программы. Эти сигналы поступают на входы элементов ИЛИ-НЕ 5. Если дизъюнкция сигналов Y.y и , поступающих на входы 1-го элемента ИЛИ-НЕ не равна нулю, то это значит, что 1-й узел оперативных блоков 3 участвуетв выполнении текущей или последукнцей команды программы. В этом случае протекает базовый ток р-п-р-транзистора в 1-м ключе коммутации тока питания. Этот транзистор открывается и подает ток питания для элементов И Л J-ro уз/та ,.)ративных блоков 3. Если же (Y,4 О, то все выходные транзисторы инверторов Й в -м элементе ИЛИ-НЕ 5 закрыты, р-п-р-транзистор 1-го ключа k коммутации тока питания также закрыт, и в 1-й узел оперативных бло-. кое 3 не поступает ток питания. Таким образом, узлы оперативных блоков 3, .не участвующие в выполнении текущей и последующей команды, отключаются от источника питания и не потребляют мощность. Переключение элементов ИЛИ-НЕ 5 и ключей коммутации тока питания в состояние, необходимое для выполне- . НИИ последующей команды производится в течение цикла выполнения текущей команды. Таким образом, в микросхеме реализуется предварительное включение тока питания узлов оперативных блоков 3- благодаря чему быстродействие микропроцессора сохраняется на прежнем уровне. Применение микросхем Микропроцессоров, с отключением узлов оперативных блоков в сложных цифровых системах позволяет значительно уменьшить общую потребляемую мощность систем. Формула изобретения /. Интегральная микросхема И Л микропроцессора, содержащая К узлов оперативных блоков, узел управления, имеющий К групп управляющих выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами оперативных блоков, управляющие выходы каждой I-и группы узла управления соединены с управляющими входами соответствуюцей 1-й группы разрядов операционного регистра, управляющие выходы каждой (-группы разрядов ко79

торого соединены с управляющими входами соответствующего I-го узла операционных блоков, отличающаяся тем, что, с целью уменьшений потребляемой мощности в нее введены К ключей коммутации тока питания и К элементов ИЛИ-НЕ, причем входы каждого i-ro элемента ИЛИ-НЕ соединены с управляющими выходами 1-й группы узла управления и с выходами i-й группы разрядов операционного регистра, выходы каждого 1-го элемента ИЛИ-НЕ соединены с управляющим входом 1-го ключа коммутации тока питания, токовый выход каждого 1-го ключа коммутации тока-питания соединен с входом питания 1-го узла оперативных блоков, токовый вход всех К ключей коммутации тока питания соединен с входом питания устройства,

2, Микросхема поп.1,отлимающ а я с я тем, что в качестве элементов ИЛИ-НЕ используются инверторы И.-Л, входы которых соединены с соответствующими выходами 1-й груп

8

пы узла управления и операционного регистра, выходы инверторов подключены к выходу элемента ИЛИ-НЕ, в качестве ключей коммутаций тока питания используется р-п-р-транзисторы, база каждого из которых через резисторы соединена с управляющими .. входами соответствующего ключа коммутации тока питания, коллектор и эмит тер каждого транзистора соединены соответственно с токовым выходом и токовым входом соответствующего ключа коммутации тока питания.

Источники информации, принятые во внимание при экспертизе

с. 36, рис. 2.

Авторы

Даты

1982-06-23—Публикация

1980-11-17—Подача