(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство определения координат объекта | 1988 |

|

SU1562980A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Адаптивная система телеметрического контроля | 1990 |

|

SU1751800A2 |

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

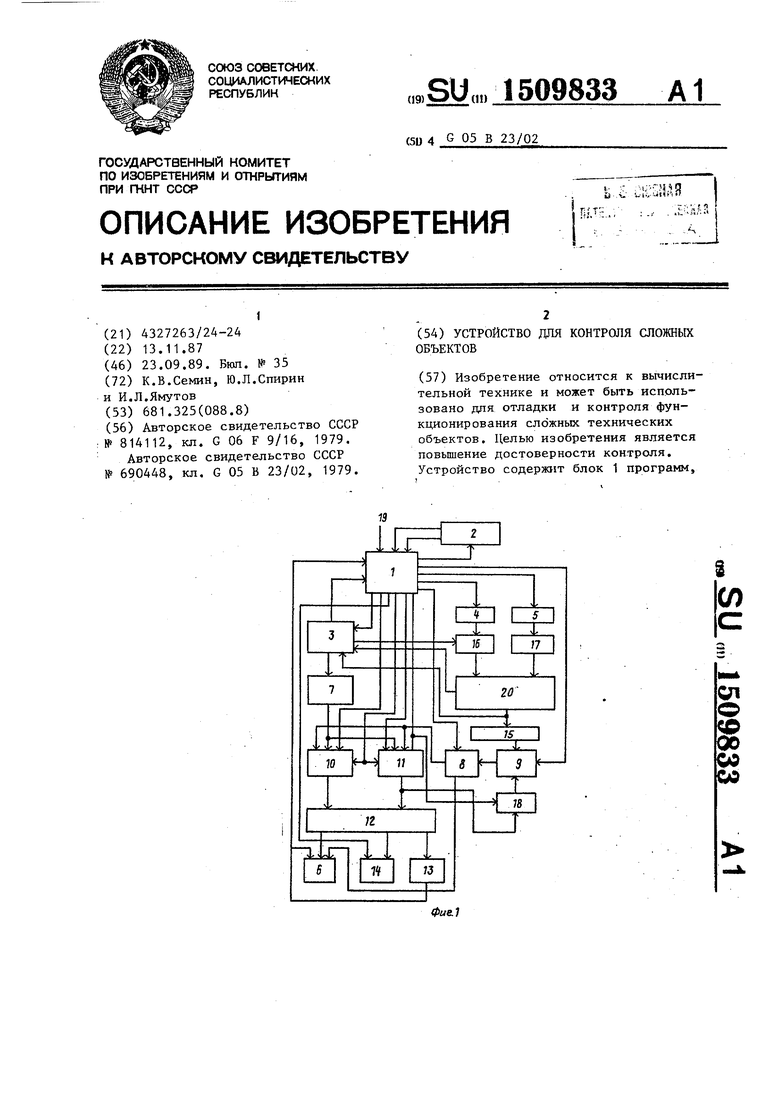

Изобретение относится к вычислительной технике и может быть использовано для отладки и контроля функционирования сложных технических объектов. Целью изобретения является повышение достоверности контроля. Устройство содержит блок 1 программ, формирователь 2 временной диаграммы, блок 3 синхронизации, первый 4 и второй 5 регистры, блок 6 индикации, счетчик 7, блок 8 нормализации, блок 9 коммутации, блок 10 оперативной памяти, блок 11 репрограммируемой памяти, вычитатель 12, блок 13 постоянной памяти, блок 14 регистрации, датчик 15, преобразователь пробного воздействия 16, преобразователь коррекции 17, формирователь 18 сигналов. Поставленная цель достигается путем сравнения откликов объекта контроля от воздействия одиночных импульсов с записанными ранее, в процессе функционирования предлагаемого устройства, эталонными откликами с возможностью самотестирования устройства благодаря моделированию откликов объекта контроля на одиночные импульсы. Достоверность контроля повышается также путем введения корректирующего одиночного импульса, позволяющего исключить паразитные составляющие за счет параметрических процессов при подаче пробного воздействия непосредственно в рабочем режиме объекта контроля. Для достижения поставленной цели используются известные и вновь введенные блоки и связи. 8 ил.

ел

о со сх со со

3150

формирователь 2 временной диаграммы, блок 3 синхронизации, первый 4 и второй 5 регистры, блок 6 индикации, счетчик 7, блок 8 нормализации,блок 9 коммутации, блок 10 оперативной памяти, блок 11 репрограммируемой памяти, вычитатель 12,блок 13 постоянной памяти, блок 14 регистрации, датчик 15, преобразователь пробного воздействия 16, преобразователь коррекции 17, формирователь 1.8 сигналов. Поставленная цель достигается путем сравнения откликов объекта контроля от воздействия одиноч- ных импульсов с записанным ранее,в процессе функционирования предлагаИзобретение относится к вычислительной технике и может быть использовано ;ц1я отладки и контроля функционирования сложных технических объектов, например, систем управления реального времени, в том числе цифроаналоговых систем вторичного электропитания радиоэлектронной аппаратуры на пьезоэлектрических и на маточных электромагнитных трансфор- маторах с адаптивными изменениями параметров во времени.

Цель изобретения - повышение достоверности контроля.

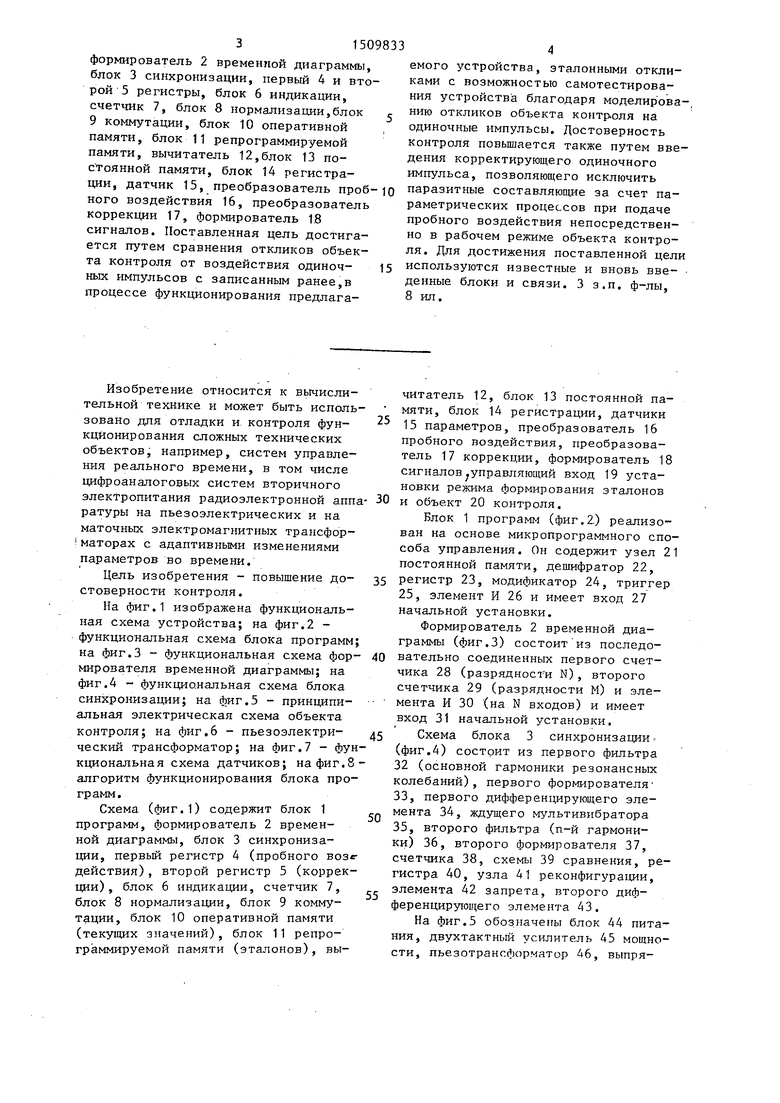

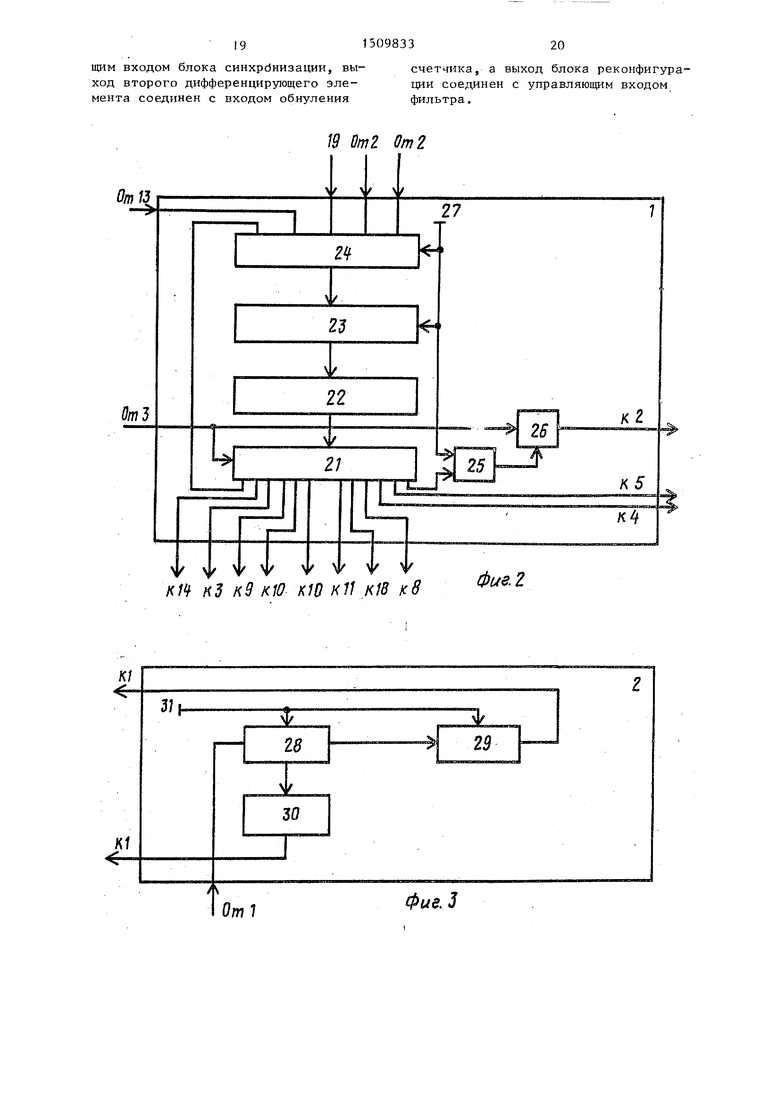

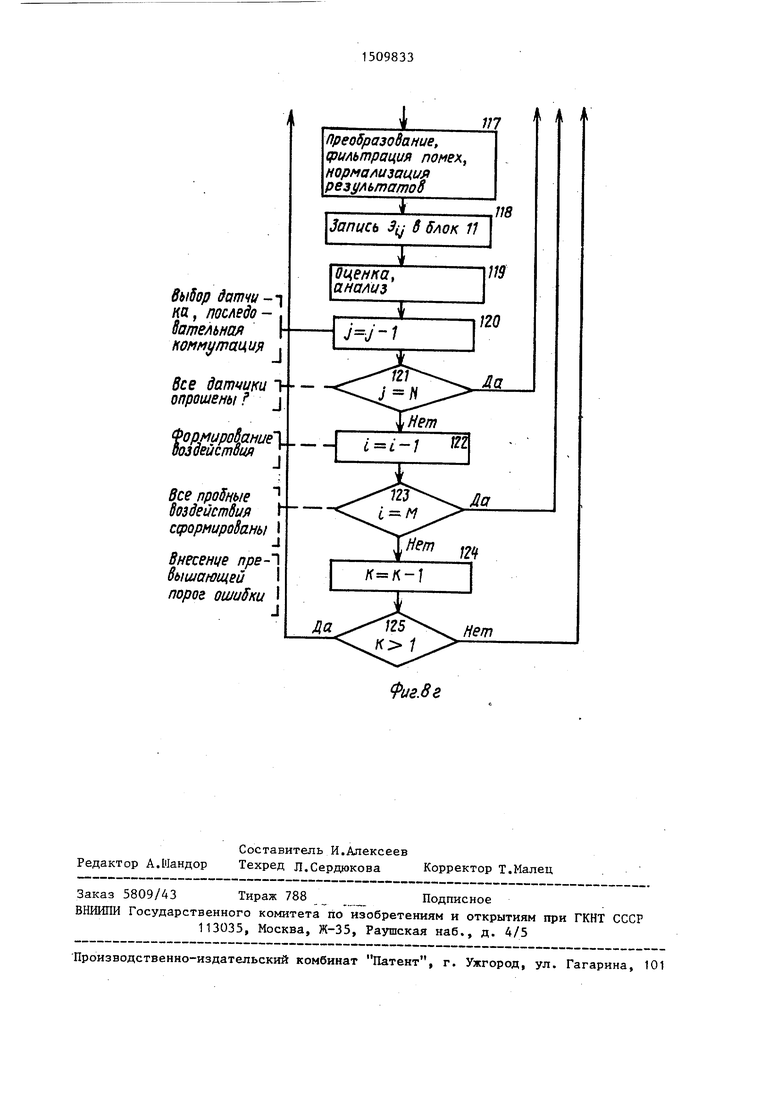

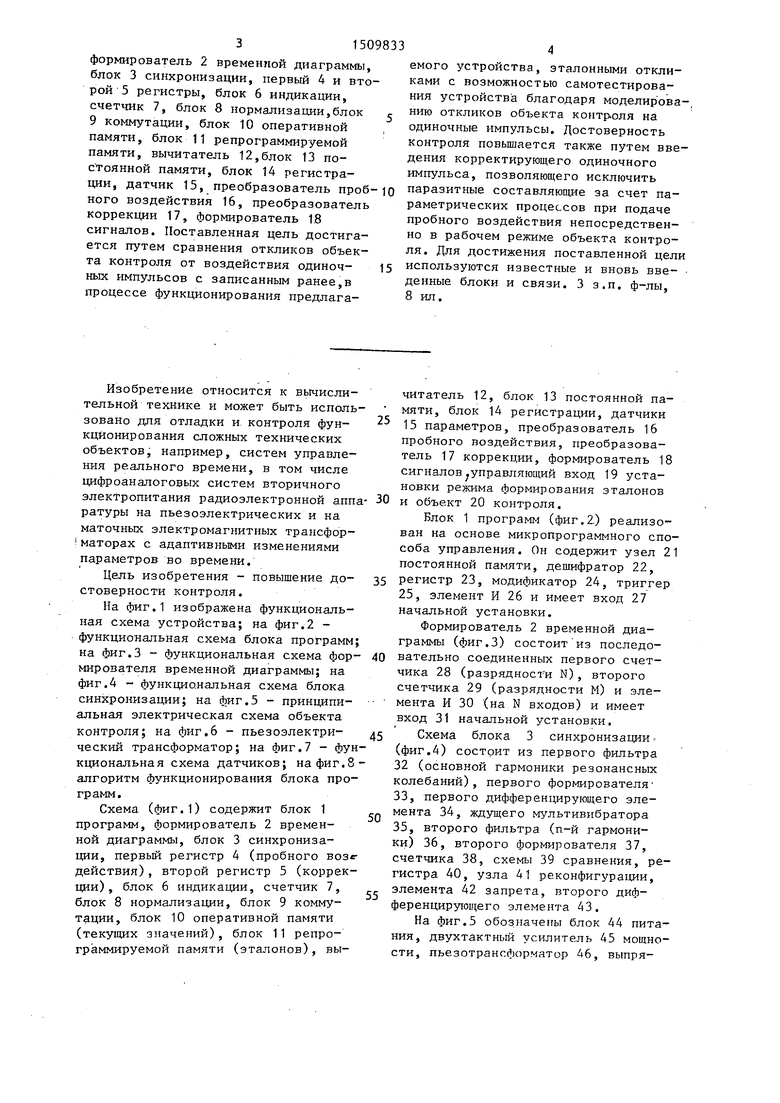

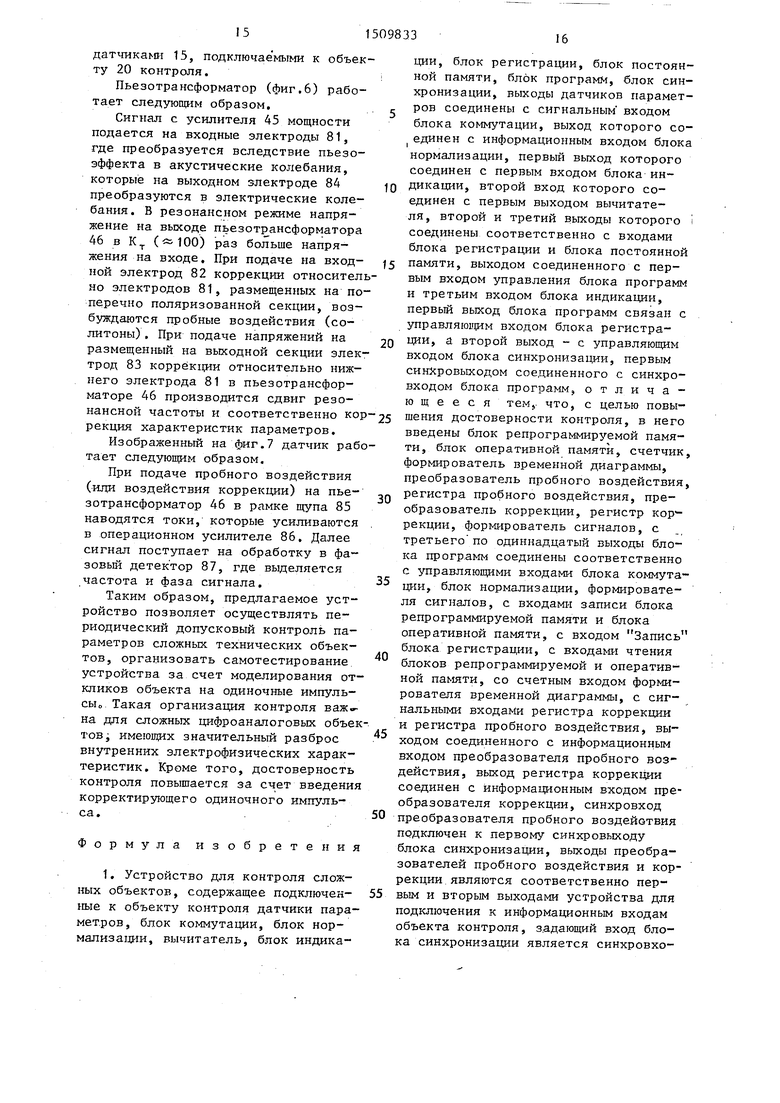

На фиг.1 изображена функциональная схема устройства; на фиг.2 - функциональная схема блока программ; на фиг.З - функциональная схема формирователя временной диаграммы; на фиг.4 - функциональная схема блока синхронизации; на фиг.5 - принципиальная электрическая схема объекта контроля; на фиг.6 - пьезоэлектрический трансформатор; на фиг.7 - функциональная схема датчиков; на фиг.З алгоритм функционирования блока прогр амм.

Схема (фиг.1) содержит блок 1 программ, формирователь 2 временной диаграммы, блок 3 синхронизации, первый регистр 4 (пробного возе действия), второй регистр 5 (коррекции) , блок 6 индикации, счетчик 7, блок 8 нормализации, блок 9 коммутации, блок 10 оперативной памяти (текущих значений), блок 11 репрограммируемой памяти (эталонов), выемого устройства, эталонными откликами с возможностью самотестирования устройства благодаря моделир ованию откликов объекта контр-оля на одиночные импульсы. Достоверность контроля повьшается также путем введения корректирующего одиночного импульса, позволяющего исключить паразитные составляющие за счет параметрических процессов при подаче пробного воздействия непосредственно в рабочем режиме объекта контроля. Для достижения поставленной цели используются известные и вновь вве- денные блоки и связи. 3 з.п, ф-лы, 8 ил.

читатель 12, блок 13 постоянной памяти, блок 14 регистрации, датчики

15 параметров, преобразователь 16 пробного воздействия, преобразователь 17 коррекции, формирователь 18 сигналов .управляющий вход 19 установки режима формирования эталонов

и объект 20 контроля.

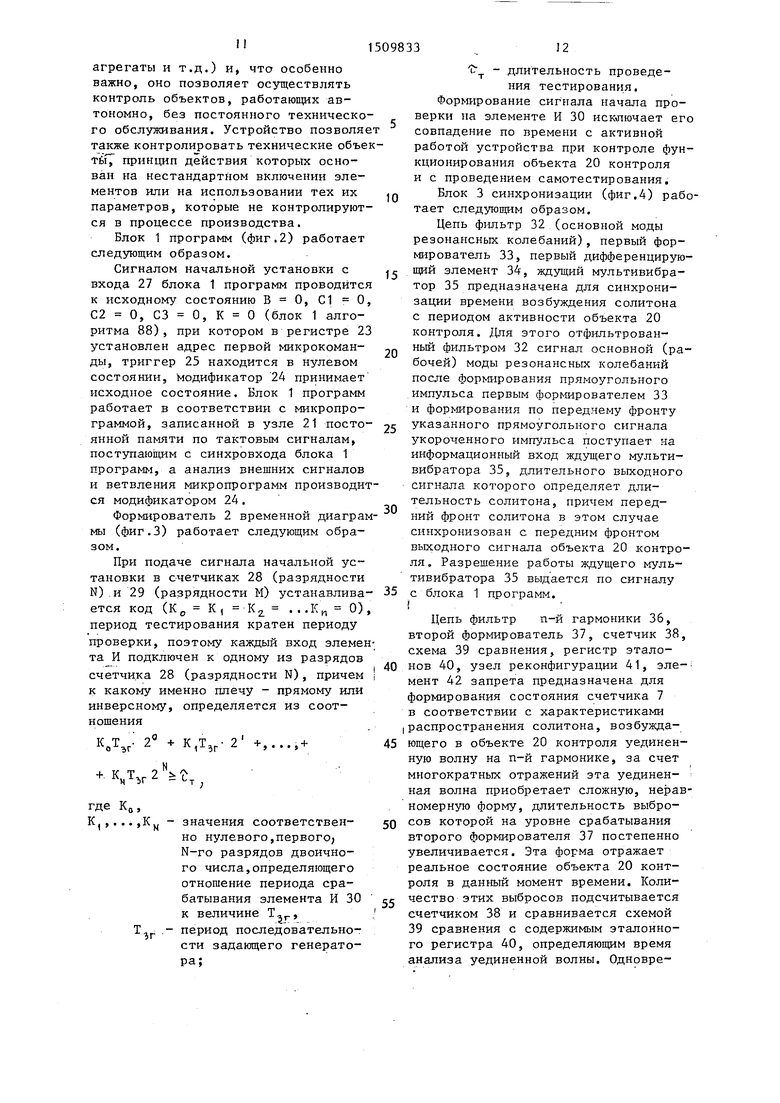

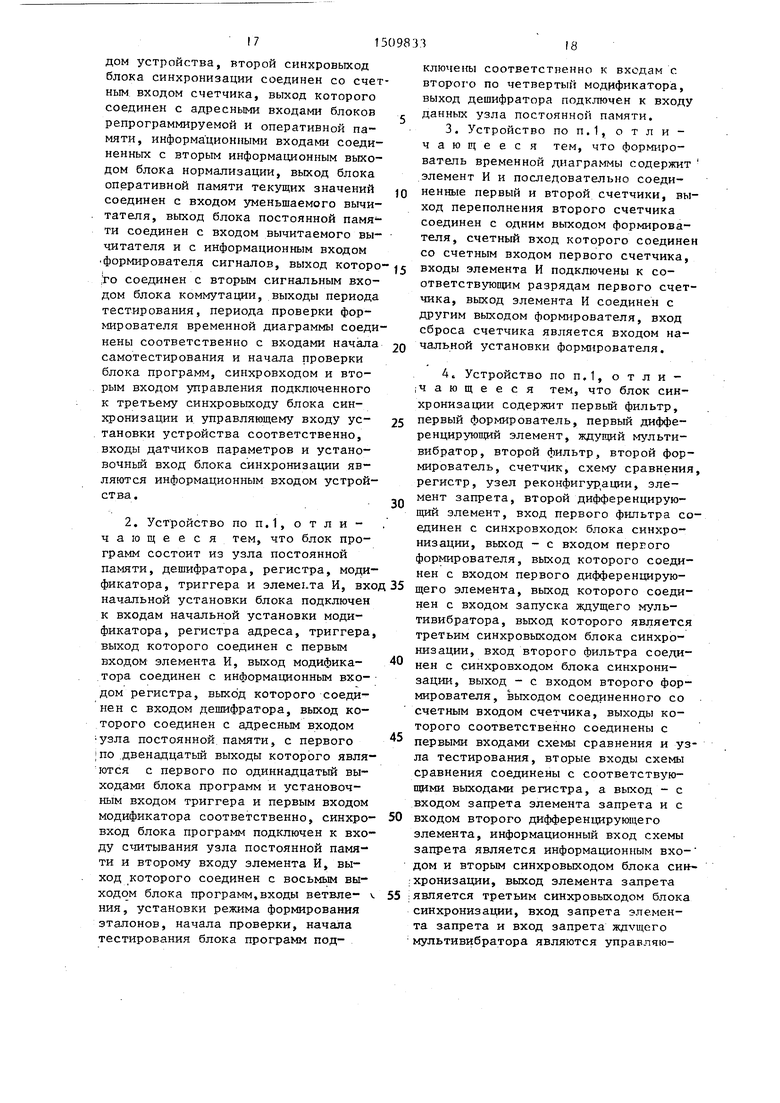

Блок 1 программ (фиг.2.) реализован на основе микропрограммного способа управления. Он содержит узел 21 постоянной памяти, дешифратор 22,

регистр 23, модификатор 24, триггер 25, элемент И 26 и имеет вход 27 начальной установки.

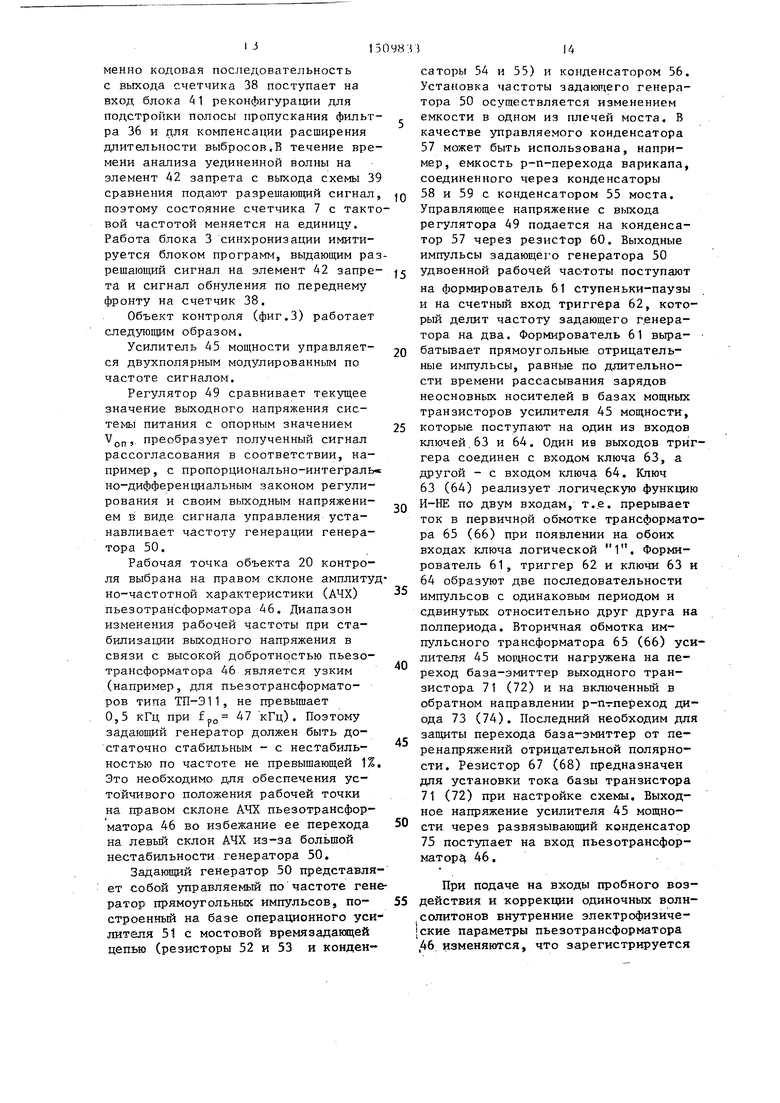

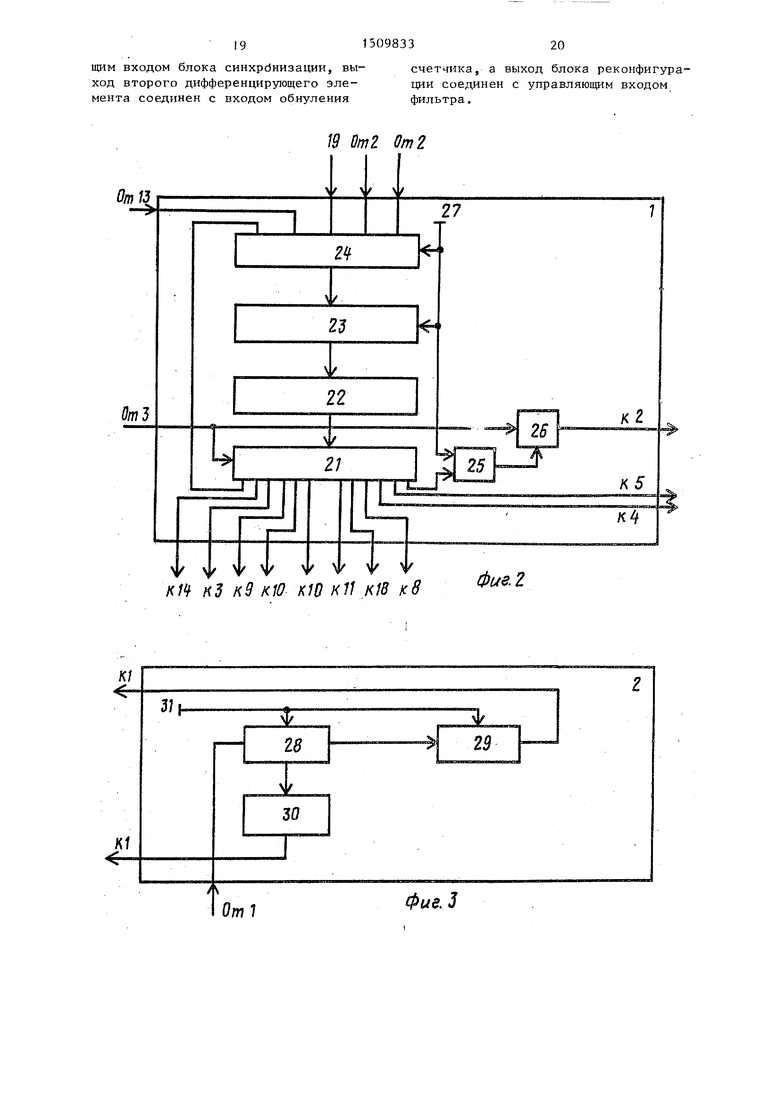

Формирователь 2 временной диаграммы (фиг.З) состоит из последовательно соединенных первого счетчика 28 (разрядности N), второго счетчика 29 (разрядности М) и элемента И 30 (на N входов) и имеет вход 31 начальной установки,

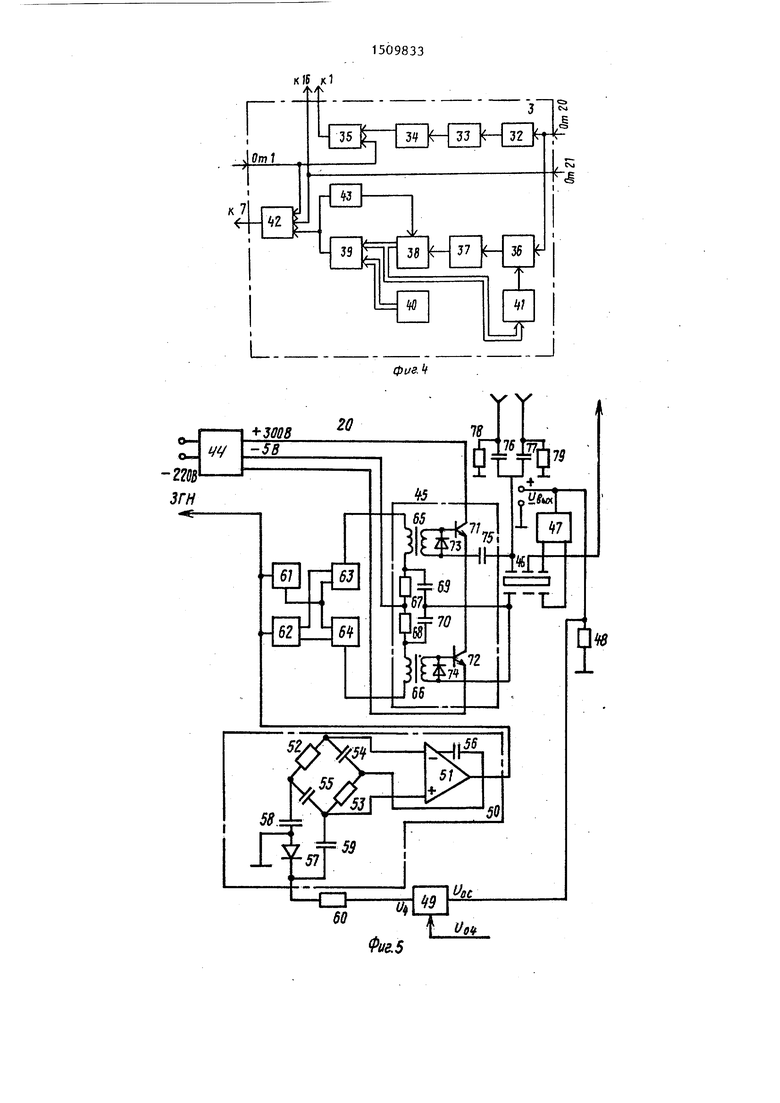

Схема блока 3 синхронизации, (фиг,4) состоит из первого фильтра 32 (основной гармоники резонансных колебаний), первого формирователя- 33, первого дифференцирующего элемента 34, ждущего мультивибратора 35, второго фильтра (п-й гармоники) 36, второго формирователя 37, счетчика 38, схемы 39 сравнения, регистра 40, узла 41 реконфигурации, элемента 42 запрета, второго дифференцирующего элемента 43.

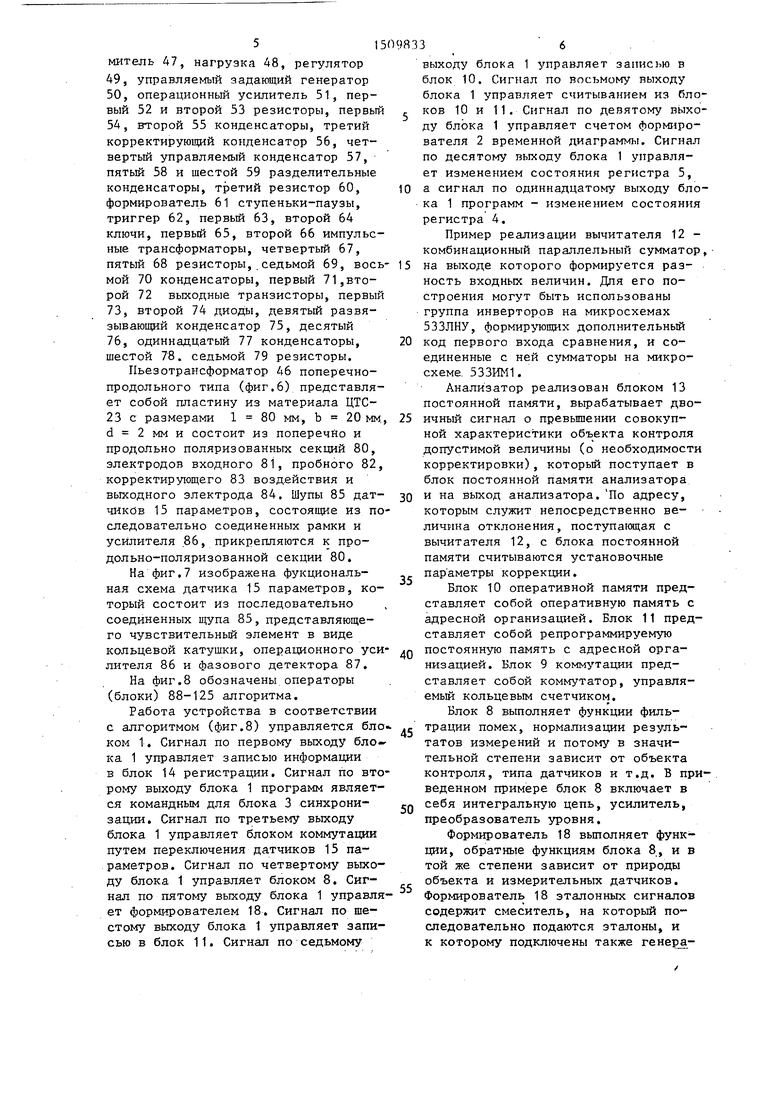

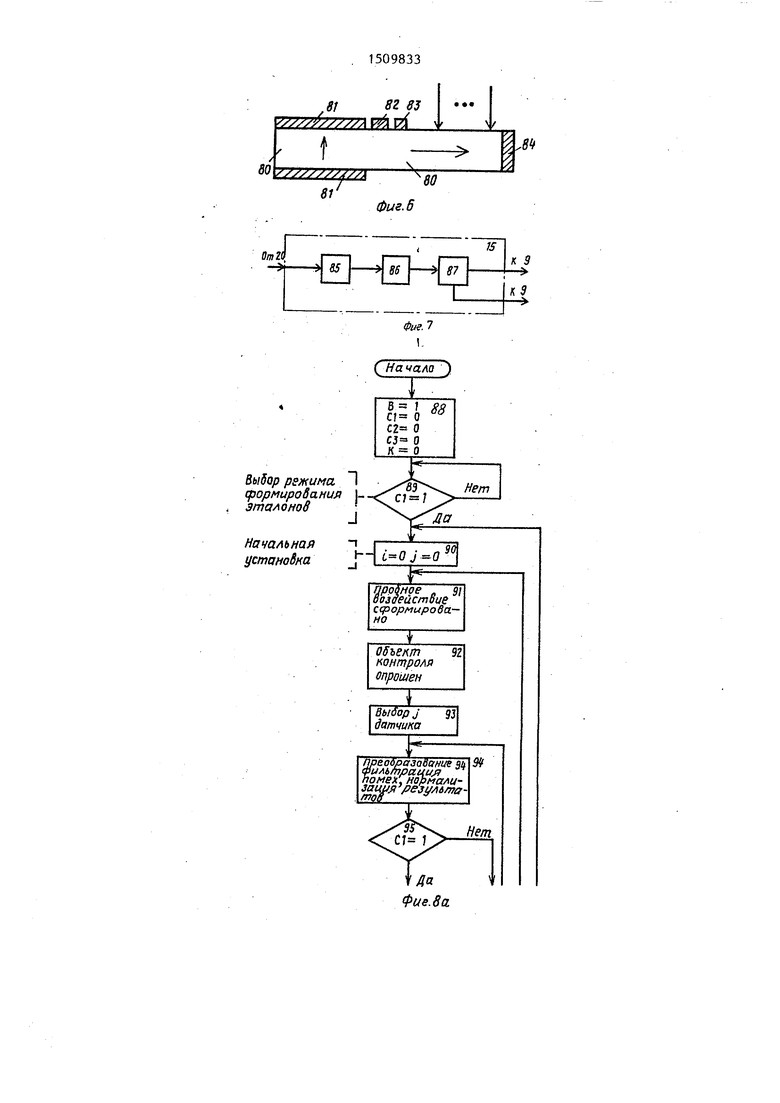

На фиг.З обозначе гы блок 44 питания, двухтактный усилитель 45 мощности, пьезотрансформатор 46, выпря

митепь 47, нагрузка 48, регулятор

49,управляемый задающий генератор

50,операционный усилитель 51, первый 52 и второй 53 резисторы, первый 54, второй 55 конденсаторы, третий корректирующий конденсатор 56, четвертый управляемый конденсатор 57, пятый 58 и шестой 59 разделительные конденсаторы, третий резистор 60, формирователь 61 ступеньки-паузы, триггер 62, первый 63, второй 64 ключи, первый 65, второй 66 импульсные трансформаторы, четвертый 67, пятый 68 резисторы,.седьмой 69, восьмой 70 конденсаторы, первый 71,второй 72 выходные транзисторы, первый 73, второй 74 диоды, девятый развязывающий конденсатор 75, десятый

76, одиннадцать 77 конденсаторы, шестой 78. седьмой 79 резисторы,

Пьезотрансформатор 46 поперечно- продольного типа (фиг,6) представляет собой пластину из материала ЦТС- 23 с размерами 1 80 мм, b 20 мм. d 2 мм и состоит из поперечно и продольно поляризованных секций 80, электродов входно.го 81, пробного 82, корректирующего 83 воздействия и выходного электрода 84, Шупы 85 датчиков 15 параметров, состоящие из последовательно соединенных рамки и усилителя 86, прикрепляются к продольно-поляризованной секции 80.

На фиг,7 изображена фукциональ- ная схема датчика 15 параметров, который состоит из последовательно соединенных щупа 85, представляющего чувствительный элемент в виде кольцевой катушки, операционного усилителя 86 и фазового детектора 87,

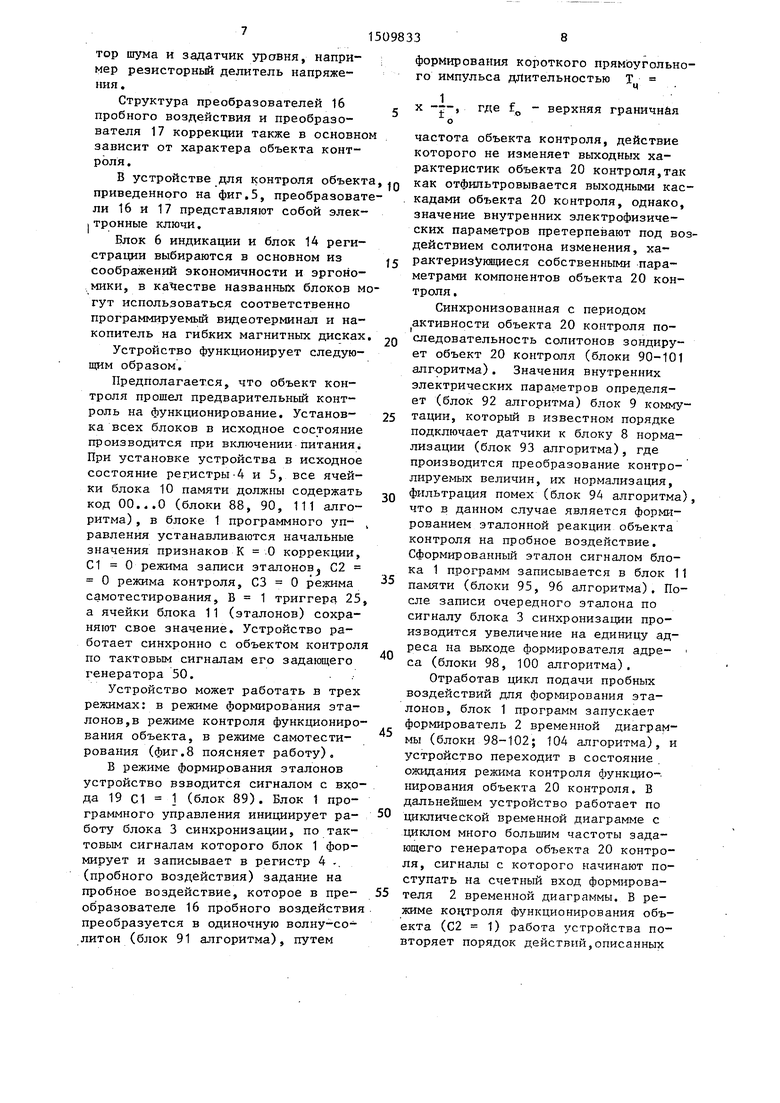

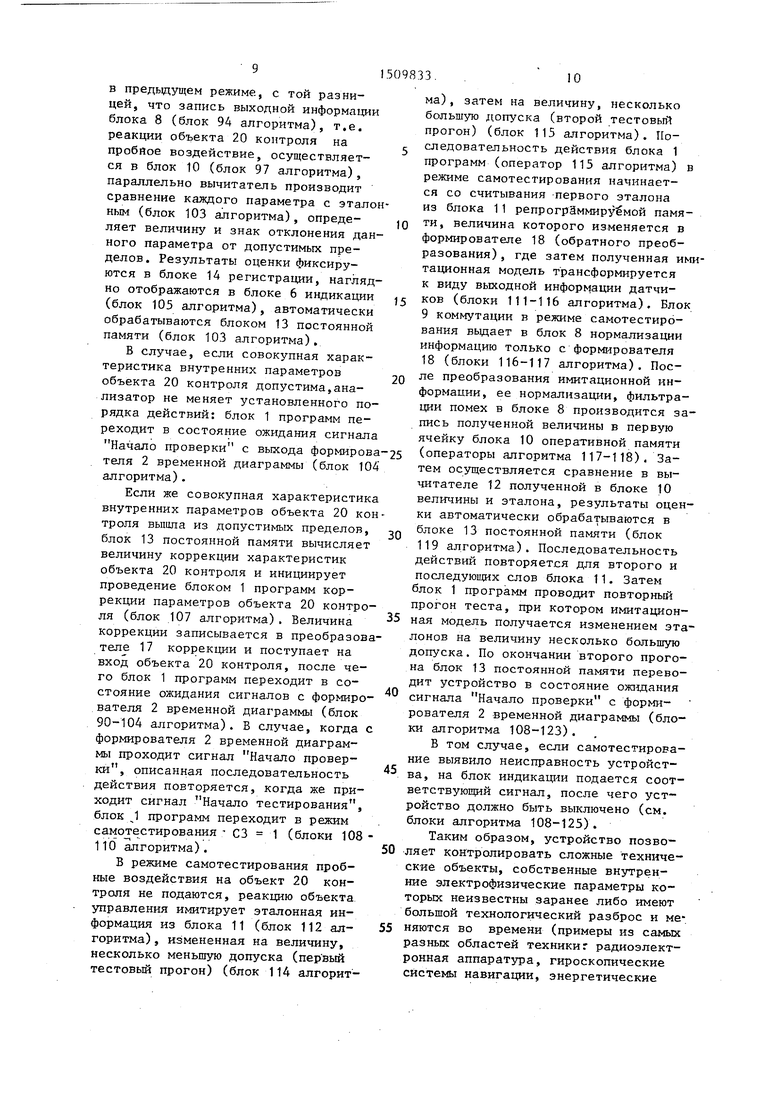

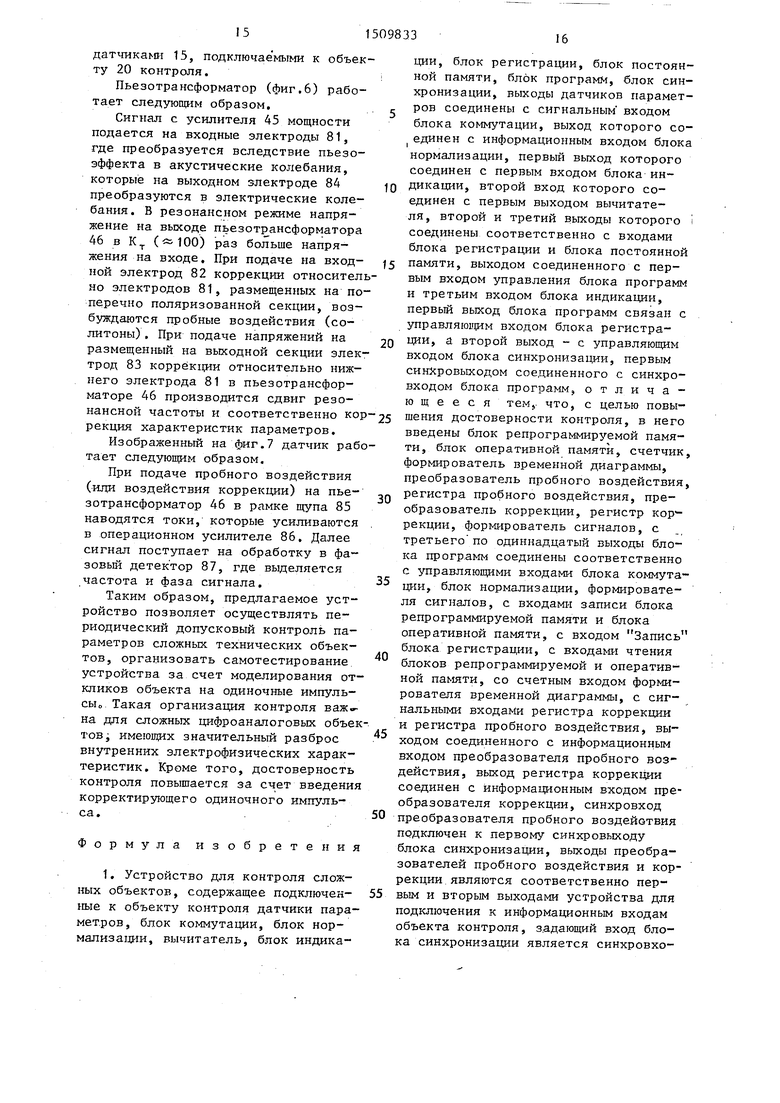

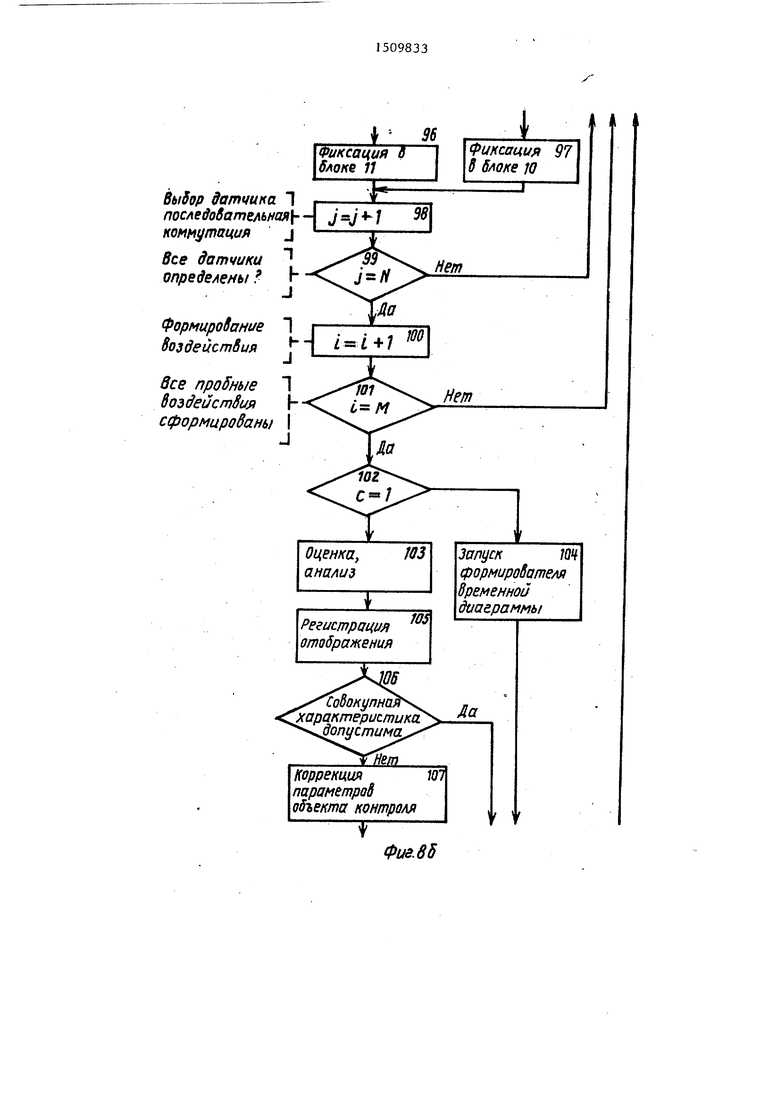

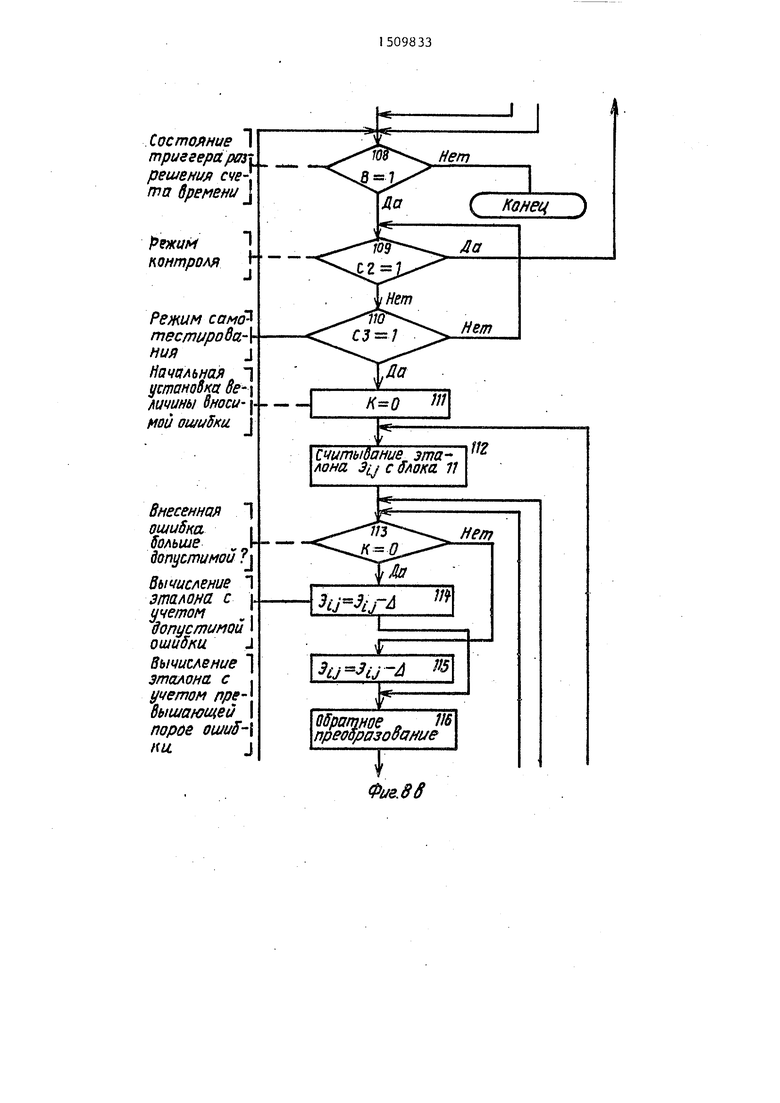

На фиг,8 обозначены операторы (блоки) 88-125 алгоритма.

Работа устройства в соответствии с алгоритмом (фиг,8) управляется бло ком 1. Сигнал по первому выходу блока 1 управляет записью информации в блок 14 регистрации. Сигнал по второму выходу блока 1 программ является командным для блока 3 синхронизации. Сигнал по третьему выходу блока 1 управляет блоком коммутации путем переключения датчиков 15 параметров. Сигнал по четвертому выходу блока 1 управляет блоком 8, Сигнал по пятому выходу блока 1 управляет формирователем 18, Сигнал по шестому выходу блока 1 управляет записью в блок 11, Сигнал по седьмому

0

5

0

5

0

5

0

5

выходу блока 1 управляет записью в блок 10. Сигнал по восьмому выходу блока 1 управляет считыванием из блоков 10 и 11. Сигнал по девятому выходу блока 1 управляет счетом формирователя 2 временной диаграммы. Сигнал по десятому выходу блока 1 управляет изменением состояния регистра 5, а сигнал по одиннадцатому выходу блока 1 программ - изменением состояния регистра 4,

Пример реализаид и вычитателя 12 - комбинационный параллельный сумматор, на выходе которого формируется разность входных величин, Дпя его построения могут быть использованы группа инверторов на микросхемах 533ЛНУ, формирующих дополнительный код первого входа сравнения, и соединенные с ней сумматоры на микросхеме. 533ИМ1,

Анализатор реализован блоком 13 постоянной памяти, вьфабатывает двоичный сигнал о превышении совокупной характеристики объекта контроля допустимой величины (о необходимости корректировки), который поступает в блок постоянной памяти анализатора и на выход анализатора, По адресу, которым служит непосредственно ве- личина отклонения, поступающая с вычитателя 12, с блока постоянной памяти считываются установочные параметры коррекции.

Блок 10 оперативной памяти представляет собой оперативную память с адресной организацией. Блок 11 представляет собой репрограммируемую постоянную память с адресной организацией. Блок 9 коммутации представляет собой коммутатор, управляемый кольцевым счетчиком.

Блок 8 выполняет функции фильтрации помех, нормализации результатов измерений и потому в значительной степени зависит от объекта контроля, типа датчиков и т,д, В приведенном примере блок 8 включает в себя интегральную цепь, усилитель, преобразователь уровня.

Формирователь 18 выполняет функции, обратньш функциям блока 8, и в той же степени зависит от природы объекта и измерительных датчиков. Формирователь 18 эталонных сигналов содержит смеситель, на который последовательно подаются эталоны, и к которому подключены также генер тор шума и задатчик уровня, например реэисторньй делитель напряжения .

Структура преобразователей 16 пробного воздействия и преобразователя 17 коррекции также в основно зависит от характера объекта контроля .

В устройстве для контроля объект приведенного на фиг.5, преобразоват ли 16 и 17 представляют собой элек- 1 тронные ключи.

Блок 6 индикации и блок 14 регистрации выбираются в основном из соображений экономичности и эргономики, в качестве названных блоков м гут использоваться соответственно программируемый видеотерминал и накопитель на гибких магнитных дисках

Устройство функционирует следующим образом.

Предполагается, что объект контроля прошел предварительный контроль на функционирование. Установка всех блоков в исходное состояние производится при включении питания. При установке устройства в исходное состояние регистры-4 и 5, все ячейки блока 10 памяти должны содержать код 00...О (блоки 88, 90, 111 алгоритма) , в блоке 1 программного уп- равления устанавливаются начальные значения признаков К 0 коррекции, С1 0 режима записи эталонов С2 О режима контроля, СЗ О режима самотестирования, В 1 триггера 25 а ячейки блока 11 (эталонов) сохраняют свое значение. Устройство работает синхронно с объектом контрол по тактовым сигналам его задающего генератора 50..

Устройство может работать в трех режимах: в режиме формирования эталонов, в режиме контроля функционирования объекта, в режиме самотестирования (фиг.8 поясняет работу),

В режиме формирования эталонов устройство взводится сигналом с входа 19 С1 1 (блок 89). Блок 1 программного управления инициирует работу блока 3 синхронизации, по тактовым сигналам которого блок 1 формирует и записывает в регистр 4 -, (пробного воздействия) задание на пробное воздействие, которое в преобразователе 16 пробного воздействи преобразуется в одиночную волну-со- литон (блок 91 алгоритма), путем

формирования короткого прямоугольного импульса длительностью Т

г X -Г-, где f - верхняя граничная о

частота объекта контроля, действие которого не изменяет выходных характеристик объекта 20 контроля,так IQ как отфильтровывается выходными кас- . кадами объекта 20 контроля, однако, значение внутренних электрофизических параметров претерпевают под воздействием солитона изменения, хаJ5 рактеризукяциеся собственными параметрами компонентов объекта 20 контроля .

Синхронизованная с периодом активности объекта 20 контроля по20 следовательность солитонов зондирует объект 20 контроля (блоки 90-101 алгоритма). Значения внутренних электрических параметров определяет (блок 92 алгоритма) блок 9 комму25 тации, который в известном порядке подключает датчики к блоку 8 нормализации (блок 93 алгоритма), где производится преобразование контролируемых величин, их нормализация,

2Q фильтрация помех (блок 94 алгоритма), что в данном случае является формированием эталонной реакции объекта контроля на пробное воздействие. Сформированный эталон сигналом блока 1 программ записывается в блок 11 памяти (блоки 95, 96 алгоритма). После записи очередного эталона по сигналу блока 3 синхронизации производится увеличение на единицу адреса на выходе формирователя адре- са (блоки 98, 100 алгоритма).

Отработав цикл подачи пробных воздействий для формирования эталонов, блок 1 программ запускает формирователь 2 временной диаграммы (блоки 98-102; 104 алгоритма), и устройство переходит в состояние . ожидания режима контроля функцио-. нирования объекта 20 контроля. В дальнейшем устройство работает по

50 циклической временной диаграмме с циклом много большим частоты задающего генератора объекта 20 контроля, сигналы с которого начинают поступать на счетный вход формирова5 теля 2 временной диаграммы. В режиме контроля функционирования объекта (С2 1) работа устройства повторяет порядок действий,описанных

35

40

45

в предьщущем режиме, с той разницей, что запись выходной информатдии блока 8 (блок 94 алгоритма), т.е. реакции объекта 20 контроля на пробное воздействие, осуществляется в блок 10 (блок 97 алгоритма), параллельно вычитатель производит сравнение каждого параметра с эталонным (блок 103 алгоритма), определяет величину и знак отклонения данного параметра от допустимых пределов . Результаты оценки фиксируются в блоке 14 регистрации, наглядно отображаются в блоке 6 индикации (блок 105 алгоритма), автоматически обрабатываются блоком 13 постоянной памяти (блок 103 алгоритма).

В случае, если совокупная характеристика внутренних параметров объекта 20 контроля допустима,анализатор не меняет установленного порядка действий: блок 1 программ переходит в состояние ожидания сигнала Начало проверки с выхода формирователя 2 временной диаграммы (блок 104 алгоритма).

Если же совокупная характеристика внутренних параметров объекта 20 контроля вышла из допустимых пределов, блок 13 постоянной памяти вычисляет величину коррекции характеристик объекта 20 контроля и инициирует проведение блоком 1 программ коррекции параметров объекта 20 контроля (блок 107 алгоритма). Величина коррекции записывается в преобразователе 17 коррекции и поступает на вход объекта 20 контроля, после чего блок 1 программ переходит в состояние ожидания сигналов с формирователя 2 временной диаграммы (блок 90-104 алгоритма). В случае, когда с формирователя 2 временной диаграммы проходит сигнал Начало проверки, описанная последовательность действия повторяется, когда же приходит сигнал Начало тестирования, блок J программ переходит в режим самотестирования- СЗ 1 (блоки 108 11() алгоритма).

В режиме самотестирования пробные воздействия на объект 20 контроля не подаются, реакцию объекта управления имитирует эталонная информация из блока 11 (блок 112 алгоритма) , измененная на величину, несколько меньшую допуска (первый тестовый прогон) (блок 114 алгоритма), затем на величину, несколько большую допуска (второй тестовый прогон) (блок 115 алгоритма). По- следовательность действия блока 1 программ (оператор 115 алгоритма) в режиме самотестирования начинается со считывания первого эталона из блока 11 репрогр§ммируемой памяти, величина которого изменяется в формирователе 18 (обратного преобразования) , где затем полученная имитационная модель трансформируется к виду выходной информации датчиков (блоки 111-116 алгоритма). Блок 9 коммутации в режиме самотестирования вьщает в блок 8 нормализации информацию только с формирователя 18 (блоки 116-117 алгоритма). После преобразования имитационной информации, ее нормализации, фильтрации помех в блоке 8 производится запись полученной величины в первую ячейку блока 10 оперативной памяти

(операторы алгоритма 117-118). Затем осуществляется сравнение в вы- читателе 12 полученной в блоке 10 величины и эталона, результаты оценки автоматически обрабатываются в блоке 13 постоянной памяти (блок 119 алгоритма). Последовательность действий повторяется для второго и последующих слов блока 11. Затем блок 1 программ проводит повторный прогон теста, при котором имитационная модель получается изменением эталонов на величину несколько большую допуска. По окончании второго прогона блок 13 постоянной памяти переводит устройство в состояние ож1Здания

сигнала Начало проверки с формирователя 2 временной диаграммы (блоки алгоритма 108-123).

В том случае, если самотестирование выявило неисправность устройства, на блок индикации подается соответствующий сигнал, после чего устройство должно быть выключено (см. блоки алгоритма 108-125).

Таким образом, устройство позволяет контролировать сложные технические объекты, собственные внутренние электрофизические параметры которых неизвестны заранее либо имеют большой технологический разброс и меняются во времени (примеры из самых разных областей техники г радиоэлектронная аппаратура, гироскопические системы навигации, энергетические

агрегаты и т.д.) и, что особенно важно, оно позволяет осзпцествлять контроль объектов, работающих автономно, без постоянного технического обслузкивания. Устройство позволя также контролировать технические объе Tbi7 принцип действия которых основан на нестандартном включении элементов или на использовании тех их параметров, которые не контролируются в процессе производства.

Блок 1 программ (фиг.2) работает следующим образом.

Сигналом начальной установки с входа 27 блока 1 программ проводитс к исходному состоянию , С1 0 С2 О, СЗ О, К О (блок 1 алгоритма 88), при котором в регистре 2 установлен адрес первой микрокоманды, триггер 25 находится в нулевом состоянии, модификатор 2А принимает исходное состояние. Блок 1 программ работает в соответствии с микропрограммой, записанной в узле 21 постоянной памяти по тактовым сигналам, поступающим с синхровхода блока 1

программ, а анализ внешних сигналов и ветвления микропрограмм производится модификатором 24.

Формирователь 2 временной диаграммы (фиг.З) работает следующим образом.

При подаче сигнала начальной установки в счетчиках 28 (разрядности N) и 29 (разрядности М) устанавлива- ется код (Кр К , Kg . . .К 0) , период тестирования кратен периоду проверки, поэтому каждый вход элемента И подключен к одному из разрядов счетчика 28 (разрядности N), причем к какому именно плечу - прямому или инверсному, определяется из соотношения

- 2 +.+

КоТ,гК,Т

зг

-к KJ,, 2

г.

Kj

«

,К„ зг

значения соответственно нулевого,первого; N-ro разрядов двоичного числа,определяющего отношение периода срабатывания элемента И 30 к величине Т,,., период последовательности задающего генератора;

12

0

5

0

5

0

5

1- - длительность проведения тестирования.

Формирование сигнала начала проверки на элементе И 30 исключает его совпадение по времени с активной работой устройства при контроле функционирования объекта 20 контроля и с проведением самотестирования.

Блок 3 синхронизации (фиг.4) работает следздощим образом.

Цепь фильтр 32 (основной моды резонансных колебаний), первый формирователь 33, первый дифференцирующий элемент 34, ждущий мультивибратор 35 предназначена для синхронизации времени возбуждения солитона с периодом активности объекта 20 контроля. Для этого отфильтрованный фильтром 32 сигнал основной (рабочей) моды резонансных колебаний после формирования прямоугольного импульса первым формирователем 33 и формирования по переднему фронту указанного прямоугольного сигнала укороченного импульса поступает на информационный вход ждущего мультивибратора 35, длительного выходного сигнала которого определяет длительность солитона, причем передний фронт солитона в этом случае синхронизован с передним фронтом выходного сигнала объекта 20 контроля. Разрешение работы ждущего мультивибратора 35 выдается по сигналу с блока 1 программ.

Цепь фильтр п-й гармоники 36, второй формирователь 37, счетчик 38, схема 39 сравнения, регистр эталонов 40, узел реконфигурации 41, эле- мент 42 запрета предназначена для формирования состояния счетчика 7 в соответствии с характеристиками распространения солитона, возбужда- ющего в объекте 20 контроля уединенную волну на п-й гармонике, за счет многократных отражений эта уединен- ная волна приобретает сложную, неравномерную форму, длительность выбросов которой на уровне срабатывания второго формирователя 37 постепенно увеличивается. Эта форма отражает реальное состояние объекта 20 контроля в данный момент времени. Количество этих выбросов подсчитывается счетчиком 38 и сравнивается схемой 39 сравнения с содержимым эталонного регистра 40, определяющим время анализа уединенной волны, Одновре

менно кодовая последовательность с выхода счетчика 38 поступает на вход блока А1 реконфигура1щи для подстройки полосы пропускания фильтра 36 и для компенсации расширения длительности выбросов.В течение времени анализа уединенной волны на элемент 42 запрета с выхода схемы 39 сравнения подают разрешаюпщй сигнал, поэтому состояние счетчика 7 с тактовой частотой меняется на единицу. Работа блока 3 синхронизации имитируется блоком программ, выдающим разрешающий сигнал на элемент А2 запрета и сигнал обнуления по переднему фронту на счетчик 38.

Объект контроля (фиг.З) работает следующим образом.

Усилитель 45 мощности управляется двухполярным модулированным по частоте сигналом.

Регулятор 49 сравнивает текущее значение выходного напряжения системы питания с опорным значением VQJ, , преобразует полученный сигнал рассогласования в соответствии, например, с пропорционально-интеграль но-дифференциальным законом регулирования и своим выходным напряжением в виде сигнала управления устанавливает частоту генерации генератора 50.

Рабочая точка объекта 20 контроля выбрана на правом склоне амплитудно-частотной характеристики (АЧХ) пьезотрансформатора 46. Диапазон изменения рабочей частоты при стабилизации выходного напряжения в связи с высокой добротностью пьезотрансформатора 46 является узким (например, для пьезотрансформато- ров типа Т11-Э11, не превышает 0,5 кГц при fpo кГц). Поэтому задаюпшй генератор должен быть достаточно стабильным - с нестабильностью по частоте не превышающей 1%. Это необходимо для обеспечения устойчивого положения рабочей точки на правом склоне АЧХ пьезотрансфор- матора 46 во избежание ее перехода на левый склон АЧХ из-за большой нестабильности генератора 50,

Задающий генератор 50 представляет собой з равляемый по частоте генератор прямоугольных импульсов, по- строенньй на базе операционного усилителя 51 с мостовой времязаданяцей цепью (резисторы 52 и 53 и конден

5

0

Q

5

0

5

0

5

0

5

саторы 54 и 55) и конденсатором 56. Установка частоты задающего генератора 50 осуществляется изменением емкости в одном из плечей моста. В качестве управляемого конденсатора

57может быть использована, например, емкость р-п-перехода варикапа, соединенного через конденсаторы

58и 59 с конденсатором 55 моста. Управляющее напряжение с выхода регулятора 49 подается на конденсатор 57 через резистор 60. Выходные импульсы задающего генератора 50 удвоенной рабочей частоты поступают на формирователь 61 ступеньки-паузы и на счетньш вход триггера 62, который делит частоту задающего генератора на два. Формирователь 61 выра- батывает прямоугольные отрицательные импульсы, равные по длительности времени рассасывания зарядов неосновных носителей в базах мощных транзисторов усилителя 45 мощности, которые поступают на один из входов ключей.63 и 64. Один иа выходов триггера соединен с входом ключа 63, а другой - с входом ключа 64. Ключ

63(64) реализует логическую функцию И-НЕ по двум входам, т.е. прерьшает ток в первичной обмотке трансформатора 65 (66) при появлении на обоих входах ключа логической 1. Формирователь 61, триггер 62 и ключи 63 и

64образуют две последовательности импульсов с одинаковым периодом и сдвинутых относительно друг друга на полпериода. Вторичная обмотка импульсного трансформатора 65 (66) усилителя 45 мощности нагружена на переход база-эмиттер выходного транзистора 71 (72) и на включенный в обратном направлении р-птпереход диода 73 (74). Последний необходим для защиты перехода база-эмиттер от перенапряжений отрицательной полярности. Резистор 67 (68) предназначен для установки тока базы транзистора 71 (72) при настройке схемы. Выходное напряжение усилителя 45 мощности через развязывающий конденсатор 75 поступает на вход пьезотрансфор- матор 46,

При подаче на входы пробного воздействия и коррекции одиночных волн- солитонов внутренние электрофизиче- |ские параметры пьезотрансформатора ,46 изменяются, что зарегистрируется

датчикаьш 15, подключаемыми к объекту 20 контроля,

Пьезотраргсформатор (фиг,6) работает следующим образом.

Сигнал с усилителя 45 мощности подается на входные электроды 81, где преобразуется вследствие пьезо- эффекта в акустические колебания, которые на выходном электроде 84 преобразуются в электрические колебания, В резонансном режиме напряжение на выходе пьезотрансформатора 46 в К («100) раз больще напряжения на входе. При подаче на входной электрод 82 коррекции относительно электродов 81, размещенных на поперечно поляризованной секции, возбуждаются пробные воздействия (со- литоны), При подаче напряжений на размещенный на выходной секции электрод 83 коррекции относительно нижнего электрода 81 в пьезотрансфор- маторе 46 производится сдвиг резонансной частоты и соответственно коррекция характеристик параметров.

Изображенный на фиг,7 датчик работает следующим образом.

При подаче пробного воздействия (или воздействия коррекции) на пье- зотрансформатор 46 в рамке щупа 85 наводятся токи, которые усиливаются в операционном усилителе 86, Далее сигнал поступает на обработку в фа- зовый детектор 87, где выделяется частота и фаза сигнала.

Таким образом, предлагаемое устройство позволяет осуществлять периодический допусковый контроль параметров сложных технических объектов, организовать самотестирование устройства за счет моделирования откликов объекта на одиночные импульсы Такая организация контроля на для сложных цифроаналоговых объектов j имеющих значительный разброс внутренних электрофизических характеристик. Кроме того, достоверность контроля повышается за счет введения корректирующего одиночного импульса.

Формула изобретения

1, Устройство для контроля сложных объектов, содержащее подключен- ные к объекту контроля датчики параметров, блок коммутации, блок нор- мализаияи, вычитатель, блок индика0

5

0

5

0

5

0

5

0

5

ции, блок регистрации, блок постоянной памяти, блок программ, блок синхронизации, выходы датчиков параметров соединены с сигнальным входом блока коммутации, выход которого соединен с информационным входом блока нормализации, первый выход которого соединен с первым входом блока индикации, второй вход которого соединен с первым выходом вычитате- ля, второй и третий выходы которого i соединены соответственно с входами блока регистрации и блока постоянной памяти, выходом соединенного с первым входом управления блока программ и третьим входом блока индикации, первый выход блока программ связан с зшравляющим входом блока регистрации, а второй выход - с управляющим входом блока синхронизации, первым синхровыходом соединенного с синхро- входом блока программ, отличающееся тем,, что, с целью повышения достоверности контроля, в него введены блок репрограммируемой памяти, блок оперативной памяти, счетчик, формирователь временной диаграммы, преобразователь пробного воздействия, регистра пробного воздействия, преобразователь коррекции, регистр коррекции, формирователь сигналов, с третьего по одиннадцатый выходы блока программ соединены соответственно с управляющими входами блока коммутации, блок нормализации, формирователя сигналов, с входами записи блока репрограммируемой памяти и блока оперативной памяти, с входом Запись блока регистрации, с входами чтения блоков репрограммируемой и оперативной памяти, со счетным входом формирователя временной диаграммы, с сигнальными входами регистра коррекции и регистра пробного воздействия, выходом соединенного с информационным входом преобразователя пробного воздействия, выход регистра коррекции соединен с информационным входом преобразователя коррекции, синхровход преобразователя пробного воздействия подключен к первому синхровыходу блока синхронизации, выходы преобразователей пробного воздействия и коррекции являются соответственно первым и вторым выходами устройства для подключения к информационным входам объекта контроля, з.адающий вход блока синхронизации является синхровходом устройства, второй синхровыход блока синхронизации соединен со счетным входом счетчика, выход которого соединен с адресными входами блоков репрограммируемой и оперативной памяти, информационными входами соединенных с вторым информационным выходом блока нормализации, выход блока оперативной памяти текущих значений соединен с входом уменьшаемого вычи- тателя, выход блока постоянной памяти соединен с входом вычитаемого вы- читателя и с информационным входом формирователя сигналов, выход которо , го соединен с вторым сигнальным входом блока коммутации, выходы периода тестирования, периода проверки фор- fflpoвaтeля временной диаграммы соединены соответственно с входами начала самотестирования и начала проверки блока программ, синхровходом и вторым входом управления подключенного к третьему синхровыходу блока синхронизации и управляющему входу ус- тановки устройства соответственно, входы датчиков параметров и устано- вочньй вход блока синхронизации являются информационным входом устройства.

ключены соответственно к входам с второго по четвертый модификатора, выход дешифратора подключен к входу данных узла постоянной памяти.

4с Устройство поп,1, отли- ;Чающееся тем, что блок синхронизации содержит первьш фильтр, первый формирователь, первый дифференцирующий элемент, ждущий мультивибратор, второй фильтр, второй формирователь, счетчик, схему сравнения регистр, узел реконфигур ации, элемент запрета, второй дифференцирующий элемент, вход первого фильтра соединен с синхровходок блока синхронизации, выход - с входом первого формирователя, выход которого соединен с входом первого дифференцирующего элемента, выход которого соединен с входом запуска ждущего мультивибратора, выход которого является третьим синхровыходом блока синхронизации, вход второго фильтра соединен с синхровходом блока синхронизации, выход - с входом второго формирователя, выходом соединенного со счетным входом счетчика, выходы которого соответственно соединены с первыми входами схемы сравнения и узла тестирования, вторые входы схемы сравнения соединены с соответствующими выходами регистра, а выход - с входом запрета элемента запрета и с входом второго дифференцируклцего элемента, информационный вход схемы запрета является информационным входом и вторым синхровыходом блока син Хронизации, выход элемента запрета является третьим синхровыходом блока синхронизации, вход запрета элемента запрета и вход запрета ждvщeгo мультивибратора являются управляющим входом блока синхрйнизации, выход второго дифференцирующего элемента соединен с входом обнуления

19 Отг От 2

/с/ я5 к9 кЮ кЮ Н11 к}8 кв

От

счетчика, а выход блока реконфигурации соединен с управляющим входом фильтра.

Фие. 3

L.

0

Jrz W

;

J

( Начала

Выдар режима, П (формирований} J-. эталонов:

Начальная установка

I

90

Е

Возаейстбие сформировано

±

оВъект 92 контроля

опрошен

ПреооразаВагние ait фимтраци у помех, нормализации резимто- тов

Нет

6o3deucm8ufl

сформированы I

коррекция парамбтро8 объекта контроля

JanijCKт

формиробатеАЯ Временной диаграммы

Физ.в5

Состояние 1 mpussepa/xf3 решение cvf-,

Pmui контролй

Режим само тестиро6а,- нияJ

Начальная 1 установка 8е- MWHbi Вноси-1. тй ошидки

считывание эта- лона 3ij с Злока П

QffpaniHoe прео(

т

Т

т

Т

Фиг.8в

иг.Вг

| Авторское свидетельство СССР № 814112, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля параметров функционирования сложных технических объектов | 1977 |

|

SU690448A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-09-23—Публикация

1987-11-13—Подача