Изобретение относится к запоминающим устройствам и может быть использовано при создании высоконадежной памяти, в которой контроль данных производится по массивам. Известно запоминающее устройство с автономным контролем, содержащее накопитель, регистр числа, блок свертки по модулю два, сумматор, регистр контрольного слова и блок анализа количества единиц. В таком устройстве при записи данных в сумматоре формируется контрольное слово которое затем пересылается в регистр контрольного слова. В режиме считывания с ПОМОЩ1ЯО блока свертки по модулю два производится поочередное считывание всех слов из массива данных накопителя и сложение их с контрольным словом Б сумматоре. При этом в сумматоре образуется слово, содержащее нули в разрядах, соответствующих разрядам запоминающего устройства, в которых нет ощибки или есть ощибка четной кратности, и единицы в разрядах, где есть ошибки нечетной кратности. Одиночная ощибка исправляется считыванием слова с ощибкой из накопителя, сложением его с содержанием сумматора и записью его по прежнему адресу в накопитель 1 . Недостатками известного устройства являются ограниченные возможности контроля, которые заключаются в том, что обнаруживаются ощибки только нечетной кратности и исправляются одиночные ощибки, а также наличие дополнительных операций, связанных с пересылкой контрольного слова из сумматора в регистр контрольного слова и обратно, что снижает надежность и быстродействие устройства. Наиболее близким по технической сущности к изобретению является запоминающее устройство с автономным контролем, содержащее накопитель, регистр числа, блок свертки по модулю два, блок анализа количества единиц и реверсивные счетчики по числу разрядов устройства, одни из входов которых подключены к одним выходам регистра числа, другие входы являются управляющими, а выходы соединены с входами блока анализа единиц, выходы которого подключены к одним входам регистра числа, другие входы регистра числа соединены с .выходами накопителя, а одни из выходов подключены соответственно к входам блока свёртки по модулю два и к входам накопителя. В известном устройстве при записи массива данных с помощью реверсивных счетчиков формируется контрольное слово, i-й разряд которого является суммой количества единиц в i-x разрядах всех слов массива, взятой по модулю К , где п - количество разрядов реверсивных счетчиков. При записи в j-ю ячейку массива отдельного слова предварительно производится считывание хранимого там числа на регистр слова и вычитание его из контрольного слова, хранящегося в реверсивных счетчиках. Затем записываемое число принимается на регистр числа, складывается с Контрольным словом и записывается в накопитель. При считывании отдельного слова из накопителя с помощью блока свертки по модулю. два проверяется отсутствие в нем ощибок. Если ощибок нет, слово выдается на выход устройства. Если слово счцтано с ощибками, то производится считывание всего массива данных. При этом регистрируются адреса ячеек, из которых данные считываются с ощибками. Реверсивные счетчики при этом работают как вычитающие. Если количество сбоев, поступивших с блока свертки по модулю два, соответствует числу лищних или недостающих единиц, выявленных блоком анализа количества единиц, то производится коррекция ошибок путем инвертирования соответствующих разрядов 2. Недостатками известного устройства являются его низкая надежность и невысокое быстродействие. Низкая надежность устройства обусловлена тем, что если в ячей ках накопителя при записи данных имеются отказавщие разряды, которые искажают записываемые слова, то работоспособсность устройства нарушается. Невысокое быстродействие устройства определяется тем, что при записи отдельного слова в ячейку памяти предварительно считывается ранее записанное слово, считанное слово заносится в регистр числа и затем производится вычитание его из контрольного слова, хранящегося в реверсивных счетчиках. Затем записываемое слово принимается в регистр числа и складывается с контрольным словом в реверсивных счетчиках, а также записывается в накопитель. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее накопитель, регистр числа, блок свертки по модулю два, блок анализа количества единиц и блок реверсивных счетчиков, выходы которого соединены с входами блока анализа количества единиц, информационным входом устройства является первый вход регистра числа, первый выход которого подключен к входу накопителя, введены дополнительный регистр числа, блок сумматоров по модулю два, элемент И, первый и второй элементы ИЛИ, первый и второй блоки элементов ИЛИ, блок элементов И, причем выходы накопителя соединены с одними входами дополнительного регистра числа, другие входы которого соединены с одним выходом блока анализа количества Единиц, другой выход которого является первым выходом

устройства, второй выход регистра числа подключен к первому входу блока сумматоров по модулю два, второй вход которого соединен с первым выходом дополнительного регистра числа и первым входом блока элементов И, выходы блока сумматоров по модулю два соединены с входами второго элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с вторым входом блока элементов И и является одним управляющим входом устройства, выход элемента И соединен с вторым входом регистра числа и первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом дополнительного регистра числа и является вторым В.ЫХОДОМ устройства, второй выход регистра числа подключен к первому входу второго блока элементов ИЛИ, второй вход которого является другим управляющим входом устройства, выход блока сумматоров по модулю два подключен к первому входу первого блока элементов ИЛИ, второй вход которого соединен с выходом блока элементов И, выходы первого, второго блоков элементов ИЛИ и первого элемента ИЛИ подключены соответственно к; первому, второму и третьему входам блока реверсивных счетчиков, третий выход дополнительного регистра числа подключен к входу блока свертки по модулю два, выход которого является тpetьим выходом устройства, четвертый выход дополнительного регистра числа является четвертым выходом устройства и подключен к третьему входу регистра числа.

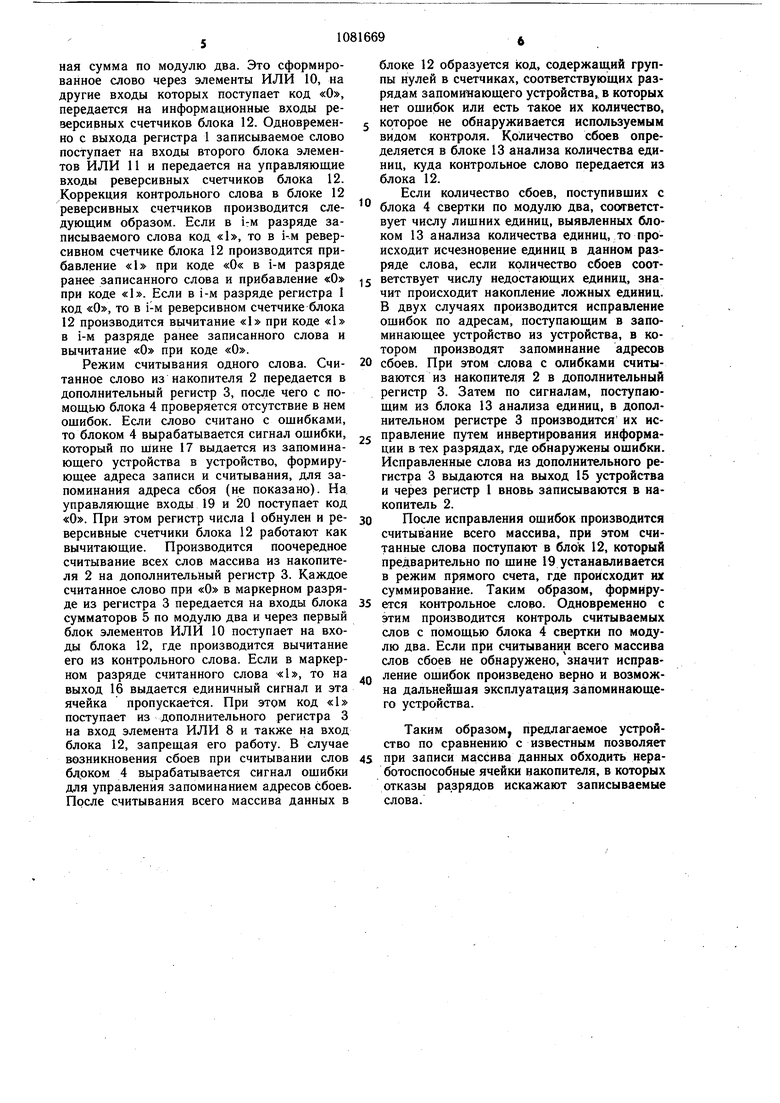

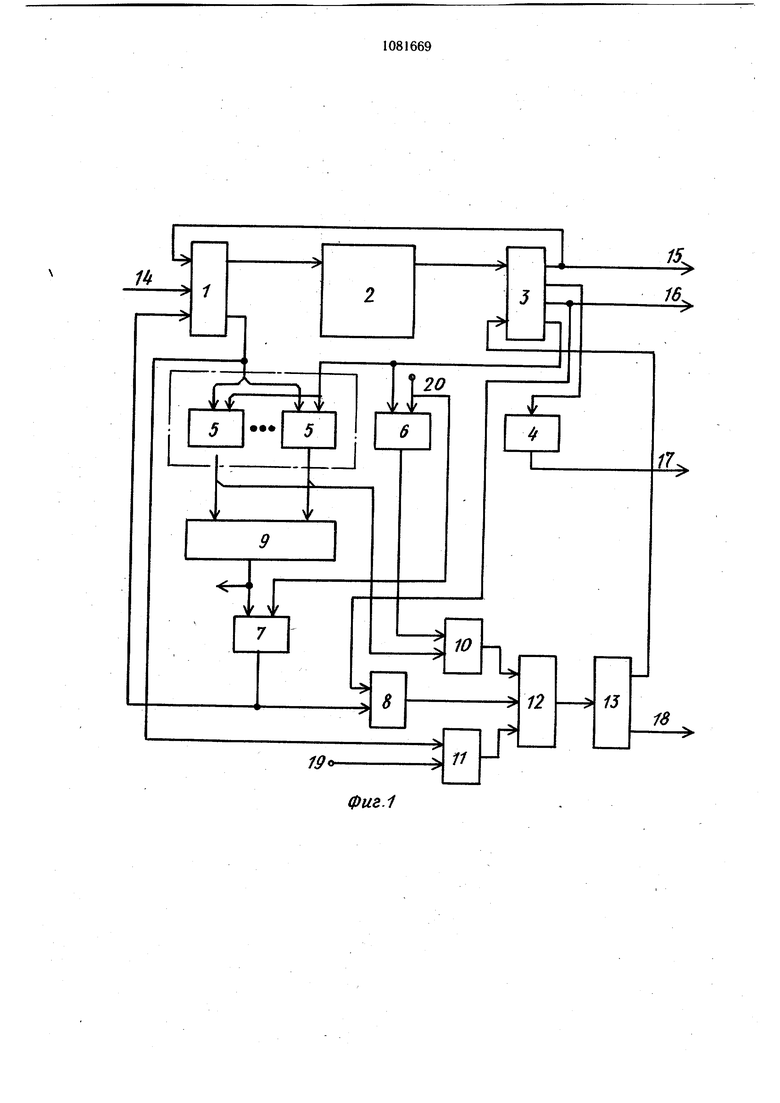

На фиг. 1 изображена структурная схема запоминающего устройства с автономным контролем; на фиг. 2 - функциональная схема блока анализа количества единиц.

Устройство содержит регистр 1 числа, накопитель 2. дополнительный регистр 3 числа, блотс 4 свертки по модулю два, блок 5 сумматоров по модулю два, блок 6 элементов И, элемент И 7, первый 8 и второй 9 элементы ИЛИ, первый 10 и второй И блоки элементов ИЛИ, п-($азрядные реверснвные счетчики, объединенные в блок 12 (пколичество разрядов слова, ) и блок 13 анализа количества единиц. Регистр 1 имеет входные 14, а регистр 3 - выходные 15 щины числа. Дополнительный регистр 3 имеет выход 16с которого выдается значение маркерного разряда слова, блок 4 CBiepTKH по модулю два - выходную цдину 17, а блок 13 .анализа количества единиц - выходную шину 18. Устройство содержит также один управляющий вход 19 И другой управляющий вход 20, блок 22 объединения единиц, блок 23 формирования команд и выходной ключ 24. Блок 13 содержит мультиплексор 21.

Устройство работает следующщим образом.

Режим записи массива слов. В этом режиме записываемое слово поступает с входа 14 в регистр I и заносится .в накопитель 2. Затем производится чтение записанного слова (с восстановлением в накопителе 2) на дополнительный регистр 3- Содержимое регистра 1 и 3 поступает в блок 5 сумматора по модулю два. Если слово записано и считано без ощибок, то содержимЪе этих регистров совпадает и на выходах блока 5

0 , суммйторов по модулю два и элемента ИЛИ 9 будет код «О. На управляющих вход 20 подается код «1, которых разрешает прохождение слова из дополнительного регистра 3 через блок 6 элементов И и первый блок 10 э.лементов ИЛИ на вход блока 12.

Одновременно на все управляющие входы 19 подается код «1, при котором реверсивные счетчики блока 12 работают как суммирующие. Записанное слово в блоке 13 складывается с контрольным словом.

0 Если слово записано и считано из-за отказов разрядов ячеек с ошибками, то на соответствующих выходах блока 5, сумматоров по модулю два и выходе элемента ИЛИ 9 будет код «1. По сигналу «1, поступающему на вход 20, на выходе эле5 мента И 7 формируется единичный уровень, который записывается в маркерный разряд регистра числа «1 и, поступая через элемент ИЛИ 8 на вход блока 12, запрещает его работу. Маркерный разряд

« из регистра 1 записывается в соответствующую ячейку накопителя 2 и из-за этого она исключается из работы. Затем производится гашение маркерного разряда регистра 1 в «О (цепь гащения на фиг. 1 не показана) и запись того же слова в следующую ячей5 ку, работоспособность которой также проверяется. Другие слова массива записываются аналогично.-Таким образом, после записи массива слов все ячейки накопителя- 2, отказы в которых искажают записываемые слова, исключаются из работы, а в

блоке 12 формируется контрольное слово для

записанного массива.

Режим записи отдельного слова. Этот режим используется в случае, когда необходимо вместо одного слова массива

5 записать другое. При этом производится считывание из накопителя 2 ранее записанного слова на дополнительный регистр 3. Записываемое слово с входа 14 поступает на регистр 1. При этом на вход .20 и входы 19 поступает код «О. Элемент И 7 закрыт.

0 С выхода 16 дополнительного регистра 3 на вход элемента ИЛИ 8 поступает нулевое значение маркерного разряда. Так как на оба входа элемента ИЛИ 8 поступает код «О, то на выходе его также будет нулевой сигнал, разрешающий работу реверсивных счетчиков блока 12. Содержимое регистров 1 и 3 поступает на вход блока 5 сумматоров по модулю два, где формируется поразрядная сумма по модулю два. Это сформированное слово через элементы ИЛИ 10, на другие входы которых поступает код «О, передается на информационные входы реверсивных счетчиков блока 12. Одновременно с выхода регистра 1 записываемое слово поступает на входы второго блока элементов ИЛИ 11 и передается на управляющие входы реверсивных счетчиков блока 12. Коррекция контрольного слова в блоке 12 реверсивных счетчиков производится следующим образом. Если в irM разряде записываемого слова код «1, то в i-м реверсивном счетчике блока 12 производится прибавление «1 при коде «0« в i-M разряде ранее записанного слова и прибавление «О при коде «1. Если в i-м разряде регистра 1 код «О, то в i-M реверсивном счетчике блока 12 производится вычитание «1 при коде «1 в i-M разряде ранее записанного слова н вычитание «О при коде «О.

Режим считывания одного слова. Считанное слово из накопителя 2 передается в дополнительный регистр 3, после чего с помощью блока 4 проверяется отсутствие в нем ошибок. Если слово считано с ошибками, то блоком 4 вырабатывается сигнал ошибки, который по иаине 17 выдается из запоминающего устройства в устройство, формирующее адреса записи и считывания, для запоминания адреса сбоя (не показано). На управляющие входы 19 и 20 поступает код «О. При этом регистр числа 1 обнулен и реверсивные счетчики блока 12 работают как вычитающие. Производится поочередное считывание всех слов массива из накопителя 2 на дополнительный регистр 3. Каждое считанное слово при «О в маркерном разряде из регистра 3 передается на входы блока сумматоров 5 по модулю два и через первый блок элементов ИЛИ 10 поступает на входы блока 12, где производится вычитание его из контрольного слова. Если в маркерном разряде считанного слова «1, то на выход 16 выдается единичный сигнал и эта ячейка пропускается. При этом код «U поступает из дополнительного регистра 3 на вход элемента ИЛИ 8 и также на вход блока 12, запрещая его работу. В случае возникновения сбоев при считывании слов бдоком 4 вырабатывается сигнал ошибки для управления запоминанием адресов сбоев. После считывания всего массива данных в

блоке 12 образуется код, содержащий группы нулей в счетчиках, соответствующих разрядам запоминающего устройства, в которых нет ошибок или есть такое их количество, 5 которое не обнаруживается используемым видом контроля. Количество сбоев определяется в блоке 13 анализа количества единиц, куда контрольное слово передается из блока 12.

Если количество сбоев, поступивших с

блока 4 свертки по модулю два, соответствует числу лишних единиц, выявленных блоком 13 анализа количества единиц, то происходит исчезновение единиц в данном разряде слова, если количество сбоев соот5 ветствует числу недостающих единиц, значит происходит накопление ложных единиц. В двух случаях производится исправление ошибок по адресам, поступающим в запоминающее устройство из устройства, в котором производят запоминание адресов

0 сбоев. При этом слова с олибками считываются из накопителя 2 в дополнительный регистр 3. Затем по сигналам, поступающим из блока 13 анализа единиц, в дополнительном регистре 3 производится их ис5 правление путем инвертирования информации в тех разрядах, где обнаружены ошибки. Исправленные слова из дополнительного регистра 3 выдаются на выход 15 устройства и через регистр 1 вновь записываются в накопитель 2.

0 После исправления ошибок производится считыв ание всего массива, при этом считанные слова поступают в блок 12, который предварительно по шине 19 устанавливается в режим прямого счета, где происходит их суммирование. Таким образом, формиру5 ется контрольное слово. Одновременно с этим производится контроль считываемых слов с помощью блока 4 свертки по модулю два. Если при считывании всего массива слов сбоев не обнаружено, значит исправQ ление ошибок произведено верно и возможна дальнейшая эксплуатация запоминающего устройства.

Таким образом, предлагаемое устройство по сравнению с известным позволяет 5 при записи массива данных обходить неработоспособные ячейки накопителя, в которых отказы разрядов искажают записываемые слова.

фиг.1

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942164A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с обнаружением ошибок | 1980 |

|

SU881876A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее накопитель, регистр числа, блок свертки по модулю два, блок анализа количества единиц и блок реверсивных счетчиков, выходы которого соединены с входами блока анализа количества единиц, информационным входом устройства является первый вход регистра числа, первый выход которого подключен к входу накопителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительный регистр числа, блок сумматоров по модулю два, элемент И, первый и второй цементы ИЛИ, первый и второй блоки элементов ИЛИ, блок элементов И, причем выходы накопителя соединены с одними входами дополнительного регистра числа, другие вхЬды Которого соединены с одним выходом блока анализа количества единиц, другой выход которого является первым выходом устройства, второй выход регистра числа подключен к первому входу блока сумматоров по модулю два, второй вход которого соединен с первым выходом дополнительного регистра числа и первым входом блока элементов И, выходы блока сумматоров по модулю два соединены с входами второго элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с вторым входом блока элементов И и является одним управляющим входом устройства, выход элемента И соединен с вторым входом регистра числа и первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом дополнительного регистра числа и является вторым выходом устройства, второй выход регистра числа подключен к первому входу второго блока элементов ИЛИ, второй вход которого является i другим управляющим входом устройства, выход блока сумматоров по модулю два (Л подключен к первому входу первого блока элементов ИЛИ, второй вход которого соединен с выходом блока элементов И, выходы первого, второго блоков элементов ИЛИ и первого элемента ИЛИ подключены соответственно к первому, второму и третьему входам блока реверсивных счетчиков, третий выход дополнительного регистра числа СХ) подключен к входу блока свертки по модулю два, выход которого является третьим О5 выходом устройства, четвертый выход доО5 полнительного регистра числа является четвертым выходом устройства и подключен к третьему входу регистра числа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU452860A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942164A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-03-23—Публикация

1983-01-18—Подача