(5) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ДОПОЛНИТЕЛЬНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1979 |

|

SU789992A1 |

| Счетчик импульсов | 1979 |

|

SU790346A1 |

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

| Устройство для формирования и хранения вычетов чисел по модулю три | 1983 |

|

SU1109755A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| Двоичный счетчик | 1973 |

|

SU558403A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования последовательного двоичного кода в дополнительный код Известно устройство для формирования дополнительного кода, собранного на инверторе, соединенном с сумматором, на второй вход которого подается импульс младшего разрядаD Недостатком этого устройства для формирования дополнительного кода является сложность реализации сумматора. Известно устройство для формирования дополнительного кода, содержащее полусумматор, первый вход которого соединен с входом устройства а второй через линию задержки - с. выходом собирательной схемы, первый вход которой соединен с первым выходом полусумматора и выходом устройства, а второй вход - с вторы выходом полусумматора Г. . Недостатком данного устройства для формирования дополнительного кода является наличие суммирующего элемента - полусумматора. Наиболее близким к изобретению является устройство для формирования дополнительного кода, в котором отсутствует суммирующий элемент. Это устройство содержит триггер, выходы которого подключены к первым входам. двух элементов И, выходы которых подключены к входам элемента ИЛИ, выход которого является рыходом устройства, причем входная шина устройства подк/ж чена непосредственно к второму входу первого элемента И, через инвертор - к второму входу второго элемента И и через элемент задержки к единичному,входу триггера Сз. Недостатком такого устройства для формирования дополнительного кода является относительная сложность его реализации.

Цель изобретения - упрощение устройства.

Указанная цель достигается тем, что устройство для формирования дополнительного кода, содержащее триггер, первый элемент задержки, элемент И, элемент ИЛИ, причем вход устройства соединен с первым входом элемента И и через первый элемент адержки - с единичным входом триггера, выход элемента И соединен с первым входом элемента ИЛИ, выход которого подключен к выходу устройства, содержит второй элемент задержки, вход которого соединен с нулевым выходом триггера, а выход - с вторым входом элемента И, единичный выход триггера соединен со вторым входом элемента ИЛИ, вход устройства соединен с нулевым входом триггера.

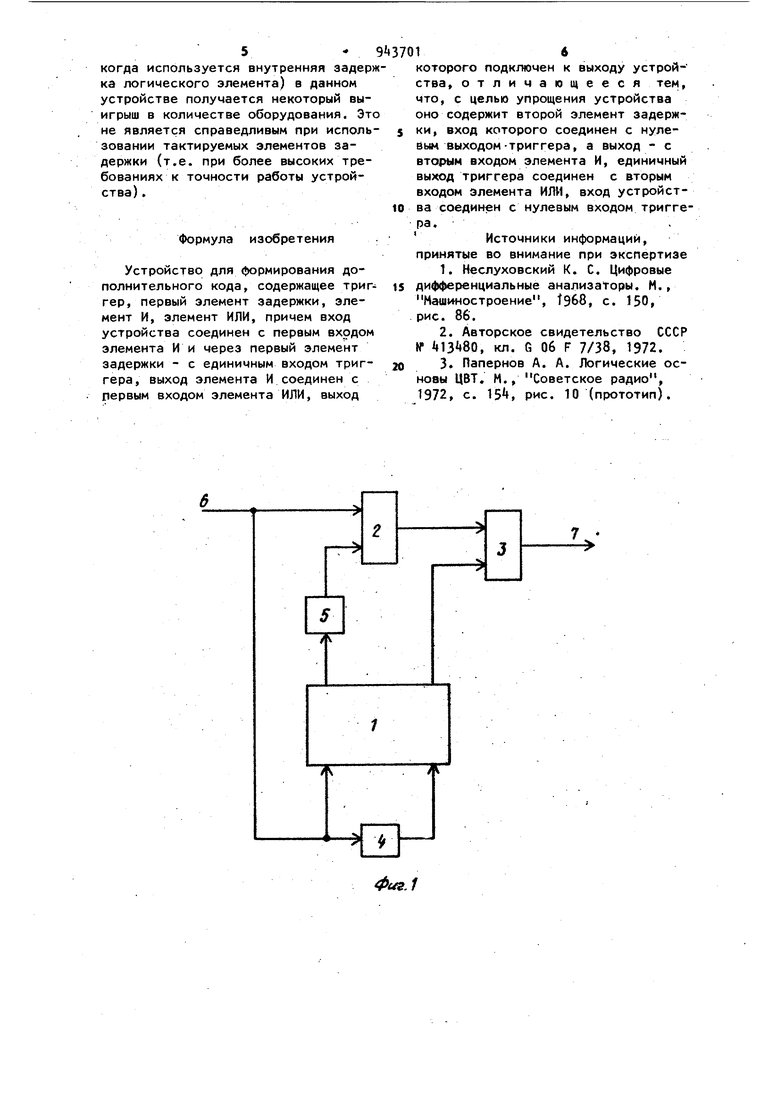

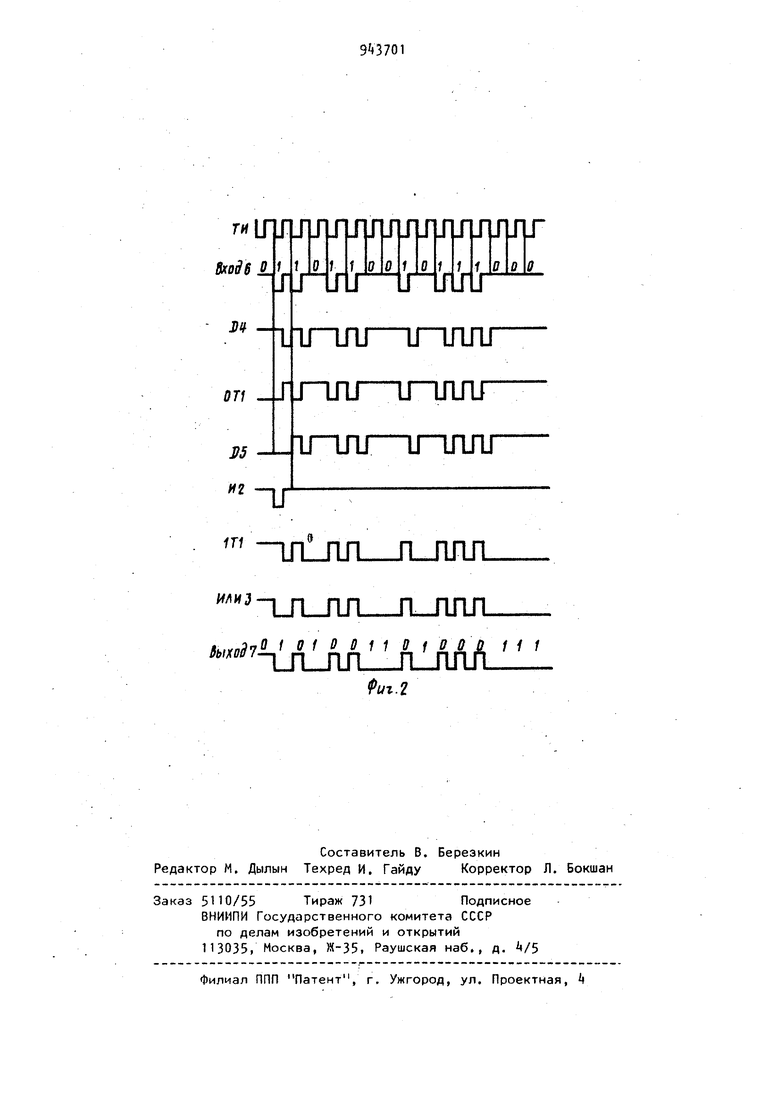

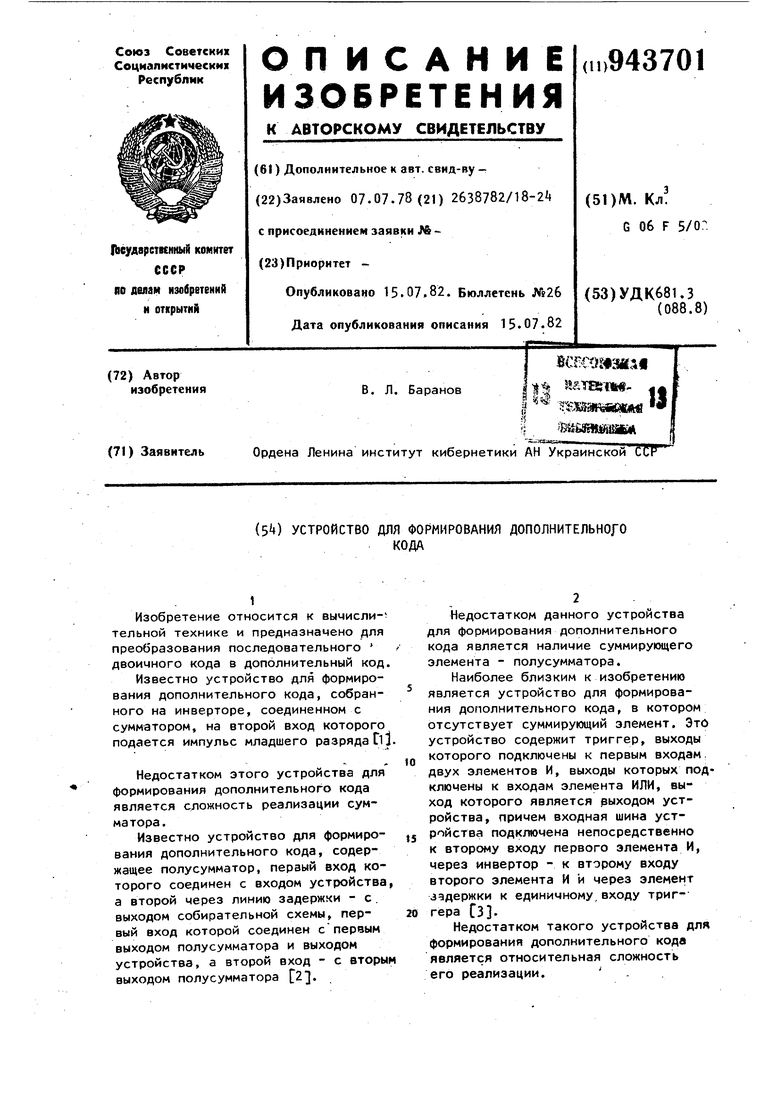

На фиг. 1 изображена функциональная схема устройства для формирования дополнительного кода; на фиг.2временная диаграмма его работы.

Устройство для формирования дополнительного кода содержит триггер 1, элемент И 2, элемент ИЛИ 3, два элемента задержки j и 5 вход 6 и выход 7. Единичный вход триггера 1 подключен к выходу элемента задержки Ц, вход которого подключен к ь левому входу триггера 1, первому входу элемента И 2 и входу 6. Элемент ИЛИ 3 подключен первым входом, к выходу элемента И 2, вторым входом - к единичному выходу триггера 1 и выходом к выходу 7. Нулевой выход триггера 1 подключен к входу элемента задержки 5, выход которого подключен к второму входу элемента И 2.

Устройство для формирования дополнительного кода работает следующим образом.

В исходном состоянии триггер 1 на ходится в нулевом состоянии, элемент И 2 открыт единичным сигналом нулевого выхода триггера 1, поступающим через элемент задержки 5 на второй вход элемента И 2. На втором входе элемента ИЛИ 3 действует Нулевой сигнал единичного выхода триггера 1. Последовательный двоичный код поступает по входу 6, начиная с младших разрядов, на первый вход элемента И 2. Все младшие разряды последовательного двоичного кода, включая первую младшую единицу, проходят через элемент И 2 и ИЛИ 3 на выход 7. Перпая младшая единица

входного двоичного кода, задерживаясь элементом задержки 4 на время длительности входного импульса, поступает на единичный вход триггера 1,

устанавливая его в единичное состояние. Если в следующем разряде после первой младшей единицы двоичного кода поступает нулевой код, то единичное состояние триггера 1 сохраняется и на выход 7 через элемент ИЛИ 3 с единичного выхода триггера 1 проходит сигнал единичного кода. Если в следующем разряде после первой младшей единицы двоичного кода поступает единичный код, то триггер 1 переходит в нулевое состояние, что приводит к установке на втором входе элемента ИЛИ нулевого сигнала единичного выхода триггера 1. Единичный код, поступающий на первый вход элемента И 2, на выход элемента И 2 не проходит; так как элемент задержки 5 задерживает на длительность входного импульса поступление единичного

сигнала с нулевого выхода триггера 1 на второй вход элемента И 2. Таким образом, в момент действия на входе 6 единичного кода на выходе 7 действует нулевой код. Импульс единичного кода, действующий на входе 6, поступает через элемент задержки 4 на . единичный вход триггера 1, устанавливая.его в единичное состояние. Остальные разряды входного двоичного кода обра15атываются устройст

вом аналогичным образом.

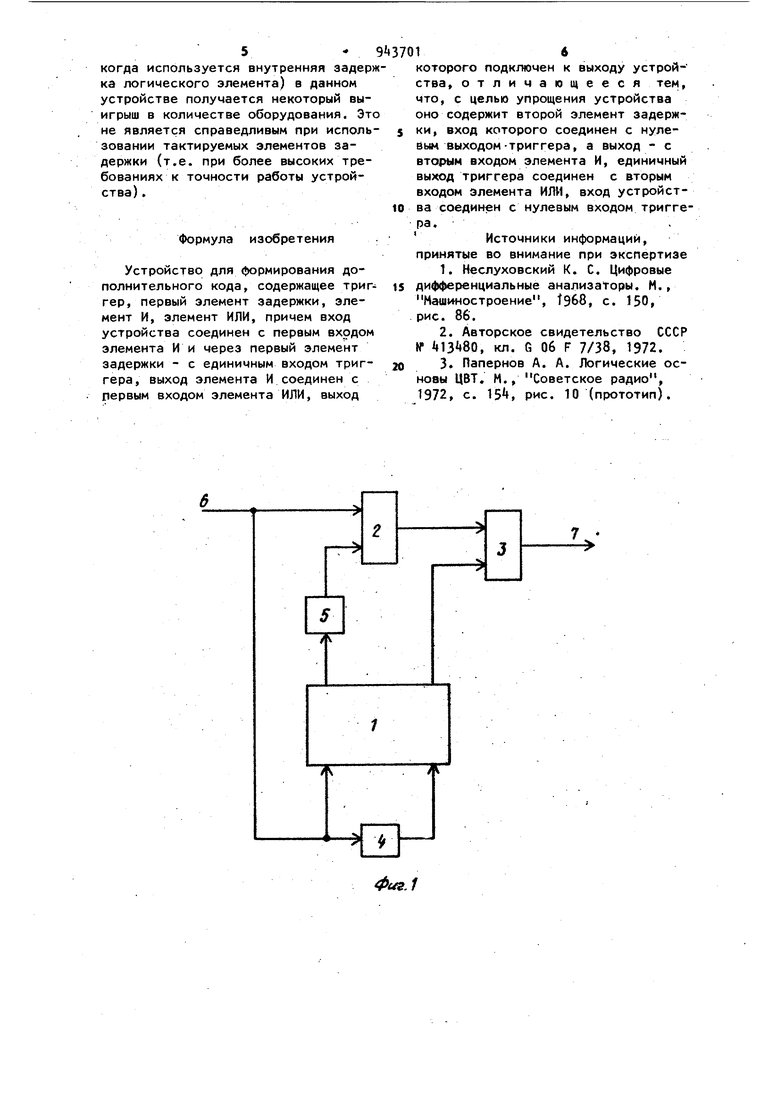

В целях иллюстрации работы предложенного устройства на фиг.2 изображена временная диаграмма его работы, которая составлена для импульсов отрицательной полярности в системе низких потенциалов. Поступление на вход 6 последовательного двоичного кода и считывание с выхода 7 проис-,

ХОДИТ по тактовым импульсам ТИ.

На вход 6 поступает, начиная с младших разрядов, двоичный код 0001110100110110, который прео.бразуется на выходе 7 в дополнительный

код 1110001011001010.

По сравнению с известным в данном устройстве устранен один элемент И и элемент НЕ и введен второй элемент задержки. При малой критичности ко,

времени задержки элемента задержки (когда такой элемент задержки не является тактированным и выполнен просто на логическом элементе, т.е.

когда используется внутренняя задержка логического элемента) в данном устройстве получается некоторый выигрыш в количестве оборудования. Это не является справедливым при использовании тактируемых элементов задержки (т.е. при более высоких требованиях к точности работы устройства) ,

Формула изобретения .

Устройство для формирования дополнительного кода, содержащее триггер, первый элемент задержки, элемент И, элемент ИЛИ, причем вход устройства соединен с первым входом элемента И и через первый элемент задержки - с единичным входом триггера, выход элемента И соединен с первым входом элемента ИЛИ, выход

которого подключен к выходу устройства, отличающееся тем, что, с целью упрощения устройства оно содержит второй элемент задержки, вход которого соединен с нулевым выходом -триггера, а выход - с вторым входом элемента И, единичный выход триггера соединен с вторым входом элемента ИЛИ, вход устройства соединен с нулевым входом триггера.

Источники информации, принятые во внимание при экспертизе

Наш1 ностроение, t968, с. 150, рис. 86.

« 1Г1Ш1ЛЛЛЛГ1ЛЛГ1ЛЛПЛГ

о

jrui

irmj-1гтллг

1

jnjij-innjir

1

irmr-innnr

И2

If

1Г1

1 rLJUl JL JUia

fc,7l, Д,й-г

пши

Авторы

Даты

1982-07-15—Публикация

1978-07-07—Подача