Изобретение относится к вычислительной технике и предназначено для вычитания двоичных чисел. Известно устройство для вычитания содержащее два регистра (уменьшаемого и вычитаемого и одноразрядный вы читатель на три входа 1}. Недостатком такого устройства для 1 вычитания является сложность реализации вычитателя. Известно устройство для вычитания содержащее два регистра, счетчик, два триггера, блок формирования дополнительного кода, сумматор и логические элементы 2. Недостатком этого устройства .вычитания является относительная сложность его реализации. Наиболее близким по технической сущности к предлагаемому является устройство для вычитания, содержащее два регистра, сумматор, первый вход которого соединен с выходом первого регистра, а выход - со входом этого же регистра, два триггера, элемент задержки и элемент И, причем единичный выход первого триггера соединен со вторым входом сумматора и еди ничный вход - с выходом второго регистра, первым входом элемента И и с входом элемента задержки, выход которого подключен к единичному входу второго триггера, единичный выход которого соединен со вторым входом элемента И, выход которого подключен ко входу второго регистра, а нулевые входы обоих триггеров связаны с шиной сброса 3. Недостатком данного устройства является его невысокое быстродействие вследствие задержки на один цикл каждой единицы вычитаемого во втором триггере. Нашичие второго триггера и сумматора на три входа в составе устройства также приводит к его усложнению. Цель изобретения г повышение быстродействия и упрощение устройства. Поставленная цель достигается тем, что в устройство для вычитания, содержащее два регистра, полусумматор, выход которого соединен со входом первого регистра, триггер, элемент задержки, первый элемент И, первый вход которого соединен с прямым выходом второго регистра, введены второй элемент И и элемент ИЛИ, выход которого соединен с первым входом полусумматора, причем единичный выход триггера через элемент задержки соединен со

вторым входом полусумматора, единичный вход триггера соединен с первым входом элемента ИЛИ и выходом первого элемента И, второй вход которого додключен к инверсному выходу первого регистра, нулевой вход триггера соединен со вторым входом элемента ИЛИ и с выходом второго элемента И, подключенного первым входом к прямому выходу первого регистра и вторым входом - к инверсному ёыходу.второго регистра.

Исключение из состава утсройства для вычитания второго триггера, а также замена сумматора на три входа полусумматором позволяет исключить задержку на один цикл каждой единицы вычитаемого, упростить устройство

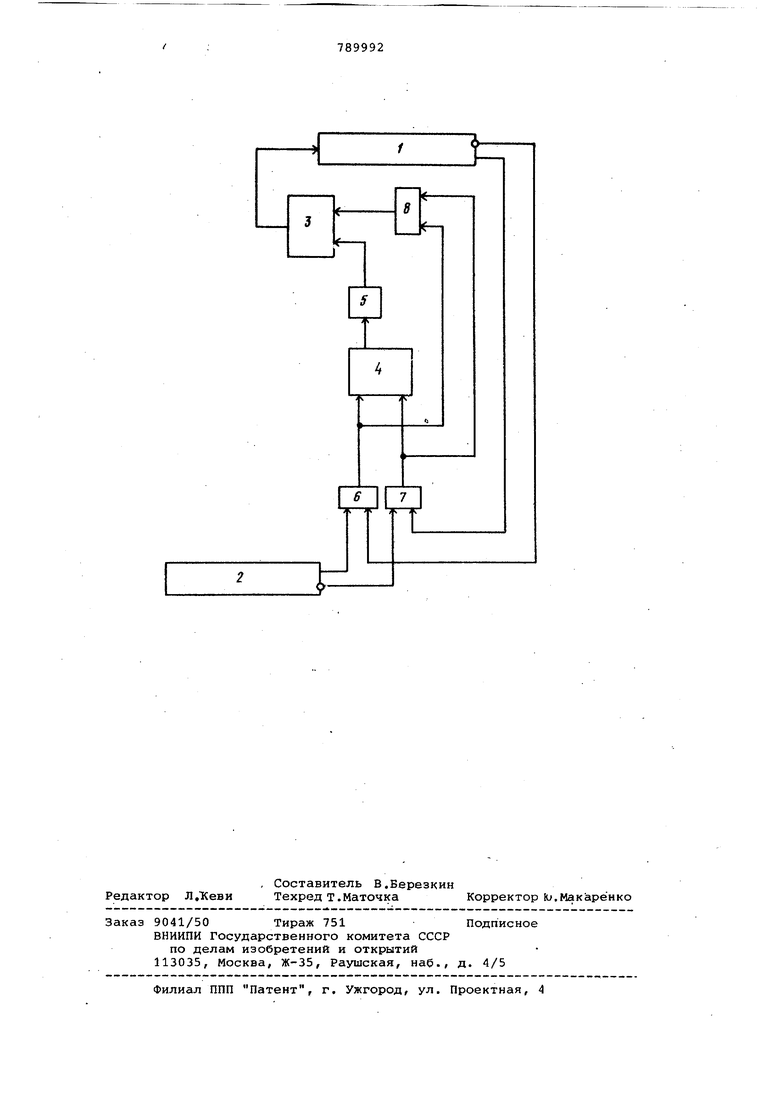

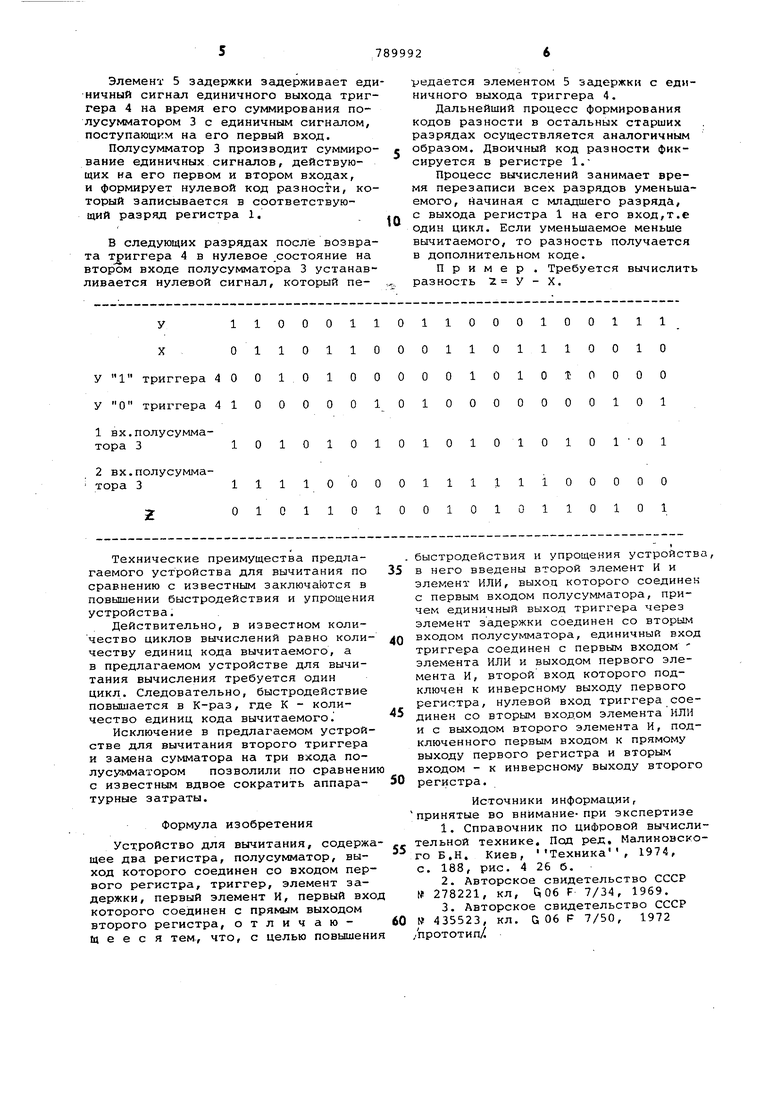

На чертеже изображена структурная схема устройства для вычитания.

Устройство для вычитания содержит два регистра 1 и 2, полусумматор 3, триггер 4, элемент 5 задержки, два элемента И 6 и И 7, элемент ИЛИ 8.

Вход регистра 1 соединен с выходом полусумматора 3. Триггер 4 подключен единичным выходом к входу элемента 5 задержки, единичным входо к выходу элемента И б и первому входу элемента ИЛИ 8, кулевым входом к выходу элемента И 7 и второму входу элемента ИЛИ 8, выход которого подключен к первому входу полусумматора 3, второй вход которого соедине с выходом элемента 5 задержки.

Элемент И 6 подключен первым входом к прямому выходу регистра 2 и вторым входом - к инверсному выходу регистра 1. Элемент И7 подключен первым входом к прямому выходу регистра 1 и вторым входом - к инверсному выходу регистра 2.

Устройство для вычитания работает следующим-образом.

В исходном состоянии триггер 4 находится в нулевом состоянии, в регистр 1 записывается последовательны двоичный код умёйьшаемого У, а в регистр 2 - вычитаемого X.

Двоичные коды уменьшаемого и вычитаемого считываются одновременно последовательным способом, начиная с младших разрядоё, с выходов регистров 1 и 2 соответственно.

До тех пор, пока триггер 4 находится в нулевом состоянии, на его единичном выходе действует нулевой сигнал, который через элемент 5 задержки передается на второй вход полусумматора 3. Следовательно, полусумматор 3 при нулевом состоянии триггера 4 передает без изменения двоичный код, поступающий по его первому входу с выхода элемента ИЛИ 8. Триггер 4 не изменяет своего нулевог состояния до тех пор, пока не срабатывает элемент И6.

Таким образом, при нулевом состоянии триггера 4, в младшие разряды

разности записываются единичные коды только в случае срабатывания элемента И7, выходной сигнал которого через элемент ИЛИ 8 полусумматор 3 записывает в соответствующие разряды разности единичные коды регистр 1. Элемент И 7 срабатывает только в слу.чае наличия в соответствующих разарядах единичного кода уменьшаемого и нулевого кода вычитаемого.

Так продолжается до тех пор, пока не срабатывает элемент И 6, на выходе которого сформировывается выходной сигнал только в случае наличия в соответствующих разрядах нулевого кода уменьшаемого и единичного кода вычитаемого. Единичные сигнал с выхода элемента И 6 записывается через элемент ИЛИ 8 и полусумматор 3 в соответствующий разряд разности в регистре 1 и, поступая на единичный вход триггера 4, переводит его в единичное состояние. Элемент 5 задержки обеспечивает задержку перепада на единичном выходе триггера 4, поддерживая таким образом на втором входе полусумматора 3 нулевой сигнал на время записи единичного сигнала с выхода элемента И 6 через элемент ИЛИ 8 и полусумматор 3 в регистр 1.

В следующих разрядах после переходя триггера 4 в единичное состояние н на втором входе полусумматора 3 действует единичный сигнал единичного выхода триггера 4, который передается через элемент 5 задержки.

Триггер 4 сохраняет единичное состояние до момента срабатывания элемента И 7. При единичном состоянии триггера 4 и закрытых элементах И б и И 7 на выходе элемента ИЛИ 8 действует нулевой сигнал, который передается на первый вход полусуммотора 3, на втором входе которого поддерживается единичный сигнал единичным выходом триггера 4.

В это случае в соответствующие разряды разности в регистр 1 записываются с выхода полусумматора 3 единичные коды.

Срабатывание элемента И б при единичном состоянии триггера 4 не изменяется его единичного состояния. Однако выходной сигнал- элемента И б, поступая через элемент ИЛИ 8 на первый вход полусумматора 3, на втором входе которого действует единичный сигнал единичного выхода триггера 4, обеспечивает формирование на выходе полусумматора 3 нулевого кода, который записывается в соответствующий разряд разности в регистр 1.

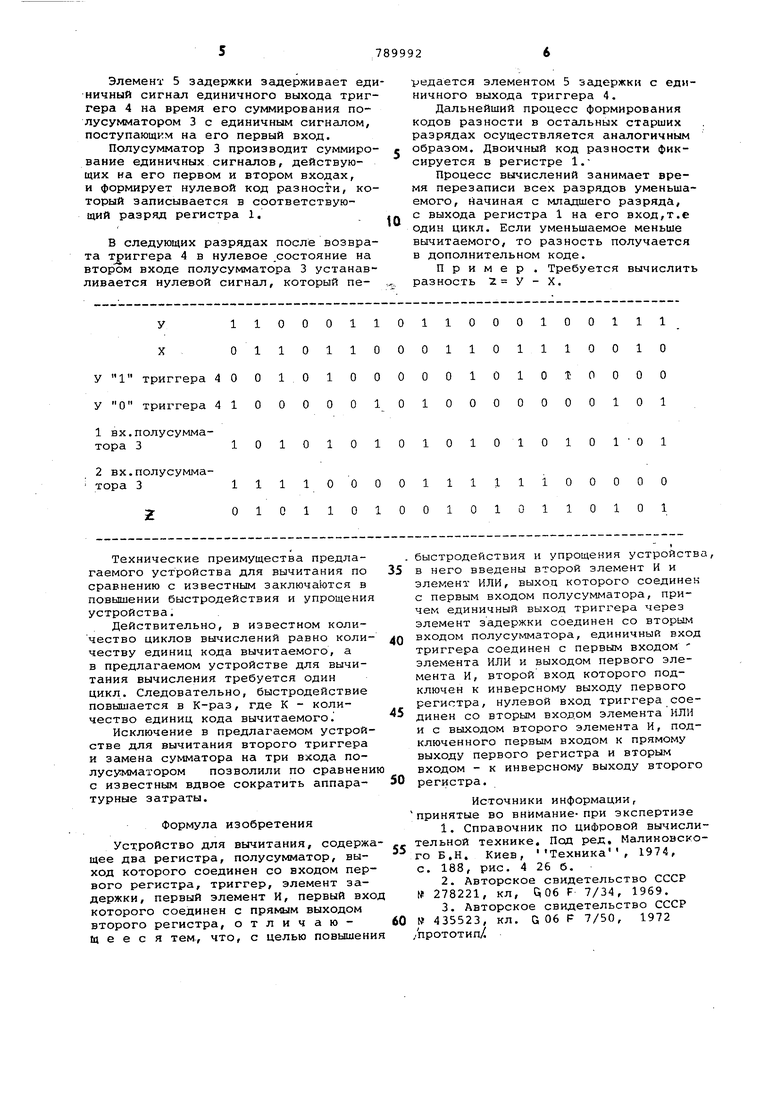

Так продолжается до срабатывания элемента И 7, выходной сигнал которого через элемент ИЛИ 8 поступает на первый вход полусумматора 3 и сбрасывает триггер 4 в нулевое состояние. Элемент 5 задержки задерживает еди ничный сигнал единичного выхода триггера 4 на время его суммирования полусумматором 3 с единичным сигналом, поступающим на его первый вход. Полусумматор 3 производит суммирование единичных сигналов, действующих на его первом и втором входах, и формирует нулевой код разности, который записывается в соответствующий разряд регистра 1. В следующих разрядах после возврата т иггера 4 в нулевое состояние на втором входе полусумматора 3 устанавливается нулевой сигнал, который пеУ110001101X011011000 у 1 триггера 4001010000 У О триггера 4100000101 1 вх.полусуммаlOlOlOlOlтора 3 2 вх.полусумматора 3111100001 у 010110100

Технические преимущества предлагаемого устройства для вычитания по сравнению с известным заключаются в повышении быстродействия и упрощения устройства.

Действительно, в известном количество циклов вычислений равно количеству единиц кода вычитаемого, а в предлагаемом устройстве для вычитания вычисления требуется один цикл. Следовательно, быстродействие повышается в К-раз, где К - количество единиц кода вычитаемого.

Исключение в предлагаемом устройстве для вычитания второго триггера и замена сумматора на три входа полусумматором позволили по сравнени с известным вдвое сократить аппаратурные затраты.

Формула изобретения

Устройство для вычитания, содержащее два регистра, полусумматор, выход которого соединен со входом первого регистра, триггер, элемент задержки, первый элемент И, первый вхо которого соединен с прямым выходом второго регистра, отличающееся тем, что, с целью повышени

t

. быстродействия и упрощения устройства, в него введены второй элемент И и элемент ИЛИ, выход которого соединен с первым входом полусумматора, причем единичный выход триггера через элемент задержки соединен со втopы входом полусумматора, единичный вход триггера соединен с первым входом элемента ИЛИ и выходом первого элемента И, второй вход которого подключен к инверсному выходу первого регистра, нулевой вход триггера соединен со BTOpfcJM входом элемента ИЛИ и с выходом второго элемента И, подключенного первым входом к прямому выходу первого регистра и вторым входом - к инверсному выходу второго регистра.

Источники информации, принятые во внимание-при экспертизе

1.Справочник по цифровой вычислительной технике. ПсД ред. Малиновского Б.Н. Киев, Техника, 1974,

с. 188, рис. 4 26 б.

2.Авторское свидетельство СССР № 278221, кл, G,06 F 7/34, 1969.

3.Авторское свидетельство СССР 0 W 435523, кл. G 06 F 7/50, 1972

/прототип/ редается элементом 5 задержки с единичного выхода триггера 4. Дальнейший процесс формирования кодов разности в остальных старших разрядах осуществляется аналогичным образом. Двоичный код разности фиксируется в регистре . Процесс вычислений занимает время перезаписи всех разрядов уменьшаемого, начиная с млсщшего разряда, с выхода регистра 1 на его вход,т.е один цикл. Если уменьшаемое меньше вычитаемого, то разность получается в дополнительном коде. Пример . Требуется вычислить разность 2 у - X. 1000100111 1101110010 01010 0000 0000000101 OlOlOlOlOl 1111100000 1010110101

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1979 |

|

SU851403A1 |

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| Генератор двоичных чисел | 1981 |

|

SU1062674A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для вычитания | 1982 |

|

SU1083183A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| Преобразователь двоичного кода в код с весовыми коэффициентами 1 и -1 и обратно | 1981 |

|

SU1007097A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

Авторы

Даты

1980-12-23—Публикация

1979-02-26—Подача