Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры накапливающего типа (далее - объект), см., например, книгу М.А.Карцев. Арифметика цифровых машин. М.: Наука 1969, стр.247-252, а также двоичный накапливающий сумматор по а.с. SU 1112363А. Недостатком объекта является наличие в каждом разряде трех RS-триггеров и выполнение только одной операции - сложения.

Наиболее близким, принятым за прототип, является накапливающий сумматор по а.с. SU 1176323 A.

Прототип выполнен на основе только двух триггерных регистров, выполняет одну операцию сложения кодов, но может работать только при определенном, строго ограниченном времени распространения сигнала сквозного переноса. Другими словами, устройство работоспособно при Тсп=2nτ≤tи, - здесь Тсп - время сквозного переноса; τ - время задержки сигнала на одном логическом элементе (ЛЭ) И (ИЛИ); n - число двоичных разрядов объекта; tи - длительность исполнительного импульса, равная времени гашения переносов.

Из этого следует, что при увеличении Тсп следует увеличивать время гашения переносов, т.е. снижать быстродействие работы объекта. Вторым недостатком прототипа является ограниченный перечень выполняемых операций.

Задачей изобретения является устранение указанных недостатков. Для этого предложен объект, содержащий в каждом разряде первый и второй RS-триггеры, восемь элементов И, три элемента ИЛИ, один элемент НЕ и семь шин управления, причем входы первого элемента И соединены с шиной управления первым сложением по модулю два и с входной шиной сумматора, входы второго элемента И соединены с шиной управления сложением по модулю два инверсного кода второго слагаемого и выходом первого элемента НЕ, вход которого соединен с входной шиной сумматора, выходы первого и второго элементов И подключены к входам первого элемента ИЛИ; входы третьего элемента И соединены с шиной управления вторым сложением по модулю два и с шиной переноса из младшего разряда, выход третьего элемента И соединен с входом второго элемента ИЛИ, выход которого соединен с первыми входами четвертого и пятого элементов И. вторые входы этих элементов И связаны с единичным и нулевым выходами второго триггера соответственно, а выходы упомянутых элементов И подключены к нулевому и единичному входам первого триггера, выходы первого триггера соединены с первыми входами шестого и седьмого элементов И, его вторые входы подключены к шине управления пересылкой кода из первого триггера во второй, выходы шестого и седьмого элементов И соединены с нулевым и единичным входами второго триггера соответственно, выход седьмого элемента И и единичный выход второго триггера соединены с первым и вторым входами третьего элемента ИЛИ, кроме того, нулевые входы первого и второго триггеров подключены к шинам установки нуля этих триггеров, отличающийся тем, что сумматор в каждом разряде содержит четвертый элемент ИЛИ и восьмую шину гашения переносов, при этом выход первого элемента ИЛИ соединен со вторым входом второго элемента ИЛИ и с третьим входом третьего элемента ИЛИ, выход которого соединен с первым входом восьмого элемента И, нулевой вход первого триггера связан с первым входом четвертого элемента ИЛИ, второй вход этого элемента соединен с выходом восьмого элемента И, а третий вход четвертого элемента ИЛИ соединен с шиной переноса из младшего разряда, выход четвертого элемента ИЛИ подключен к второму входу восьмого элемента И, восьмая шина управления переносом соединена с третьим входом восьмого элемента И.

Кроме того, введены:

- девятая шина управления сдвигом кода влево, подключенная к четвертому входу четвертого элемента ИЛИ (п.2 формулы изобретения);

- девятый элемент И и десятая шина управления, которая подключена к первому входу упомянутого элемента, второй вход связан с выходом восьмого элемента И первого старшего разряда, а его выход подключен к третьему входу второго элемента ИЛИ (п.3);

- пятый элемент ИЛИ, первый вход которого подключен к выходу седьмого элемента И, ко второму входу упомянутого элемента ИЛИ подключена введенная одиннадцатая шина управления, а выход шестого элемента ИЛИ соединен с единичным входом второго триггера (п.4).

Отметим основные отличительные признаки объекта и покажем, что позволяет получить каждый из признаков.

1. Соединение выхода первого элемента ИЛИ через третий элемент ИЛИ с входом восьмого элемента И обеспечивает формирование сигнала переноса при переключении триггера 1 из "единицы" в "нуль", а также при наличии сигнала переноса, поступившего по шине 19, во время tи, т.е. в разряде будет сформирован сигнал переноса одновременно с выполнением ЭО приема второго слагаемого и сложения по модулю два.

2. Соединение выхода восьмого элемента И с входом четвертого элемента ИЛИ обеспечивает "хранение" переноса во время второго и третьего временных тактов.

3. Подключение восьмой шины к входу восьмого элемента И разрешает его работу во время t1, t2 и t3 временных тактов.

Указанные отличия объекта (1, 2, 3) повышают быстродействие работы и позволяют исключить из состава оборудования третий триггерный регистр.

4. Подключение девятой шины к входу четвертого элемента ИЛИ обеспечивает выполнение операции сдвига влево.

5. Подключение выхода восьмого элемента И к входу девятого элемента И младшего разряда обеспечивает сдвиг кода вправо.

6. Подключение одиннадцатой шины управления через пятый элемент ИЛИ к "единичному" входу второго триггера позволяет выполнить операцию логического умножения.

Указанные отличия объекта (4, 5, 6) расширяют перечень выполняемых операций.

Предлагаемый объект позволяет построить сумматор накапливающего типа на основе трех ЛЭ - И, ИЛИ, НЕ, его схема формирования и распространения сигнала переноса обеспечивает повышение быстродействия работы устройства, расширяется перечень выполняемых арифметических и логических операций (вычитание, сдвиг влево, сдвиг вправо, логическое сложение, логическое умножение и инвертирование кода) практически без дополнительных затрат оборудования.

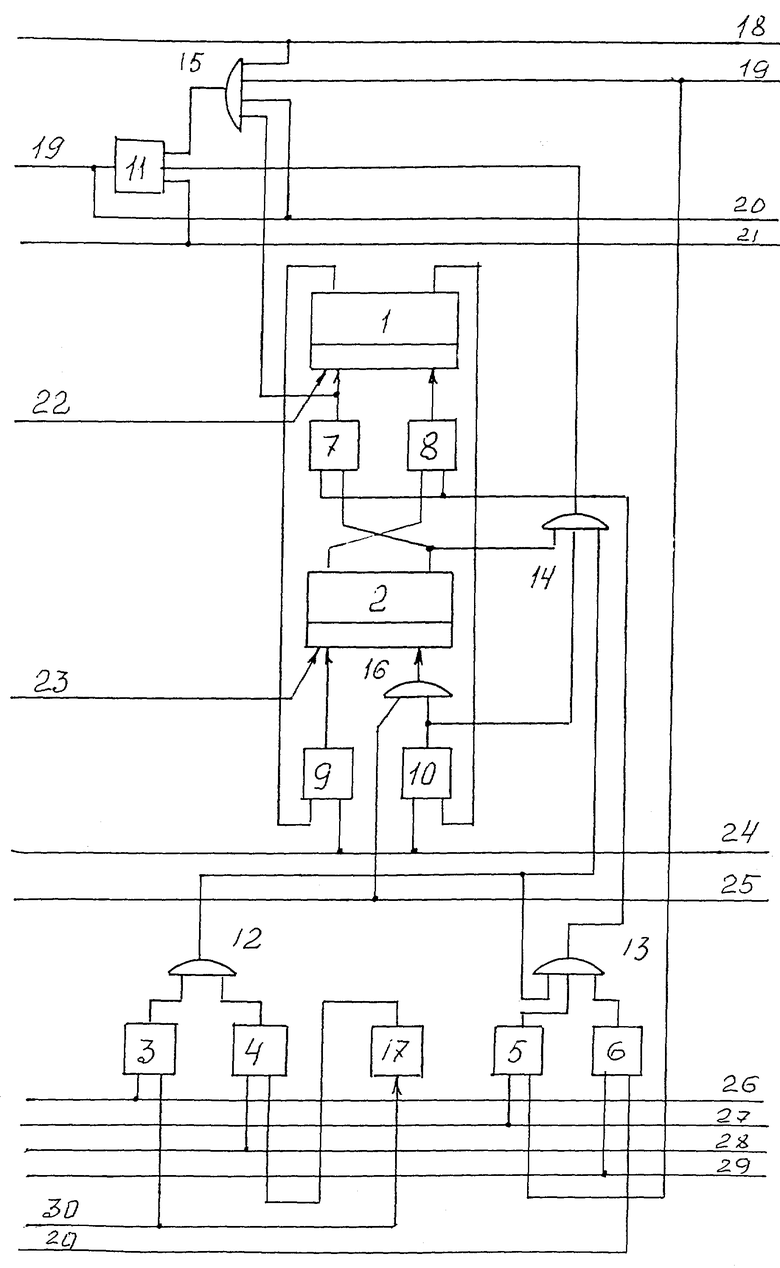

Для пояснения работы предлагаемого объекта на чертеже приведена функциональная схема одного двоичного разряда сумматора. Каждый разряд объекта содержит RS-триггеры 1 и 2, элементы ИЗ-11, элементы ИЛИ 12-16, элемент НЕ 17, шину управления сдвигом влево 18, шину переноса из младшего разряда 19, шину гашения переносов 21, шины установки нуля триггеров 22 и 23, шину пересылки кода из первого триггера во второй 24, шину приема единицы во второй триггер 25, шину приема прямого кода 26, шину управления вторым сложением по модулю два 27, шину приема обратного кода 28, шину сдвига кода вправо 29, входную шину приема кода в данный разряд 30.

1. Рассмотрим работу объекта при выполнении операции сложения двух чисел, представленных в двоичном коде. Будем считать, что код первого слагаемого хранится в триггерах 1 и 2, а код второго слагаемого поступает в сумматор по шинам 30.

По первому временному такту (t1) выполняется одновременно элементарные операции (ЭО) приема второго слагаемого, сложения по модулю два (первого), формирование и запоминание потенциала переноса в цепи сквозного переноса данного разряда. Для выполнения этих ЭО на шину 26 подается исполнительный импульс, на шину 21 подается потенциал разрешения прохождения сигнала переноса. Если на шине 30 имеется сигнал, соответствующий коду "1", то исполнительный импульс по цепи ЛЭ И 3, ИЛИ 12, 14 поступит на первый вход И 11. Одновременно этот импульс по цепи ИЛИ 13 поступит на первые входы ЛЭ 7, 8 и, если в триггере 2 хранится код "1", установит триггер 1 в "0". Одновременно сигнал с выхода И7 поступит на первый вход ИЛИ 15 и, далее, на второй вход И 11. Так как на трех входах И 11 присутствуют сигналы, по шине 19 в старший разряд будет поступать сигнал переноса. За счет связи выхода И 11 с входом ИЛИ 15 этот сигнал будет "храниться" до конца операции сложения.

По второму временному такту (t2) выполняется ЭО пересылки кода триггера 1 в триггер 2. Для этого на шину 24 поступает исполнительный импульс. Одновременно продолжается распространение сигнала переноса в сторону старших разрядов.

По третьему временному такту (t3) выполняется ЭО сложения по модулю два (вторая). Исполнительный импульс поступает на шину 27 и, если в рассматриваемый разряд по шине 19 поступил потенциал переноса из младшего разряда, по цепи И 5, ИЛИ 13 поступит на входы И 7, 8 и проинвертирует код триггера 1. На этом операция сложения завершается. Результат суммирования будет храниться в триггерах 1.

По четвертому временному такту (t4) выполняются ЭО пересылки кода триггера 1 в триггер 2 (вторая) и гашение сигналов переносов, сформированных по t1 и t2. Операция второй пересылки выполняется аналогично первой пересылке. Элементарная операция гашения переносов выполняется за счет снятия разрешающего сигнала, присутствующего на шине 21 во время t1, t2 и t3. При этом во всех разрядах одновременно будут устранены сигналы переносов. По истечении t4 объект будет подготовлен для выполнения следующей операции сложения или других операций.

2. Операция вычитания выполняется аналогично выполнению сложения. Отличие состоит в том, что по t1 прием второго слагаемого производится инверсным кодом. Исполнительный импульс проходит по цепи И 4, ИЛИ 12,13 на входы И 7, 8.

3. Элементарная операция сдвига кода влево выполняется за три временных такта t1, t2 и t3. Код числа хранится в триггерах 1 и 2. По t1 на шину 18 подается исполнительный импульс, который через ИЛИ 15 поступает на вход И 11. На второй вход И 11 поступает сигнал "1" с выхода триггера 2, через элемент ИЛИ 14. На выходе И 11 будет сформирован и будет хранится до конца выполнения операции потенциал переноса, который по шине 19 поступит на вход И5 старшего разряда.

По t2 на шины 22 и 23 подаются импульсы установки триггеров 1 и 2 в нулевое состояние.

По t3 на шину 27 подается исполнительный импульс, который по цепи И 5, ИЛИ 13, И 8 поступит на "единичный" вход триггера 1. Таким образом, код числа будет сдвинут влево на один разряд. (Для выполнения этой ЭО потребуется увеличить оборудования предлагаемого объекта на один вход ЛЭ ИЛИ и одну шину управления).

4. Элементарная операция сдвига кода вправо выполняется аналогично ЭО сдвига влево (t1 и t2). По t3 на шину 29 подается исполнительный импульс, который по цепи И 6, ИЛИ 13, И 8 поступит на единичный вход триггера 1. Таким образом, код числа, хранящийся в триггерах 1, будет сдвинут на один разряд вправо. (Для выполнения этой ЭО потребуется увеличить оборудование объекта на три входа ЛЭ И, ИЛИ и одну шину управления).

5. Элементарная операция инвертирования кода, хранящегося в триггерах 1, выполняется за два такта. По t1 на шину 28 подается исполнительный импульс. Так как прием числа не производится, то с выхода НЕ 17 на вход И 4 поступает высокий потенциал, разрешающий прохождение импульса по цепи И 4, ИЛИ 12, 13 на И 7, на "нулевой" вход триггера 1, если в триггере 2 хранится "1", и через И 8 на "единичный" вход триггера 1, если в триггере 2 хранится код "0". По t2 выполняется ЭО пересылки кода из регистра 1 в регистр 2 и гашение потенциалов переноса во всех разрядах объекта. (Для выполнения этой ЭО не требуется увеличения оборудования).

6. Аналогичным образом выполняется ЭО сложения кодов по модулю 2. Отличие состоит в том, что исполнительный импульс подается на шину 26, а код второго слагаемого поступает по шине 30.

7. Операция логического сложения выполняется за три такта. По t1 на шину 23 подается импульс установки триггера 2 в "нуль". По t2 принимается код второго слагаемого. Если на шине 30 присутствует высокий потенциал, соответствующий коду "1", то исполнительный импульс по цепи И 3, И 12, 13, И 8 поступит на "единичный" вход триггера 1. (Для выполнения этой ЭО не требуется дополнительного оборудования). По t3 выполняется ЭО пересылки кода и гашения переносов.

8. Операция логического умножения выполняется за три такта. По t1 на шину 25 подается исполнительный импульс, поступающий через ИЛИ 16 на "единичный" вход триггера 2. По t2 принимается инверсный код второго сомножителя. Исполнительный импульс подается на шину 28, который проходит по цепи И 4, ИЛИ 12, 13, И 7 на "нулевой" вход триггера 1, если инверсное значение второго сомножителя в данном разряде равно "1". Таким образом, будет выполнена операция логического умножения. (Для ее выполнения требуется увеличить оборудование устройства на два входа элемента ИЛИ). По t3 выполняется ЭО пересылки кода и гашение переносов.

Таким образом, предлагаемый объект обеспечивает повышение быстродействия выполнения операций сложения (вычитания) и расширяет перечень выполняемых объектом операций в четыре раза при одинаковых затратах аппаратурных средств.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия, расширение перечня выполняемых арифметических и логических операций. Указанный результат достигается за счет того, что сумматор содержит два RS-триггера, девять элементов И, пять элементов ИЛИ, элемент НЕ, десять шин управления. Сумматор выполняет операции сложения (вычитания), операции сдвига кода влево и вправо, инвертирование, сложение по модулю два, логическое сложение и логическое умножение. 2 з.п. ф-лы, 1 ил.

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

Авторы

Даты

2006-01-27—Публикация

2003-11-24—Подача