(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВА/ АТНСГО КСРНЯ ИЗ СУММЫ КВАДРАТОВ ДВУХ ЧИСЕЛ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1129610A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| Цифровой вольтметр | 1985 |

|

SU1337791A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1238064A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU922735A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ И РАЗНОСТИ ЧАСТОТ СИГНАЛОВ | 1992 |

|

RU2025738C1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1984 |

|

SU1238065A1 |

- . 1 ,

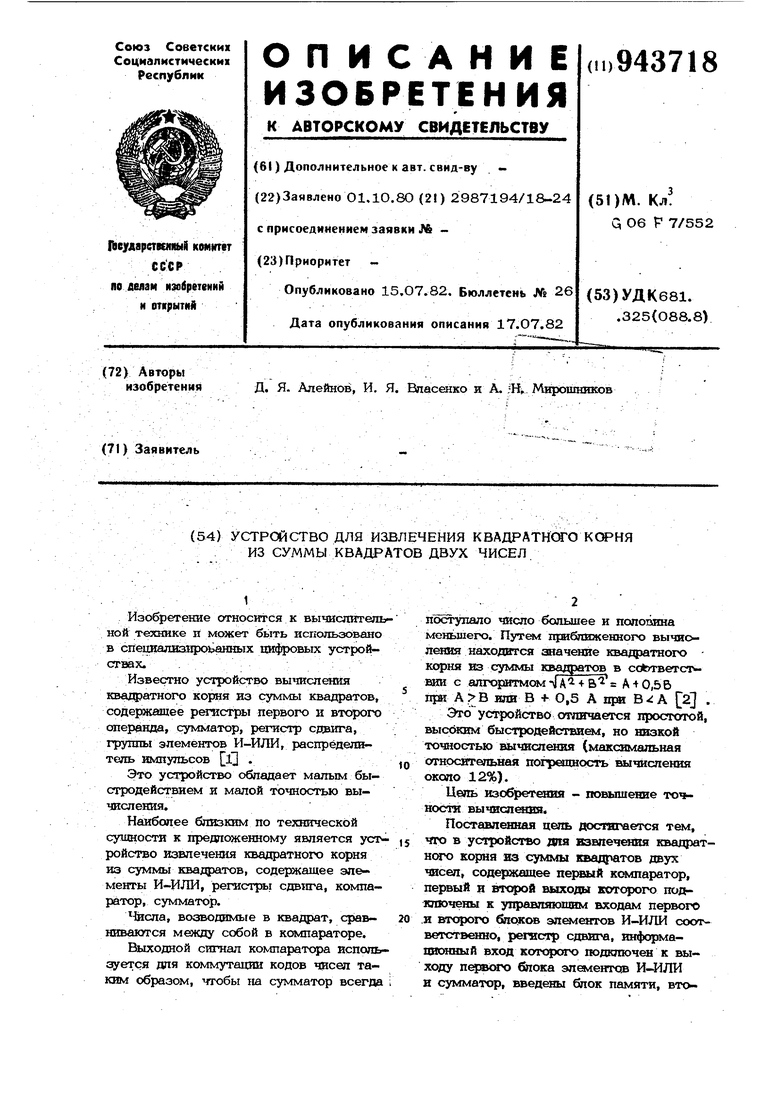

Изобретение относится к вычислительной технике и может быть использовано в специалнз фоьанных шяфровых устройствах.

Известно устройство вычислетш ква/фатного корня из суммы квадратов, содержащее регистры первого и второго операнда, сумматор, регистр сдвига, грухшы элементов И-ИЛИ, распределитель импуттьсов i .

Это устройство обладает малым быстродействием я малой точностью вычисления.

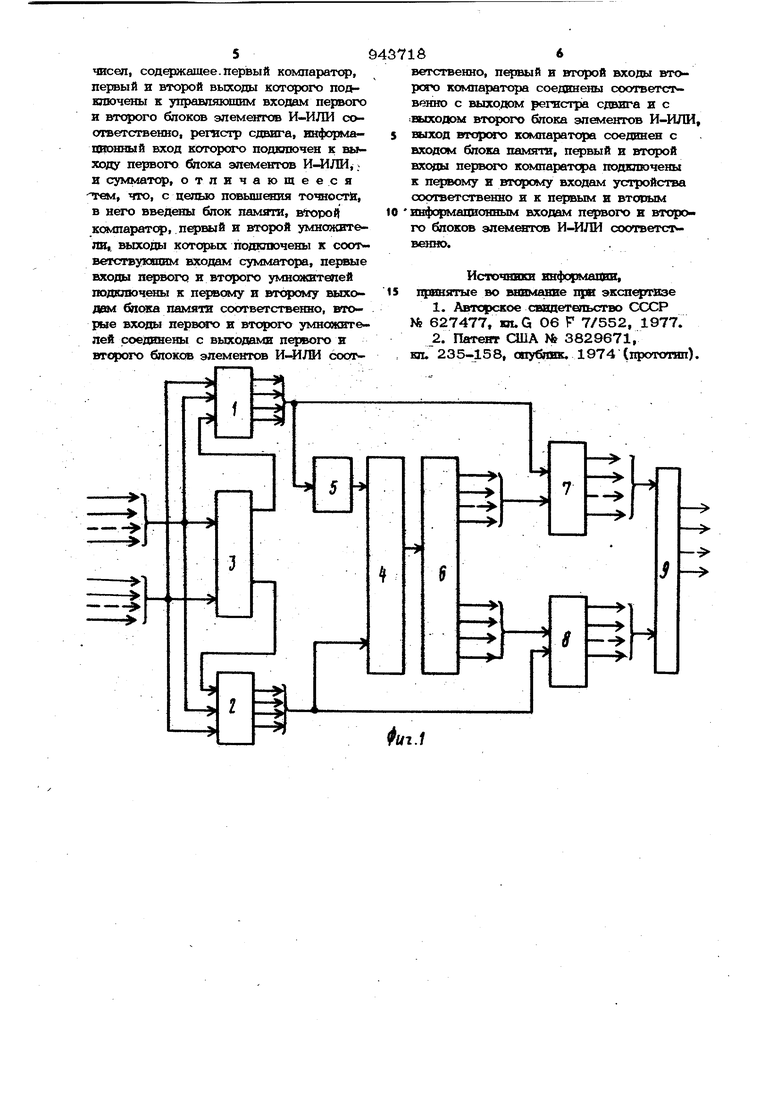

Наиболее близким по технической сугцности к предложенному является устройство извлечения квадратного корня из суммы квадратов, содержащее элементы И-ИЛИ, регистрь сдвига, компаратор, сумматор.

feaia, возводимьге в квадрат, сравниваются между собой в компараторе.

Выходной сигнал KOMnapaTqpa используется для коммутации кодов чисел таким образом, чтобы на сумматор всегда ;

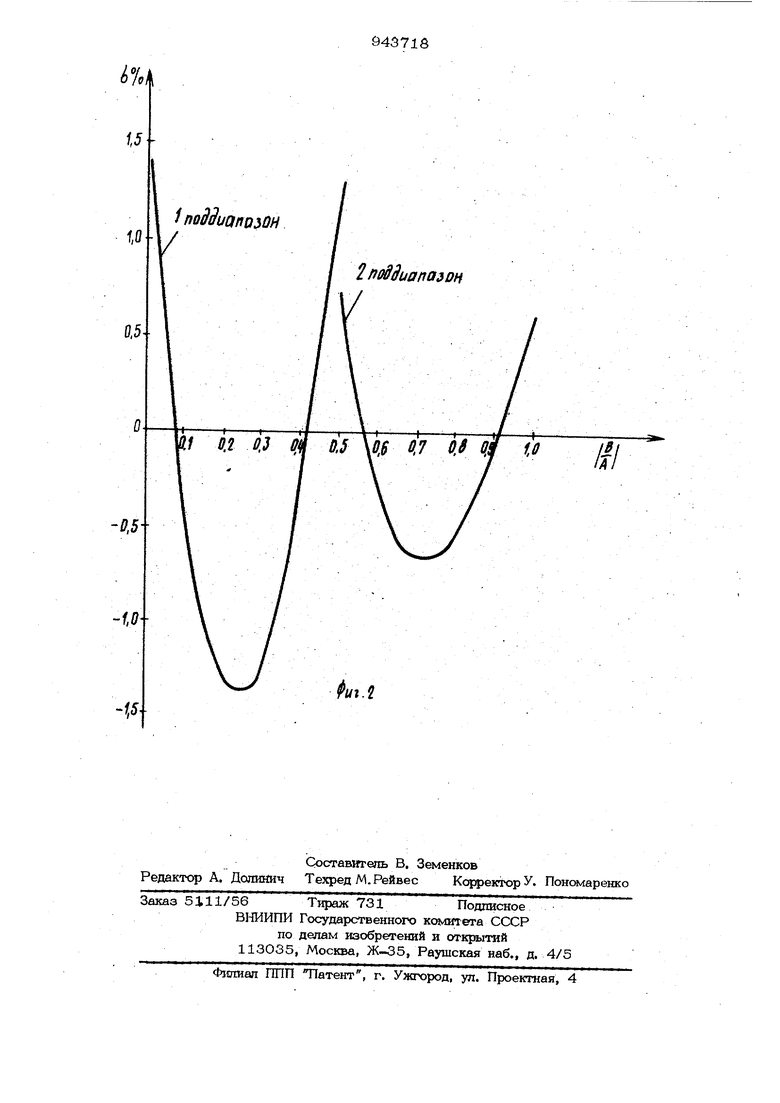

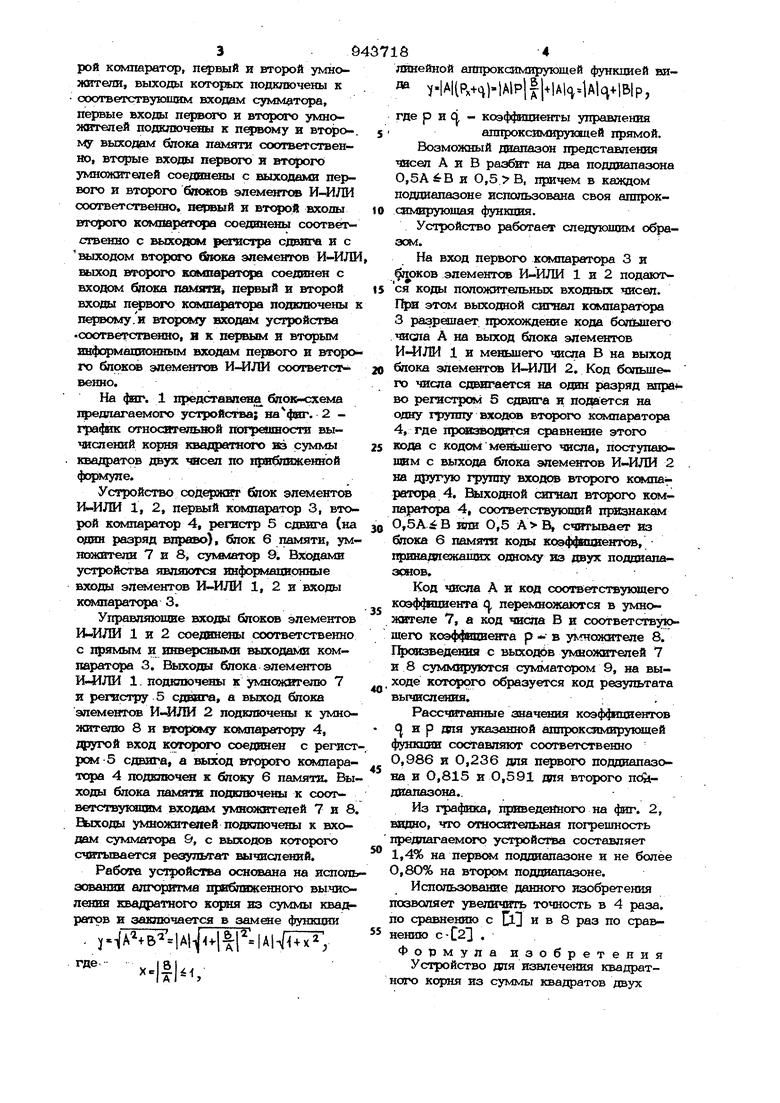

поступало число большее и половина меньшего. Путем пргаблнженного вычиоленяя находится оиаченне квадратного корня из суммы квадратов в соЬтветст вии с алгоритмом А при А или В 4- 0,5 А при В А 2 . Это устройство отпнчается простотой, выомсим быстродействием, но низкой точностью вычотслення (максимальная

Q относительная погрецность вычисления около 12%).

Цепь изр ретення - повышение точности вычисления.

Поставлешшя цель достигается тем,

15 ЯГО в устройство для взвпеч ош квадраткаго корня из суммы квадратов двух чисел, содержащее переый компаратор, первый и второй выходы которого поохлючены к управляющим входам первого

чисел, содержащее. nepJBbift компаратсф, первый я второй выходы которого подключены к управшпсшим входам первого и второго блоков элементов И-ИЛИ соответственно, регистр сдвига, внфо|Ж1ашгонный вход которого подюпочен к ш 1ходу перво1х блока элементов И-ИЛИ,; и сумматор, отличающееся -тем, что, с целью псявышеяия точности, в него введены блок памяти, кс отаратор, первый и второй умножители,, выходы подключены к соответствующим входам сумматора, первые Екоды и второго умножитепей подкпючень к первому и второму выходом басха памяти соответственно, вторые входы первого и умноокнтелей соединены с выходами первого и второго блоков элементов И-ИЛИ схх ветственно, первый н второй входы втореях компаратора соещнены соответственно с выходом регистра сдвига и с выходом втсфого блока элементов И-ИЛИ выход второго компаратора соединен с кзазаам блока памяти, первый и второй входы первсях) компаратора подключены к первому и второму входам устройства соответственно и к первым и втопым информационным входам первого и второго блоков элементов И-ИЛИ соответст венно.

Источники информафи, щ ИН5Ггые во внимсшие щя экспертизе

кп. 235-158, опубпик. 1974 (прототип).

f 0.2 ff.3 т 0.5

2ni duanasDH

If

hi.1

Авторы

Даты

1982-07-15—Публикация

1980-10-01—Подача