Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специали зированньЬс вычислителях.

Цель изобретения - повышение быстродействия вычислений за счет устранения влияния количества значащих разрядов аргумента на время вычисления и повьшение точности за счет нормирования аргументов.

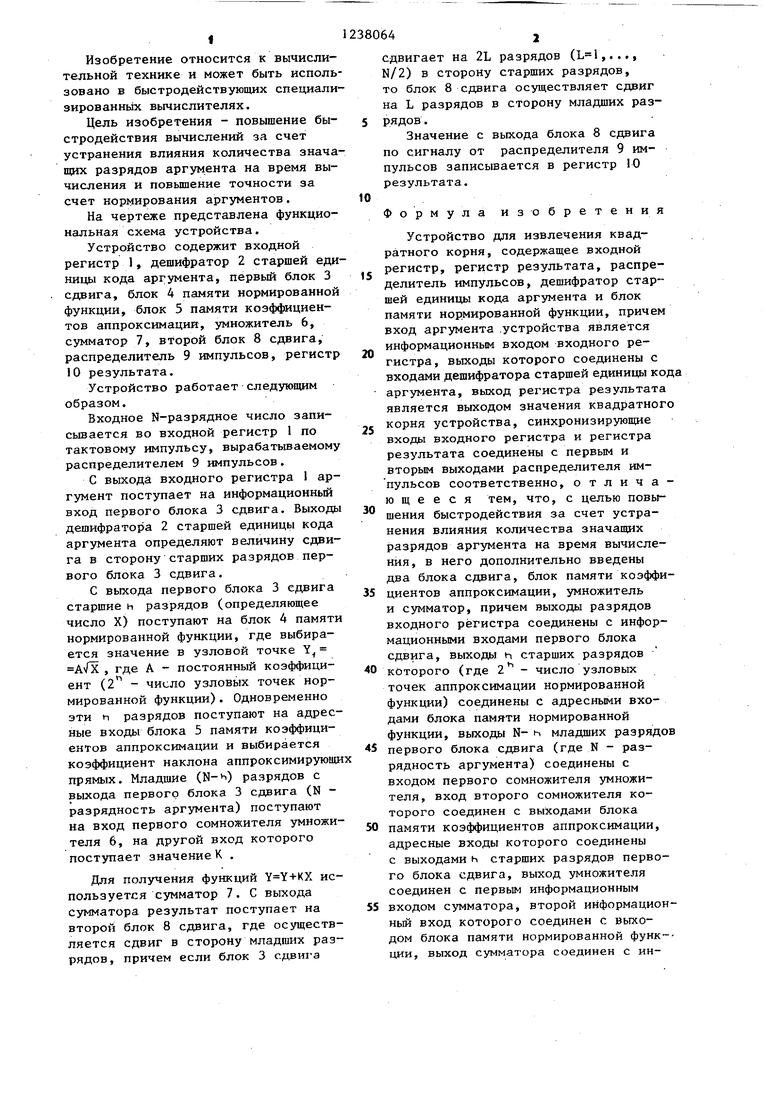

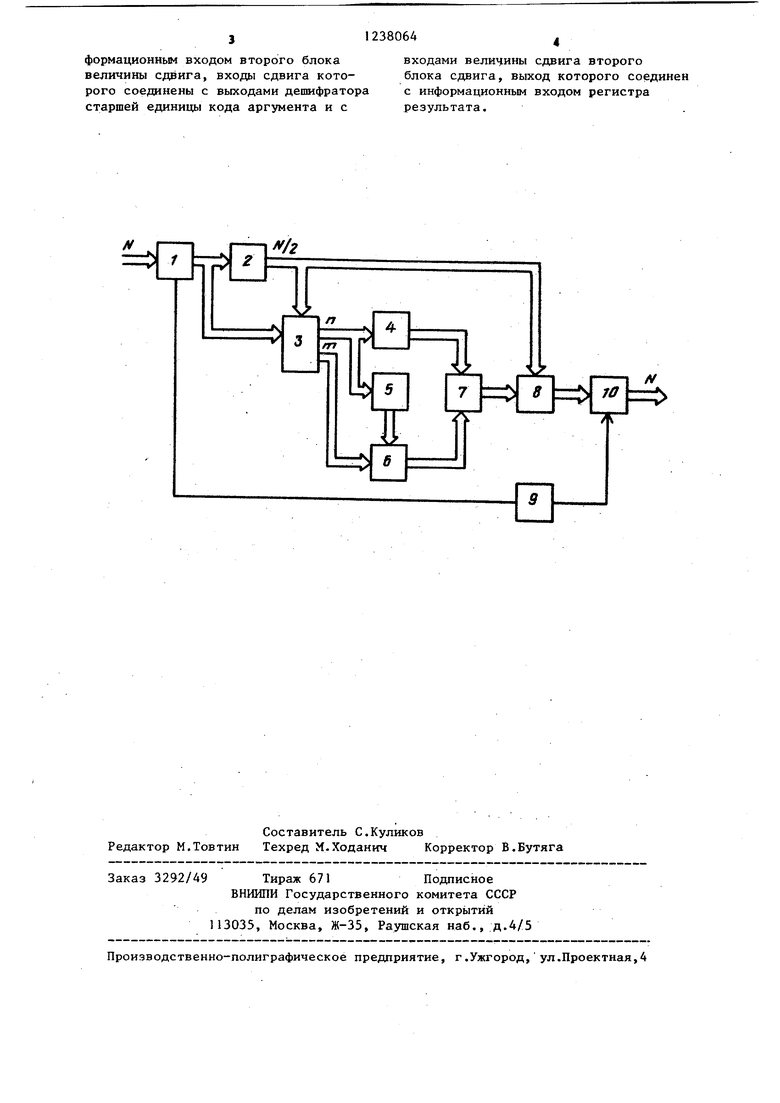

На чертеже представлена функциональная схема устройства.

Устройство содержит входной регистр 1, дешифратор 2 старшей еди нищ) кода аргумента, первьй блок 3 сдвига, блок 4 памяти нормированной функции, блок 5 памяти коэффициентов аппроксимации, умножитель 6, сумматор 7, второй блок 8 сдвига, распределитель 9 импульсов, регистр 10 результата.

Устройство работает следующим образом.

Входное N-разрядное число записывается во входной регистр 1 по тактовому импульсу, вырабатьшаемому распределителем 9 импульсов.

С выхода входного регистра 1 аргумент поступает на информационный вход первого блока 3 сдвига. Выхода дешифратора 2 старшей единицы кода аргумента определяют величину сдвига в сторону старших разрядов первого блока 3 сдвига.

С выхода первого блока 3 сдвига старшие и разрядов (определяющее число X) поступают на блок 4 памяти нормированной функции, где выбирается значение в узловой точке Y , где А - постоянный коэффициент (2 - число узловых точек нормированной функции). Одновременно эти и разрядов поступают на адресные входы блока 5 памяти коэффициентов аппроксимации и выбирается коэффициент наклона аппроксимирующи прямых. Младшие (N-ь) разрядов с выхода первого блока 3 сдвига (N - разрядность аргумента) поступают на вход первого сомножителя умножителя 6, на другой вход которого поступает значение К .

Для получения функций используется сумматор 7. С выхода сумматора результат поступает на второй блок 8 сдвига, где осуществляется сдвиг в сторону младших разрядов, причем если блок 3 сдвига

0

сдвигает на 2L разрядов (,..,, N/2) в сторону старших разрядов, то блок 8 сдвига осуществляет сдвиг на L разрядов в сторону младших раз5 рядов.

Значение с выхода блока 8 сдвига по сигналу от распределителя 9 импульсов записывается в регистр 10 результата.

0

Формула изобретения

Устройство для извлечения квадратного корня, содержащее входной регистр, регистр результата, распределитель импульсов, дешифратор старшей единицы кода аргумента и блок памяти нормированной функции, причем вход аргумента .устройства является информационным входом входного регистра, выходы которого соединены с входами дешифратора старшей единицы кода аргумента, выход регистра результата

является выходом значения квадратного , корня устройства, синхронизирующие входы входного регистра и регистра результата соединены с первым и вторым выходами распределителя импульсов соответственно, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия за счет устранения влияния количества значащих разрядов аргумента на время вычисления, в него дополнительно введены два блока сдвига, блок памяти коэффи- 5 циентов аппроксимации, умножитель и сумматор, причем выходы разрядов входного регистра соединены с информационными входами первого блока сдвига, выходы i- старших разрядов 0 которого (где 2 - число узловых точек аппроксимации нормированной функции) соединены с адресными входами блока памяти нормированной функции, выходы N- ь младших разрядов 5 первого блока сдвига (где N - разрядность аргумента) соединены с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходами блока памяти коэффициентов аппроксимации, адресные входы которого соединены с выходами h старших разрядов первого блока сдвига, выход умножителя соединен с первым информационным 5 входом сумматора, второй информационный вход которого соединен с выходом блока памяти нормированной ции, выход сумматора соединен с ин0

формационным входом второго блока величины сдвига, входы сдвига которого соединены с выходами дешифратора старшей единицы кода аргумента и с

входами величины сдвига второго блока сдвига, выход которого соединен с информационным входом регистра результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для извлечения корня | 1988 |

|

SU1508209A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для вычисления функции табличным методом | 1986 |

|

SU1383337A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных вычислителях, радиотехнических устройствах и аппаратуре передачи дан-, ных, когда предъявляются требования к быстродействию вычислений при простоте реализации. Целью изобретения является повьппение быстродействия и точности за счет параллельной процедуры выполнения всех операций и введения нормирования входных чисел. В результате этого устраняется зависимость времени вычисления от разрядности входных чисел. Входное число поступает на дешифратор старшей единицы кода аргумента, который управляет процедурой нормирования аргумента в первом блоке сдвига. Блоки памяти нормированной функции, коэффициентов аппроксимации служат для получения величин, необходимых для вычисления умножителя и сумматора аппроксимирующей функции. Значение результата нормируется в обратную сторону во втором блоке сдвига и записывается в регистр результата с помощью распределителя импульсов 1 ил. I (П IN9 оо 00 о 2

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1986-06-15—Публикация

1984-11-19—Подача