1

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления.

Известно микропрограммное устройство управления, содержащее дешифратор микрокоманд, регистр микрокоманд, блок памяти микрокоманд, регистр адреса, дешифратор адреса, элементы И, НЕ, схемы задержки, генератор тактовых импульсов l.

Однако данное устройство обладает недостаточным быстродействием.

Наиболее близким к данному изобретению является микропрограммноеустройство управления, содержащее дешифратор микрокоманд, выходы которого являются выходами устройства, элемент И условий перехода, группу триггеров переходов, .регистр микрокоманд, регистр адреса, дешифратор адреса, блок памяти микрокоманд, формирователь адреса перехода, генератор тактовых импульсов, выходом подключенный к управляющему входу дешифратора адреса, выход которого поДгключен к адресному входу блока памяти микрокоманд, информационным выходом соединенного с информационным входом регистра микрокоманд, аервый информационный выход которого соединен с информационным входом дешифратора микрокоманд, второй информационный выход регистра микрокоманд соединен с первыми входами формирователя адреса пере,д хода и регистра адреса, выходом соединенного с адресным входом дешифратора аареса, выход формирователя адреса перехода соединен со вторым входом регистра адреса, второй вход формирователя

,5 адреса перехода соединен с выходом эле мента И условий перехода, первый вход которого соединен с одним из выходов дешифратора микрокоманд, а второй - с выходами группы триггеров переходов

20 2.

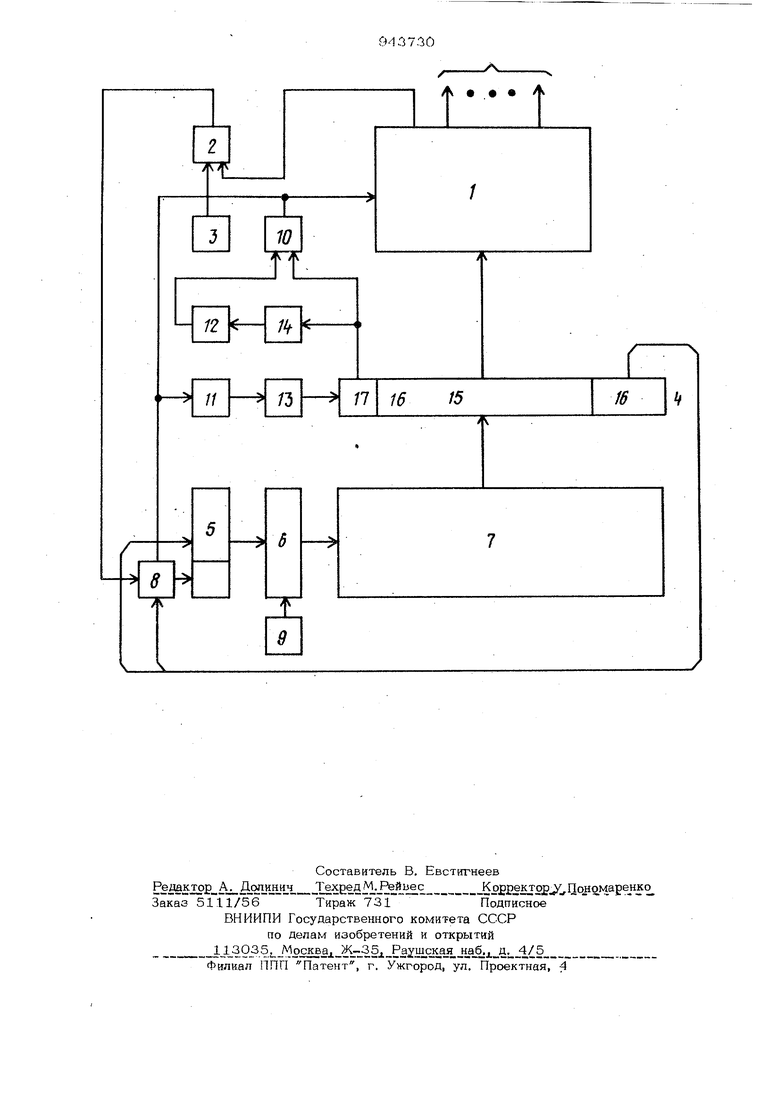

Недостатком этого устройства являются малые функциональные возможности, о феделяемые различной разрядностью информационных и управляющих слов. Цепь изобретенкя - расшкрение функциональных возможностей за счет унификации длины информационных и управляющих слов. Поставленная цель достигается тем, что устройство содержит элемент И блокировки, первый и второй элементы НЕ, первый ивторой элементы задержки, выход элемента И блокировки соединен с управляющим входом деши(|фатора микрокоманд, с третьим входом формирователя адреса перехода и со входом первой схе мы задержки, выход которой через первы элемент НЕ соединен с управляющем входом регистра микрокоманд, третий выход которого соединен с первым входо элемента И блокировки и со входом второго элемента задержки, выход которого через втсфой элемент НЕ соединен со вторым входом элемента И блокировки, На чертеж е представлена бЛ(Ж-сэсема устройства. Устройство содержат дешифратсф микрокоманд 1, элемент И условий .перехода 2, группу триггеров переходов 3, регистр мвокрокоманд 4, регистр адреса 5, деши( адреса 6, блок памяти микрокоманд 7, формирователь адреса перехода 8, генератор тактовых импульсов 9, элемент И блокировки 10, первый элемент задержки 11, второй элемент задержки 12, первый элемент НЕ 13, второй НЕ 14. Устрсйство работает следующим образом. В соответствии с адресом, оформированным на регистре 5 и сигналом на соответствующем этому адресу выходе дешВ(}атора 6, в моменты времени, оареаепяеыялм генератором 9, из блока памятк мясрокоманд 7 считывается очередная микр(жомандв на регистр мшсрокоманд 4. Последний содержит операдвон вые попя 15, адресное поле 16, я специальный 17, единичное значение когароиго указывает микрокоманду считывания константы из блока 7. При всех другвх макрокомандах значение это го рааряш равно нулю и дальнейшая работа устройства в этом случае заключается в следующем. На выходе деиШфра тора 1 вырабатываются один или несколь ко элемеятартых микроопераций в соответствии с кодом микрокоманд. Одновременно с выполнением этих микроопераций с перво1Ч1 выхода регистра макрокоманд 4 код следующей микрокоманды поступает и запоминается на регистре 5. 9 04 Условные переходы в устройстве осуществляются следующим образом. Если в каком-либо поле регистра 4 записан код анализа одного или нескольких триггеров переходов 3, вырабатывающих признаки условий, то сигнал элементарной операции, соответствующий этому коду, анализирует это состояние, поступая на первый вход элемента И 2 условий перехода, на второй вход которого подаются сигнал с выхода анализируемых триггеров 3. Сигнал, вырабатываемый на выходе элемента И 2 при определенном состо1гаии указанных выше триггеров, через формирователь адреса перехода 8 меняет состояние определенных раз{шдов регистра адреса 5. При наличии признака микрркоманды считывания константы и блока памяти микрокоманд 7, т.е. единицы в специальном разряде 17 регистра 4, микрокоманда отрабатывается в течении двух циклов обрац(Ш1ия к бло1о 7 (первый цикл - чтение микрокоманды, второй . цикл - чтение кагстантыЬ В первом цикле после чтения микрокоманды происходит блокирование дешифратора 1 и фсфмирование адреса константы. Выходы деши|} тора 1 блокируются tiyTGM подачи на его управляющий вход сигнала блсжировки с выхода элемента И 1О. Через задержки 11 и элемент НЕ 13 к конау первого цикла на управляющий вход регистра микрсжоманд 4 подается сигнал блсжировки. Для формирования адреса константы единичный код третьегр вьосош регистра микрокоманд через элемент И Ю вместе с кодом со втефого выхода регистра а/фёса 4 подается на формирою1тель адреса перехода 8, а затем сфоршфовашый адрес запоминается Hia регистре 5. Адрес ксжстанты при этом может фсфмвр(жаться путем дизъюнкции сигналов первого выхода регистра адреса 4 с сигналов третьего выхода регистра а%эеса.4. Во втором цикле происходит чтение кжстанты и отработка принятой в первом дикле микрокоманды. Шгя этого в начапе втсфого цикла сигнал с третьего выхода регисфа ечзреса 4 через схему задержки 14 в элемент НЕ 12 поступает на вход элемента И 10, сигнал с выхода которого разблсжирует дешифратор 1 и задерживается схемой задержки 11 на время, необходимое для чтения константы. С блока памяти считывается константа. Спустя время задержки на схеме задержкн 11 снимается блокировка со входа регистра 4 и схема 11 готова к приему следующей микрокоманды. На регистре 5 при этом формируется адрес по коду, соответствующему второму выходу регист-.$ ра 4 элемента И Ю, так как на вькок, а следовательно, на входе формирователя, адреса перехода 8 устанавливается потен цнал нуля.

Суммарные затраты времени на микро- команды « {ктывания констант, определяемое тем, что («и выполняются за два цикла блсжа памяти микрсжоманд незначв телыш, так как их количество в реальных микропрограммах, как правило, невелико.

/Формула изобретения

ЛЗикропроГраммное устройство управле-кия, содержащее дешифратор микроосоманд, выходы которого являются вьосошмв уст-: рсАства, элемент Иусаовий перехода, группу триггеров переходов, peractp м)а(жса«анд регистр адреса, дешифратор Адреса, блок Памяти микрокси анд форь сирователь адреса перехода, генератор тактдЫлс нмпупьсов, выхо1и м подключенный к управляюо ыу входу дешифратора аарвса, выход которого подкл зя|ен к адресному вкову памяти мнкрокомашаи вяформашпжным соединенного с нвформацношшм JBxojEloM регистра MtucpoKc faim, первый /внформаиисннкй вькод которого соединея с информациоввым жодом дешифратора Микрокоманд, второй информацвсяный ыд- 3$ ход р встра ми1фсжрманд соединен с первыми входами формирователя адреса перехода и регистра адреса, выходом сое диненным с адресным входом дешифратора, адреса, выход формирователя адресе перехода соединен с вторым входом регистра адреса, второй вход формирователя адреса перехода соединен с выходом элемента И условий перехода, первый вход кото|х го соединен с одним из выходов дешифратора микрсжоманд, а второй - с выходами группы триггеров переходе, отличающееся тем, что с целью {ясшврения функцисшальных возможностей за счет унификации длины инфефмадвонньк н управляющих сл(Ю, устройство содержит элемент И блокироыси, первый и второй элементы НЕ, первый и второй элементы задеряки, вызим элемента И блокировки соедсшен с управляющим входом деш ратора микрокоманд, с третьим входом ф(Ч мирователя адреса перехода и с входом элемента задврж1СИ, выход которого через пе{жый элемент НЕ соешгнен с управляющим входом регистра мищхжоманд, третий выход которого соединен с aeftaUM входом элемента И блоквровки в с входом второго элемента , выход которого через второ элемент НЕ соедини с вторым входом элемента И блокировки.

Источники шффмации, принятые во внвманне при экспертизе .

1.Авторское свидетельство СССР № 331387, кл. G Об F 9/16, 1972.

2.Авторское свидетельство СССР № 2912О1, кл. Q 06 Р 9/16, 1971 (прототво).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Авторы

Даты

1982-07-15—Публикация

1975-04-14—Подача