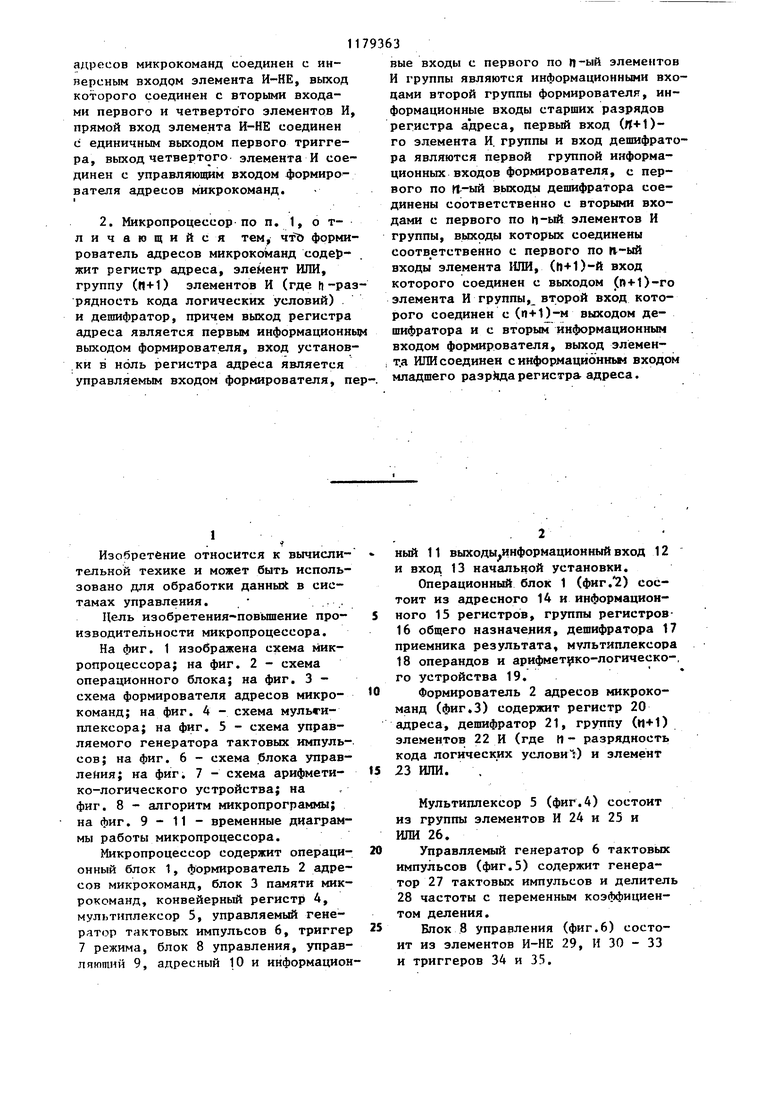

адресов микрокоманд соединен с иннерсным входом элемента И-НЕ, выход которого соединен с вторыми входами первого и четвертого элементов И, прямой вход элемента И-НЕ соединен с единичным выходом первого триггера, выход четвертого элемента И соединен с управляющим входом формирователя адресов микрокоманд. 2. Микропроцессор по п. 1, о тличающийся тем, что формирователь адресов микрокоманд содержит регистр адреса, элемент Ш1И, группу (П+1) элементов И (где h-раэ рядность кода логических условий) . и дешифратор, причем выход регистра адреса является первым информационны выходом формирователя, вход установки в ноль регистра адреса является управляемым входом формирователя, пе 1 3 вые входы с первого по ц-ый элементов И группы являются информационными входами второй группы формирователя, информационные входы старших разрядов регистра адреса, первый вход (Я+1)го элемента И. группы и вход дешифратора являются первой группой информационных входов формирователя, с первого по (t-ый выходы дешифратора соединены соответственно с вторыми входами с первого по элементов И группы, выходы которых соединены соответственно с первого по п-ый входы элемента ИЛИ, (h+1)-A вход которого соединен с выходом (п+1)-го элемента И группы, второй вход которого соединен с (п+О-м выходом дешифратора и с вторым информационным входом формирователя, выход элёмент.а ИЛИ соединен с информационньм входом младшего paэpkдaрегистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

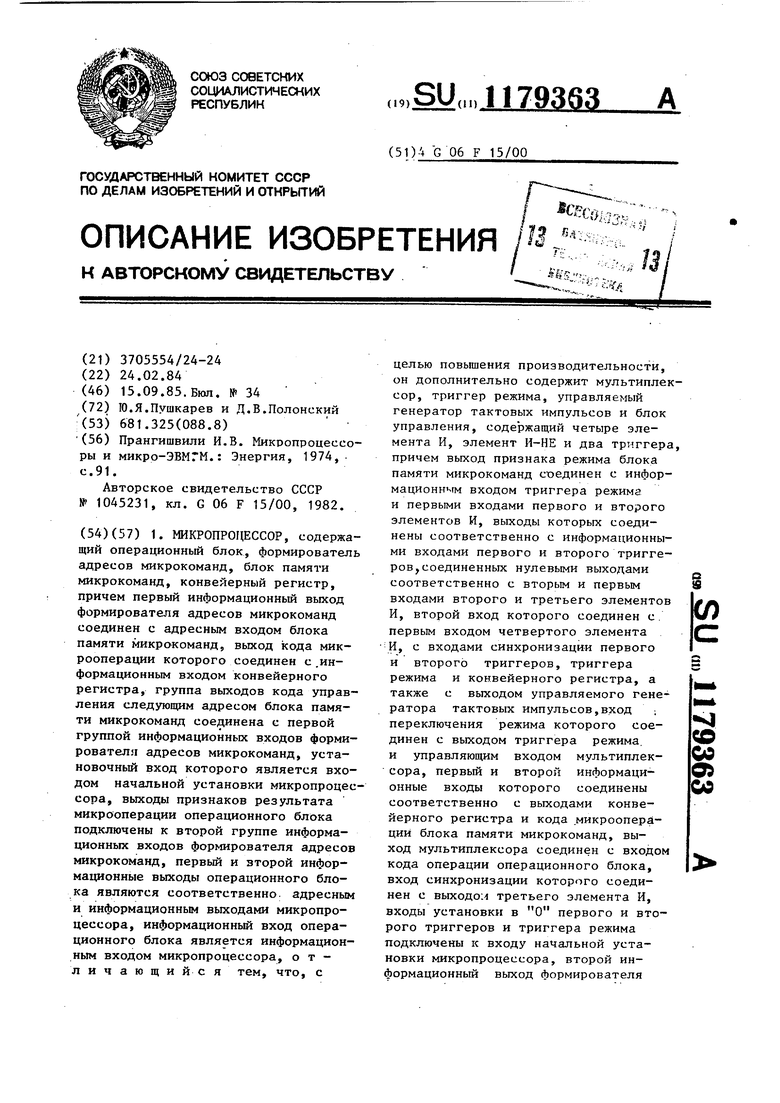

1. МИКРОПРОЦЕССОР, содержащий операционный блок, формирователь адресов микрокоманд, блок памяти микрокоманд, конвейерный регистр, причем первый информационный выход формирователя адресов микрокоманд соединен с адресным входом блока памяти микрокоманд, выход кода микрооперации которого соединен с.информационным входом конвейерного регистра, группа выходов кода управления следующим адресом блока памяти микрокоманд соединена с первой группой информационных входов формирователя адресов микрокоманд, установочный вход которого является входом начальной установки микропроцессора, выходы признаков результата микрооперации операционного блока подключены к второй группе информационных входов формирователя адресов микрокоманд, первый и второй информационные выходы операционного блока являются соответственно, адресным и информационным выходами микропроцессора, информационный вход операционного блока является информационным входом микропроцессора, о т личающийс я тем, что, с целью повышения производительности, он дополнительно содержит мультиплексор, триггер режима, управляемый генератор тактовых импульсов и блок управления, содержащий четыре элемента И, элемент И-НЕ и два триггера, причем выход признака режима блока памяти микрокоманд стоединен с информационным входом триггера режима и первыми входами первого и второго элементов И, выходы которых соединены соответственно с информационными входами первого и второго триггеров, соединенных нулевыми выходами в соответственно с вторым и первым входами второго и третьего элементов И, второй вход которого соединен с. первым входом четвертого элемента И, с входами синхронизации первого и второго триггеров, триггера режима и конвейерного регистра, а также с выходом управляемого генератора тактовых импульсов,вход vj переключения режима которого соесо со динен с выходом триггера режима, и управляющим входом мультиплекОд сора, первый и второй информацисо онные входы которого соединены соответственно с выходами конвейерного регистра и кода микроопераций блока памяти микрокоманд, выход мультиплексора соединен с входом кода операции операционного блока, вход синхронизации которого соединен с выходом третьего элемента И, входы установки в О первого и второго триггеров и триггера режима подключены к входу начальной установки микропроцессора, второй информационный выход формирователя

1

jИзобретение относится к вычислительной техике и может быть использовано для обработки данны:( в систамах управления. . .

Цель изобретения-повышение производительности микропроцессора.

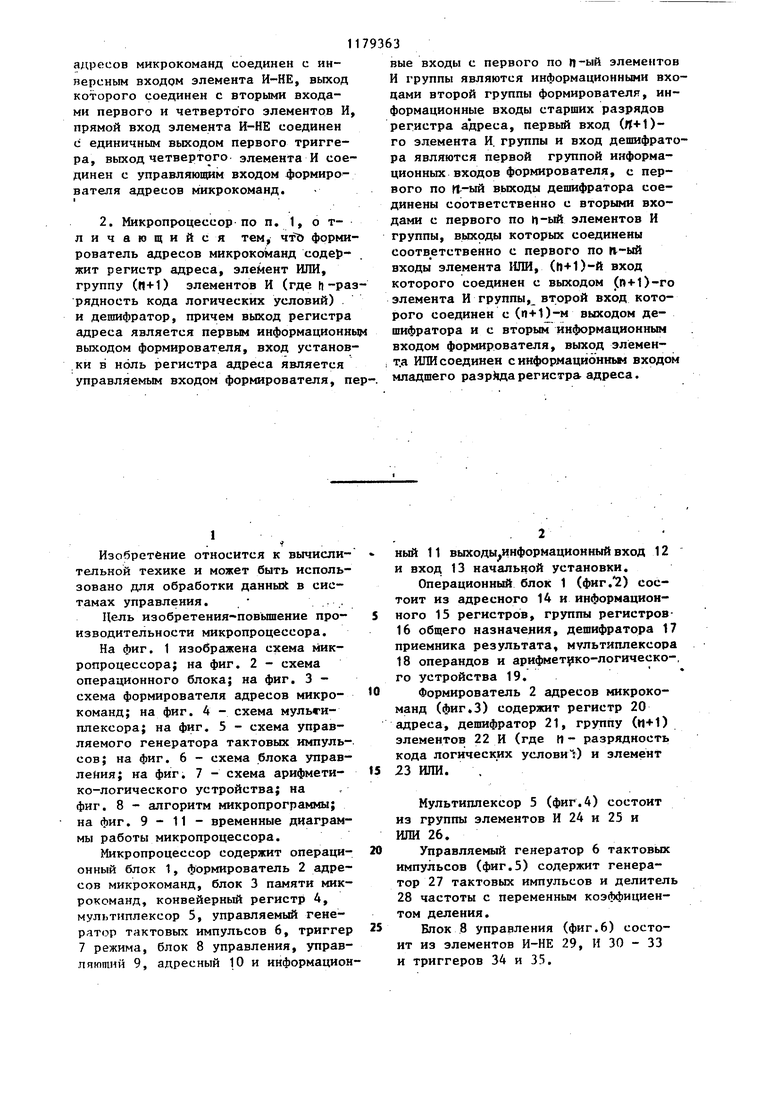

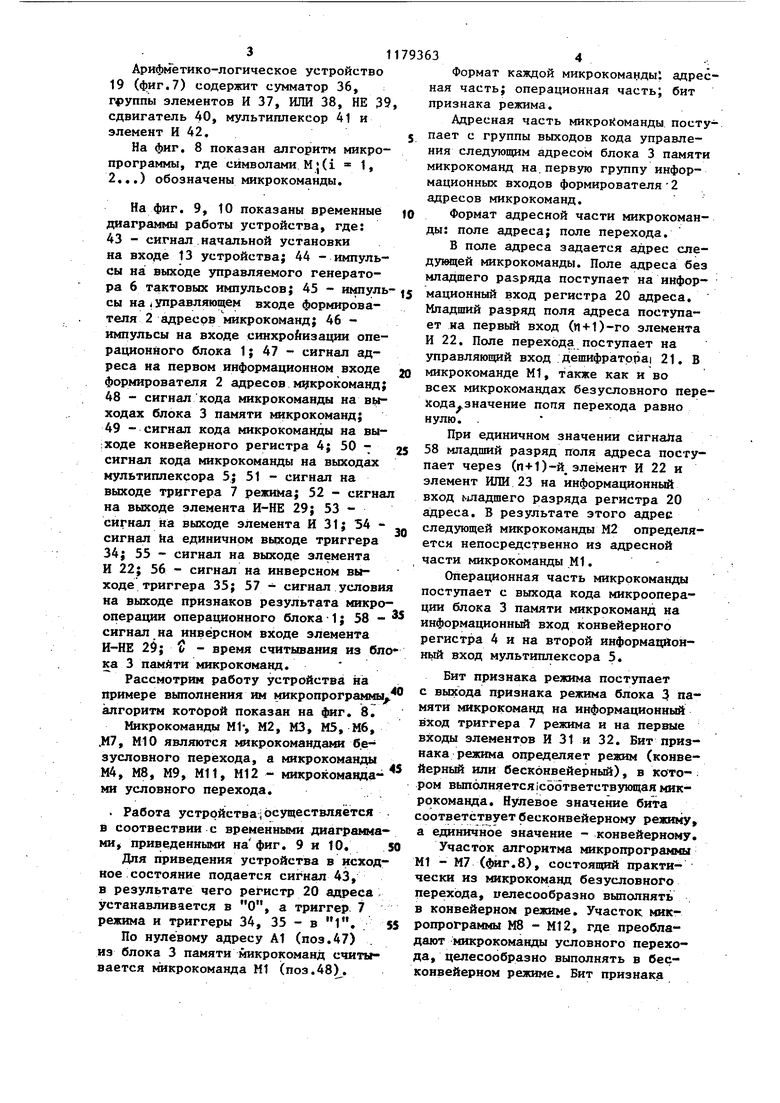

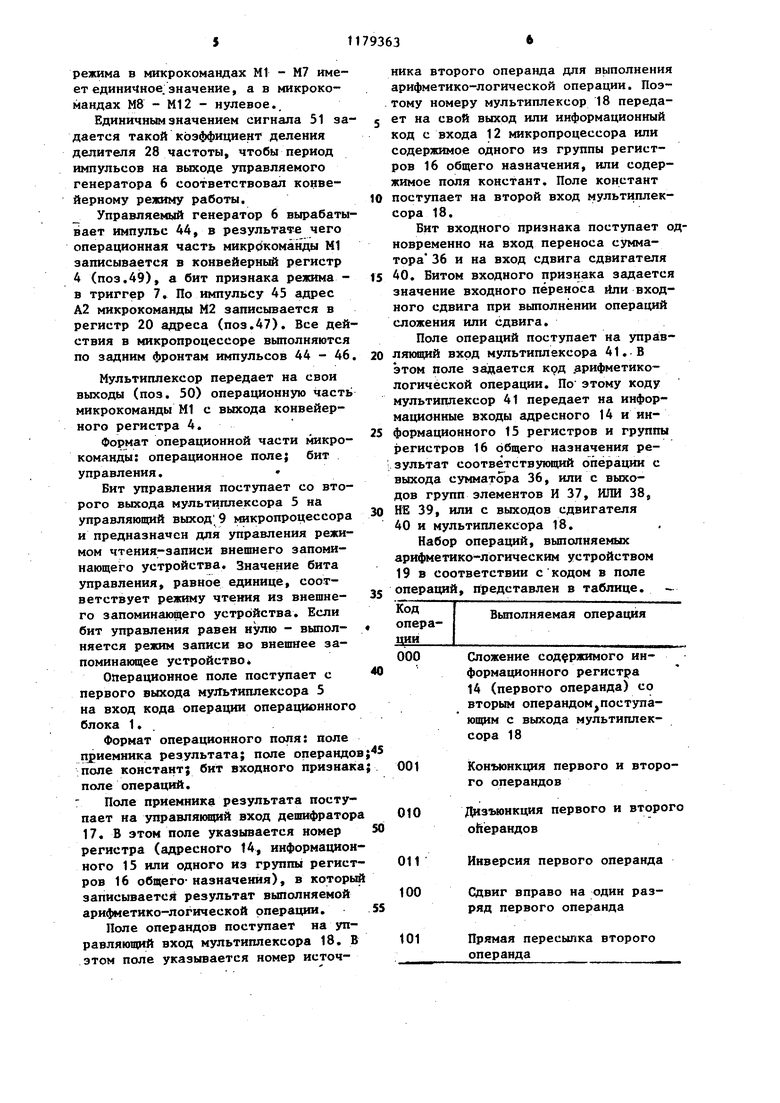

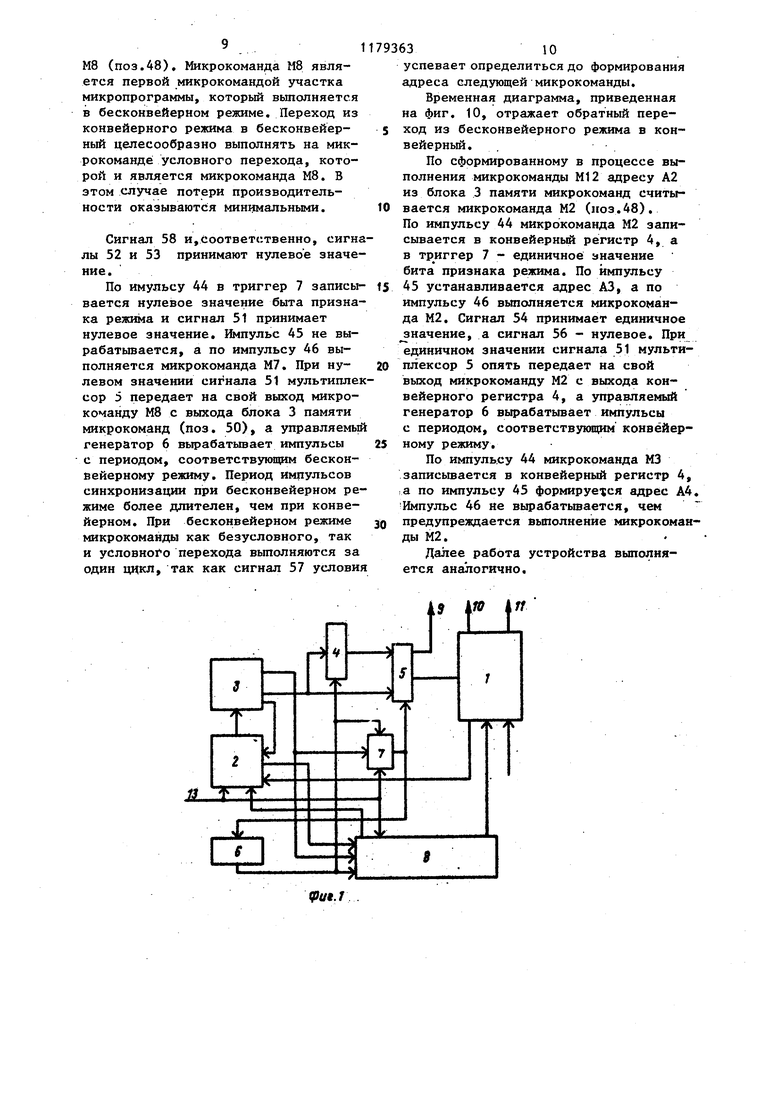

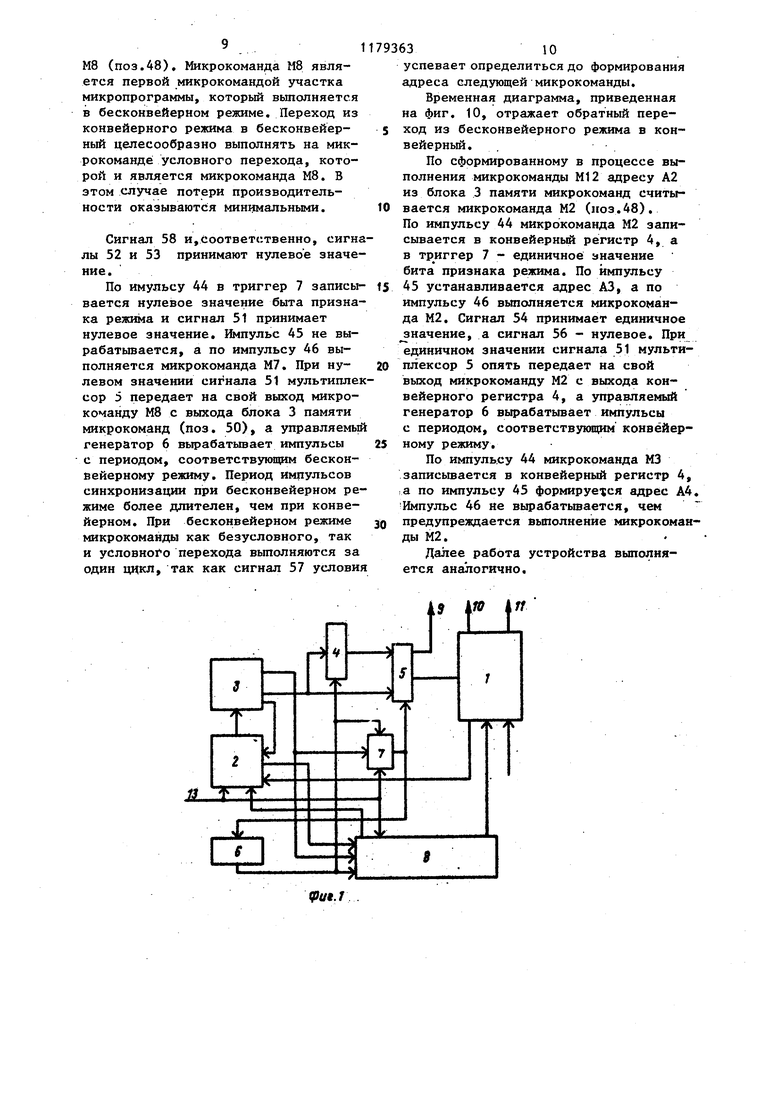

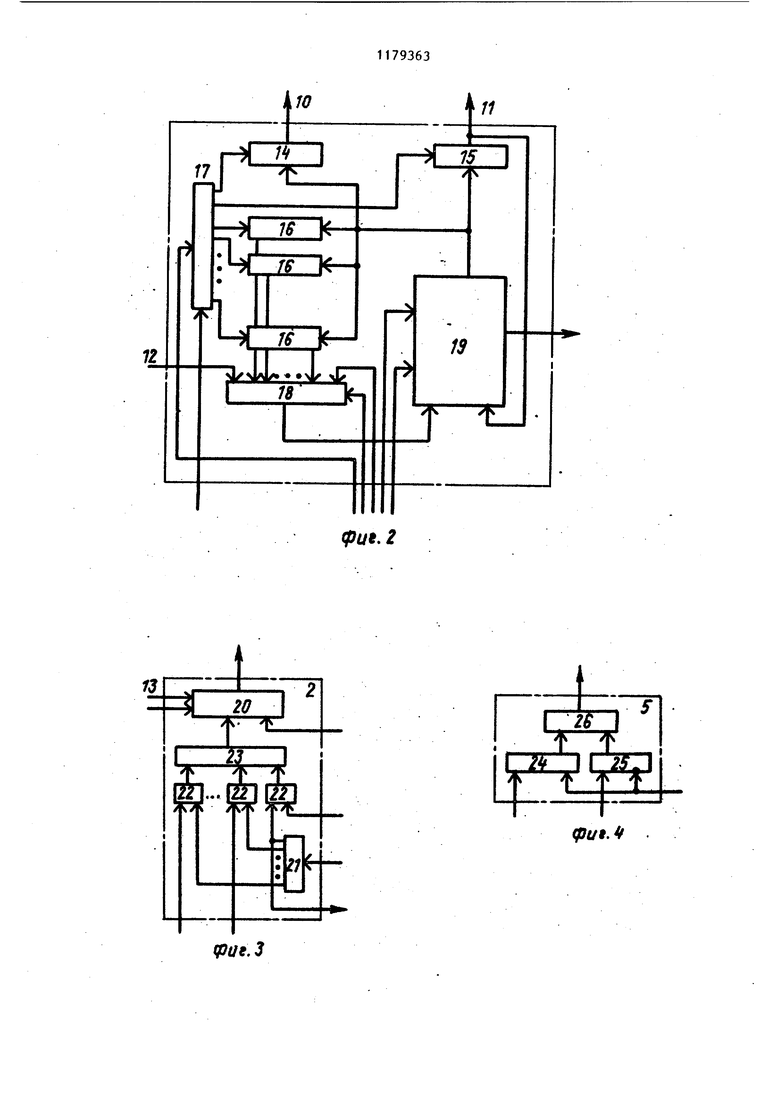

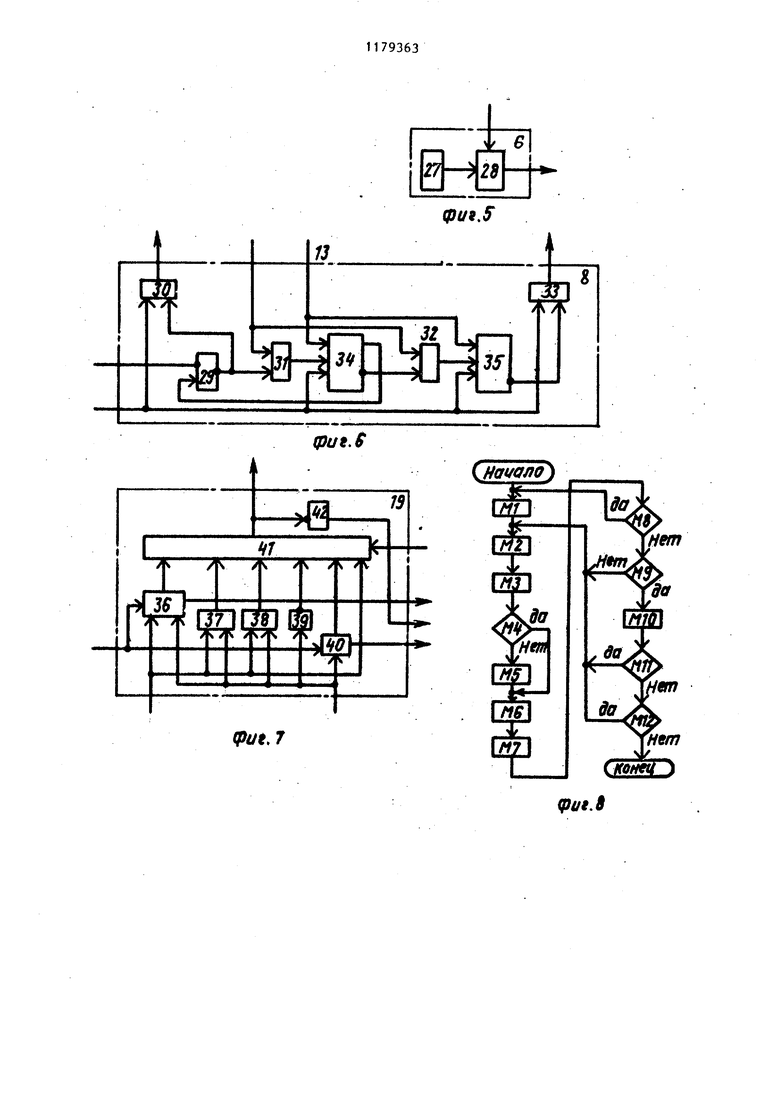

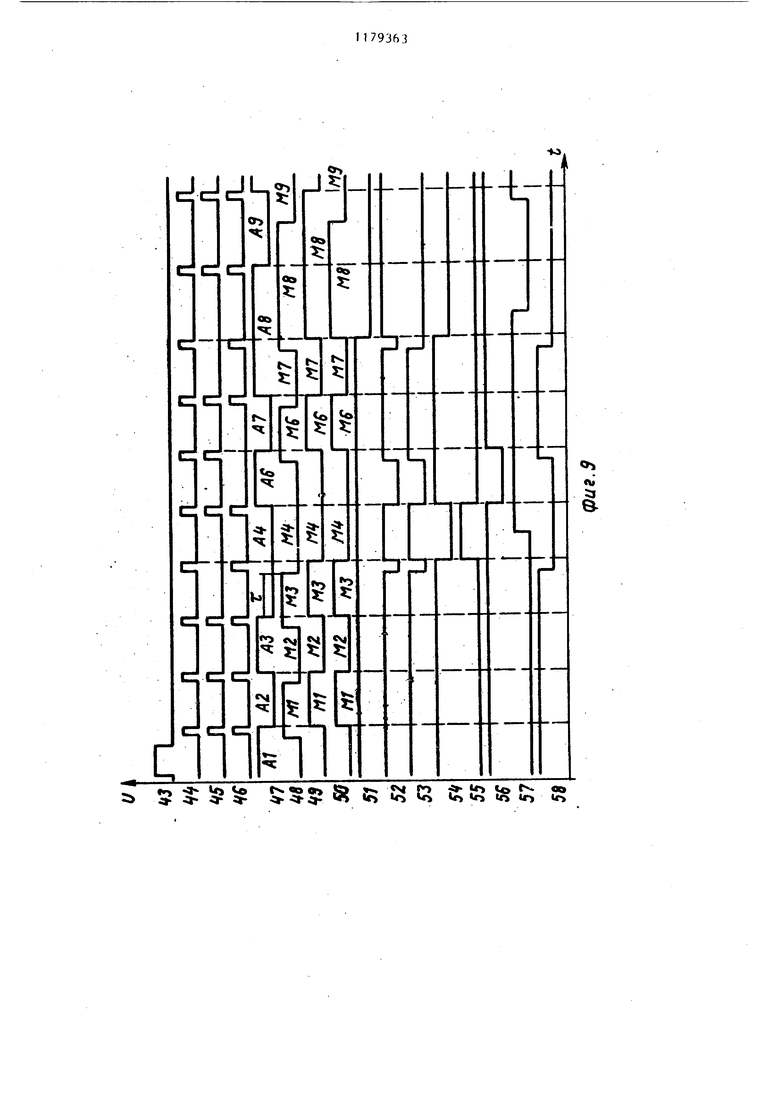

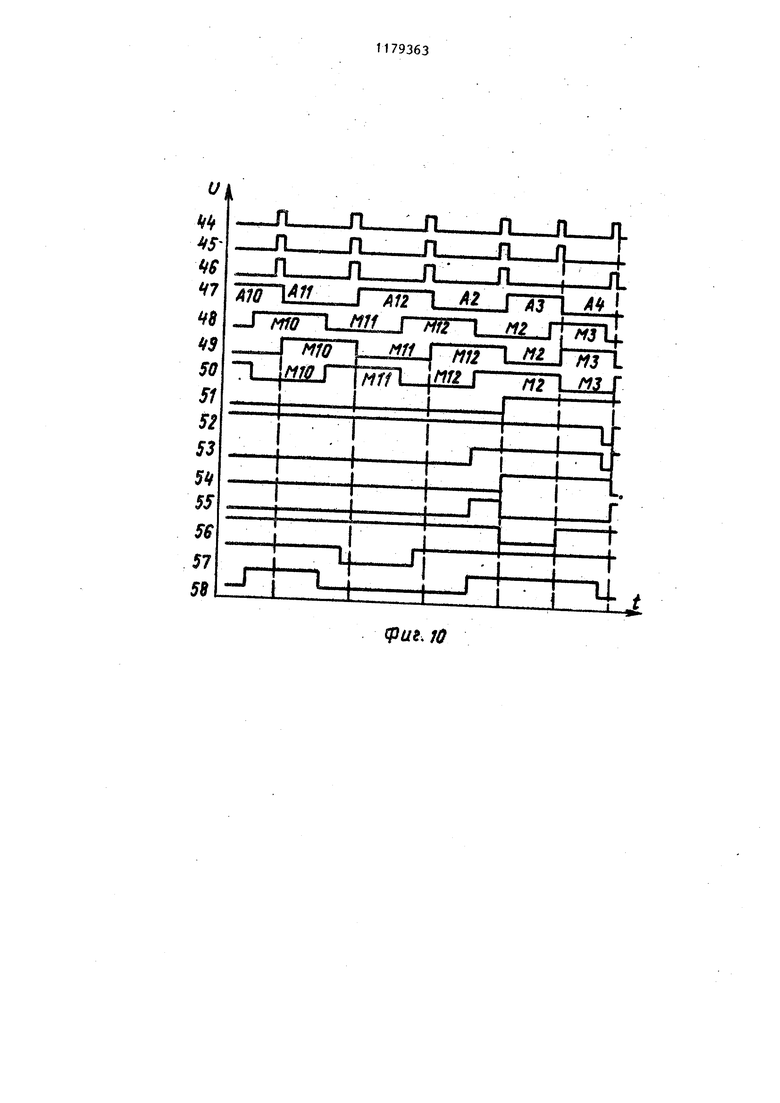

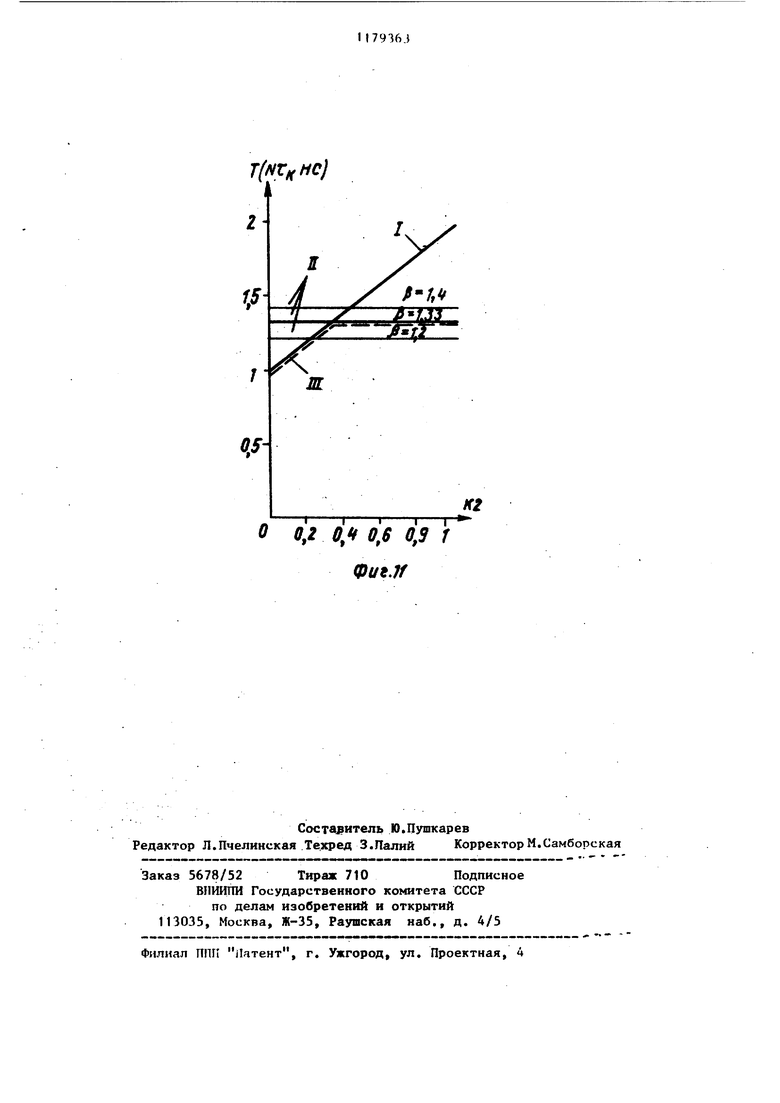

На фиг. 1 изображена схема микропроцессора; на фиг. 2 - схема операционного блока; на фиг. 3 схема формирователя адресов микрокоманд; на фиг. 4 - схема мульсиплексора; на фиг. 5 - схема управляемого генератора тактовых импульсов; на фиг. 6 - схема блока управлейия; на фиг. 7 - схема арифметико-логического устройства; на фиг. 8 - алгоритм микропрограммы; на фиг.9-11- временные диаграммы работы микропроцессора.

Микропроцессор содержит операционный блок 1, формирователь 2 адресов микрокоманд, блок 3 памяти микрокоманд, конвейерный регистр 4, мультиплексор 5, управляемый генератор тактовых импульсов 6, триггер 7 режима, блок 8 управления, управляющий 9, адресный 10 и информационный 11 выходы информационный вход 12 и вход 13 начальной установки.

Операционный блок 1 (фиг .2) состоит из адресного 14 и информационного 15 регистров, группы регистров16 общего назначения, дешифратора 17 приемника результата, мультиплексора 18 операндов и арифмет ко-логическо-, го устройства 19.

Формирователь 2 адресов микрокоманд (фиг.З) содержит регистр 20 адреса, дешифратор 21, группу (м+1) элементов 22 И (где Ц- разрядность кода логических услови ;) и элемент

23 ШШ. .

Мультиплексор 5 (фиг.4) состоит из группы элементов И 24 и 25 и ИЛИ 26.

Управляемый генератор 6 тактовых импульсов (фиг.5) содержит генератор 27 тактовых импульсов и делитель 28 частоты с переменным коэффициентом деления.

Блок 8 управления (фиг.6) состоит из элементов И-НЕ 29, И 30 - 33 и триггеров 34 и 35. Арифметико-логическое устройство 19 (фиг.7) содержит сумматор 36, группы элементов И 37, ИЛИ 38, НЕ 39 сдвигатель 40, мультиплексор 41 и элемент И 42. На фиг, 8 показан алгоритм микропрограммы, где символами Мj(i 1, 2...) обозначены микрокоманды. На фиг. 9, to показаны временные диаграммы работы устройства, где: 43 - сигнал начальной установки на входе 13 устройства; 44 - импульсы на выходе управляемого генератора 6 тактовых импульсов; 45 - импуль сы наiуправляющем входе формирователя 2 адресов микрокоманд; 46 импульсы на входе синхронизации операционного блока 1; 47 - сигнал адреса на первом информационном входе формирователя 2 адресов М1 крокоманд 48- сигнал кода микрокоманды на въхходах блока 3 памяти микрокоманд; 49- сигнал кода микрокоманды на вы;ходе конвейерного регистра 4; 50 сигнал кода микрокоманды на выходах мультиплексора 5; 51 - сигнал на выходе триггера 7 режима; 52 - сигна на выходе элемента И-НЕ 29; 53 сигнал на выходе элемента И 31; 54 сигнал ha единичном выходе триггера 34; 55 - сигнал на выходе элемента И 22; 56 - сигнал на инверсном выходе триггера 35; 57 - сигнал услови на выходе признаков результата микро операции операционного блока1; 58 сигнал на инверсном входе элемента И-НЕ 29; iJ - время считывания из бл ка 3 памйти микрокоманд. Рассмотрим работу устройства на примере выполиения IO4 микропрограммы алгоритм которой показан на фиг. 8. Микрокоманды Ml, М2, МЗ, М5, Мб, .М7, Ml О являются микрокомандами безусловного перехода, а микрокоманды М4, М8, М9, Mil, Ml2 - микрокомандами условного перехода. . Работа устройства осуществляется в соотвествии с временными диаграмма ми приведенными нафиг. 9 и 10. Для приведения устройства в исход ное состояние подается сигнал 43, в результате чего регистр 20 адреса устанавливается в О, а триггер. 7 режима и триггеры 34, 35 - в 1, , По нулевому адресу А1 (поз.47) . из блока 3 памяти микрокоманд считывается микрокоманда Ml (поз.48). Формат каждой микрокоманды адресная часть; операционная часть; бит признака режима. Адресная часть микройоманды поступает с группы выходов кода управления следующим адресом блока 3 памяти микрокоманд на. первую группу информационных входов формирователя 2 адресов микрокоманд. Формат адресной части микрокоманды: поле адреса; поле перехода. В поле адреса задается адрес следушцей микрокоманды. Поле адреса без младшего разряда поступает на информационный вход регистра 20 адреса. №1адший разряд поля адреса поступает на первый вход (н+1)-го элемента И 22. Поле перехода поступает на управляющий вход дешифратора 21. В микрокоманде Ml, также как и во всех микрокомандах безусловного переХода значение попя перехода равно нулю. . При единичном значении сигнала 58 младший разряд поля адреса поступает через (п + 1)-й элемент И 22 и элемент ИЛИ 23 на информационный вход младшего разряда регистра 20 адреса. В результате этого адрес следующей микрокоманды М2 определяется непосредственно иэ адресной части микрокоманды Ml. Операщюнная часть микрокоманды поступает с выхода кода микрооперации блока 3 памяти микрокоманд на информационный вход конвейерного регистра 4 и на второй информацйоннь1й вход мультиплексора 5. Бит признака режима поступает с выхода призиака режима блока 3 памяти микрокоманд на информационный вход триггера 7 режима и на первые входы элементов И 31 и 32. Бит признака режима определяет режим (конвейерный или бесконвейерный), в кото- : ром выполняется {Соответствующая микрокоманда. Нулевое значение бита оответствует бесконвейерному режиму, а единичное значение - конвейерному. Участок алгоритма микропрограммы Ml - М7 (фиг.8), состоящий практически из микрокоманд безусловного перехода, иелесообразно выполнять в конвейерном режиме. Участок микопрограммы М8 - Ml 2, где преоблаают микрокоманды условного перехоа, целесообразно выполнять в бесконвейерном режиме. Бит признака режима в микрокомандах Ml - М7 имеет единичное значение, а в микрокомандах М8 - Ml2 - нулевое.. Единичным значением сигнала 51 задается такой коэффициент деления делителя 28 частоты, чтобы период импульсов на выходе управляемого генератора 6 соответствовал конвейерному режиму работы. Управляемый генератор 6 вырабатывает импульс 44, в результате чего операционная часть микрокоманды Ml записывается в конвейерный регистр 4 (поз.49), а бит признака режима в триггер 7. По импульсу 45 адрес А2 микрокоманды М2 записывается в регистр 20 адреса (поз.47). Все действия в микропроцессоре выполняются по задним фронтам импульсов 44 - 46 Мультиплексор передает на свои выходы (поз. 50) операционную часть микрокоманды Ml с выхода конвейерного регистра 4. Формат операционной части микрокоманды: операционное поле; бит управления. Бит управления поступает со второго выхода мультиплексора 5 на управляющий выход; 9 микропроцессора и предназначен для управления режимом чтения-записи внешнего запоминающего устройства. Значение бита управления, равное единице, соответствует режиму чтения из внешнего запоминающего устройства. Если бит управления равен нулю - выполняется режим записи во внешнее запоминакидее устройство Операционное поле поступает с первого выхода мультиплексора 5 на вход кода операции операционного блока 1. . Формат операционного поля: поле п риемника результата; поле операндо поле констант; бит входного призна поле операций. Поле приемника результата посту пает на управляниций вход дешифрато 17. В этом поле указывается номер регистра (адресного 14, информацио ного 15 или одного из группы регис ров 16 общего-назначения), в котор записывается результат выполняемой арифметико-логической операции. Поле операндов поступает на уп равляющий вход мультиплексора 18. этом поле указывается номер источика второго операнда для выполнения арифметико-логической операции. Поэому номеру мультиплексор 18 передает на свой выход или информационный код с входа 12 микропроцессора или содержимое одного из группы регистров 16 общего назначения, или содержимое поля констант. Поле констант поступает на второй вход мультиплексора 18. Бит входного признака поступает одновременно на вход переноса сзжматора 36 и на вход сдвига сдвигателя 40. Битом входного признака задается значение входного переноса или входного сдвига при выполнении операций сложения или сдвига. Поле операций поступает на управляющий вход мультиплексора 41. В этом поле задается крд .арифметикологической операции. По этому коду мультиплексор 41 передает на информационные входы адресного 14 и информационного 15 регистров и группы регистров 16 общего назначения результат соответствующий операции с выхода сумматора 36, или с выходов групп элементов И 37, ИЛИ 38, НЕ 39, или с выходов сдвигателя 40 и мультиплексора 18. Набор операций, выполняемых арифметико-логическим устройством 19 в соответствии скодом в поле операций, представлен в таблице. - Выполняемая операция опера000Сложение содержимого информационного регистра 14 (первого операнда) со вторым операндом,поступающим с выхода мультиплексора 18 001Конъюнкция первого и второго операндов 010Диз-ыонкция первого и второго операндов 011Инверсия первого операнда 100Сдвиг вправо на один разряд первого операнда 101Прямая пересыпка второго операнда

Если результат операции .равен нулю - на выходе элемента 42 И вырабатывается единичный сигнал. Сигнал с выхода элемента 42 И, так же как и сигналы с выходов переноса сумматора 36 и сдвига сдвигателя 40 поступают на дыходы признаков результата микрооперации операционного блока 1.

По адресу А2 из блока 3 памяти микрокоманд считывается микрокоманда М2 (поз.48). По импульсу 44 операционная часть микрокоманды М2 записывается в конвейерный регистр 4 (поз,49). По импульсу 45 в регистр 20 адреса записывается адрес A3 (поз.47), заданный в поле адреса {шкрокоманды М2, по импульсу 46 результат арифметико-логической oneрации микрокоманды Ml с выхода арифметико-логического устройства 19 записывается в один из приемников (адресный 14, информационный 15 регистры или один из группы регистров 16 общего назначения в зависимости от кода в поле приемника результата.

Информация с выходов адресного 14 и информационного 15 регистров поступает соответственно на выходи 10 и 11 микропроцессора. В&коды 9-11 микропроцессора предназначены для подключения к нему внешнего запоминающего устройства (ВЗУ). Если микропроцессор производит запись в ВЗУ, то по адресуустановленному на выходе нулевом значении бита управления на выходе 9 микропроцессора в ВЗУ записываются данные с выхода 11 микропроцессора. В рсжимд чтения на выход 9 поступает единичное значение бита управления и по адресу, установленному на выходе 10 микропроцессора, из ВЗУ считывается информация и поступает на вход 12 микропроцессора. .

После выполнения микрокоманды М2 по адресу А4 (поз. 47)из блока 3 памяти микрокоманд считывается микрокоманда М4 (поз. 48). Микрокоманда М4 является микрокомандой условноного перехода и в адресной части содержит ненулевое значение поля, перехода. В результате.сигнал 58, а зате и сигналы 52 и 53 принимают нулевое значение.

В поле перехода микрокоманды М4 задается номер условия, по которому

ссуществляется переход. По единичному сигналу на одном из выходов (кроме (f + 1)-ro) дешифратора 21 открывается соотвествующий элемент 22 И группы и сигнал проверяемого условия поступает с одного из информационных входов второй группы формирователя 2 на информационный вход младшего разряда регистра 20 адреса.

По очередному импульсу 44 микрокоманда М4 записывается в конвейерный реглстр 4. П импульсу 46 выполняется микрокоманда МЗ. Импульс 45 не вьфабатьшается, так как элемент И 30 закрыт сигналом 52. Это обусловлено тем, что значение сигнала 57 условия формирования адреса следующей микрокоманды к данному моменту времени еще не определено.

Значения адреса А4 на выходе формирователя 2 и кода микрокоманды М4 на выходе блока. 3 памяти микрокоманд не изменяются. Триггер 34 устанавливается в О, в результате чего сигнал 54 принимает нулевое значение, а сигналы 52,53 и 55 - единичное.. При выполнении микрокоманды М4 (поз.50) формируется значение сигнала 57 условия. По импульсу 44 в конвейерный регистр 4 опять записывается микрокоманда М4. По импульсу 45 в регистр 20 адреса записывается адрес А6, сформированный с учетом единичного значения сигнала 57. По импульсу 46 результат вьтолнения арифметической операции микрокоманды М4 записывается в один из внутренних регистров операционного блока 1.

Триггеры 34 и 35 устанавливаются в 1, в результате чего сигналы 55 и 56 принимают нулевое значение.

По следующему;импульсу 44 в конвейерный регистр 4 записьгаастся микрокоманда Мб, а по импульсу 45 устанавливается адрес А7 на выходе формирователя 2. Импульс 46 не вырабатывается, так как элемент 33 И закрыт сигналом 56. Тем самым предупреждается повторное выполнение микрокоманды Н4. Сигнал 56 принимает единичное значение. Следовательно, микрокоманда условного перехода при конвейерном режиме выполняется в течение двух циклов микрокоманд.

После вьшолнения микрокоманды Мб «ПО адресу А8 из блока 3 памяти микрокоманд считывается микрокоманда

М8 (поз.48), Микрокоманда М8 является первой микрокомандой участка микропрограммы, который вьшолняется в бесконвейерном режиме. Переход из конвейерного режима в бесконвейерный целесообразно выполнять на микрокоманде условного перехода, которой и является микрокоманда MB. В этом случае потери производительности оказываются минимальными.

Сигнал 58 и,соответственно, сигна лы 52 и 53 принимают нулевое значение.

По имульсу 44 в триггер 7 записывается нулевое значение быта признака режима и сигнал 51 принимает нулевое значение, импульс 45 не вырабатывается, а по импульсу 46 выполняется микрокоманда М7. При нулевом значении сигнала 51 мультиплексор 5 передает на свой выход микрокоманду М8 с выхода блока 3 памяти микрокоманд (поз. 50), а управляемьА генератор 6 вырабатывает импульсы с периодом, соответствующим бесконвейерному режиму. Период импульсов синхронизации при бесконвейерном режиме более длителен, чем при конвейерном. При бесконвейерном режиме микрокоманды как безусловного, так и условного перехода вьтолняются за один ццкл, так как сигнал 57 условия

7936310

успевает определиться до формирования адреса следующей микрокоманды.

Временная диаграмма, приведенная на фиг. 10, отражает обратный переход из бесконвейерного режима в конвейерный.

По сформированному в процессе выполнения микрокоманды Ml 2 адресу А2 из блока 3 памяти микрокоманд считывается микрокоманда М2 (поз.48).

По импульсу 44 микрокоманда М2 записывается в конвейерньй регистр 4, а в тр иггер 7 - единичное значение бита признака режима. По импульсу 15 45 устанавливается адрес A3, а по импульсу 46 выполняется микрокоманда М2. Сигнал 54 принимает единичное значение, а сигнал 56 - нулевое. При единичном значении сигнала 51 мультиплексор 5 опять передает на свой выход микрокоманду М2 с выхода конвейерного регистра 4, а управляемый генератор 6 вырабатывает импульсы с периодом, соответствукнцим конвёйер5 ному режиму.

По импульсу 44 микрокоманда МЗ записьтается в конвейерный регистр 4, la по импульсу 45 формируемся адрес А4. Импульс 46 не вырабатывается, чем 0 предупреждается вьшолнение микрокоманды М2.

Далее работа устройства выполняется аналогично.

10

(put. 2

11

i

jr jrsrpj

(flt/t.

iptte.3

-±

28

фи9.5

(put.

ЧГ

7 5 / / f

у I

tpui.7

(

CKOffeu 3

pi/t,8

«o 53--3r r «o«o«otr

t

(риг. 10

r(

г

US

0 0,2 0,4 0,3 r

| Прангишвили И.В | |||

| Микропроцессоры и микро-ЭВМГМ.: Энергия, 1974, с.91 | |||

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-02-24—Подача