(54) УСТРОЙСТВО ДЛЯ ФАЗОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фазовой синхронизации | 1985 |

|

SU1401630A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1984 |

|

SU1150660A1 |

| ОДНОКАНАЛЬНАЯ МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ЦЕЛЬ | 1997 |

|

RU2108595C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| Генератор корректирующего сигнала | 1985 |

|

SU1293857A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

Изобретение относится к технике передачи дискретной информации на расстояние и мсжет быть использовано в аппаратуре приема дискретной информации по линиям связи.

Известно устройство для фазовой синхронизации, содержащее последовательно соединенные интегратор, управляемый генератор, делитель частоты и счетчик синхроимпульсов, а также элемент И ij. Q

Однако известное устройство имеет сравнительно низкую точность синхронизации, обусловленную сравнительно большим периодом измерения величины фазового рассогласования,

Цель изобретения - повьпиение точности синхронизации путем уменьшения лериода измерения величины фазового рассогласования.

Цель достигается тем, что в устрой- 20 ство для фазовой синхронизации, содержащее последовательно соединенные ин- тегратор, ущзавляемый генератор, делитель частоты и счетчик синхроимпульсов.

,а также элемент И,.введены блок задержки и последовательно-соединенные блок выделения фронтов сигнала, преобразова- тель и регистр рассогласования/выходы которого подключены ко входу интегратора и первому входу элемента И, к второму входу которого подключен выход управляемого генератора, а выход элемента И подключен к счетному входу регистра рассогласования, при этом выход блока выделения )OHTOB сигнала через блок задержки подключен ко входу сброса счетчика синхроимпульсов и корректирующему входу делителя.частоты, выход которого подключен к втсрому входу преобразователя, к третьему входу которого подключен выход счетчика синхроимпульсов.

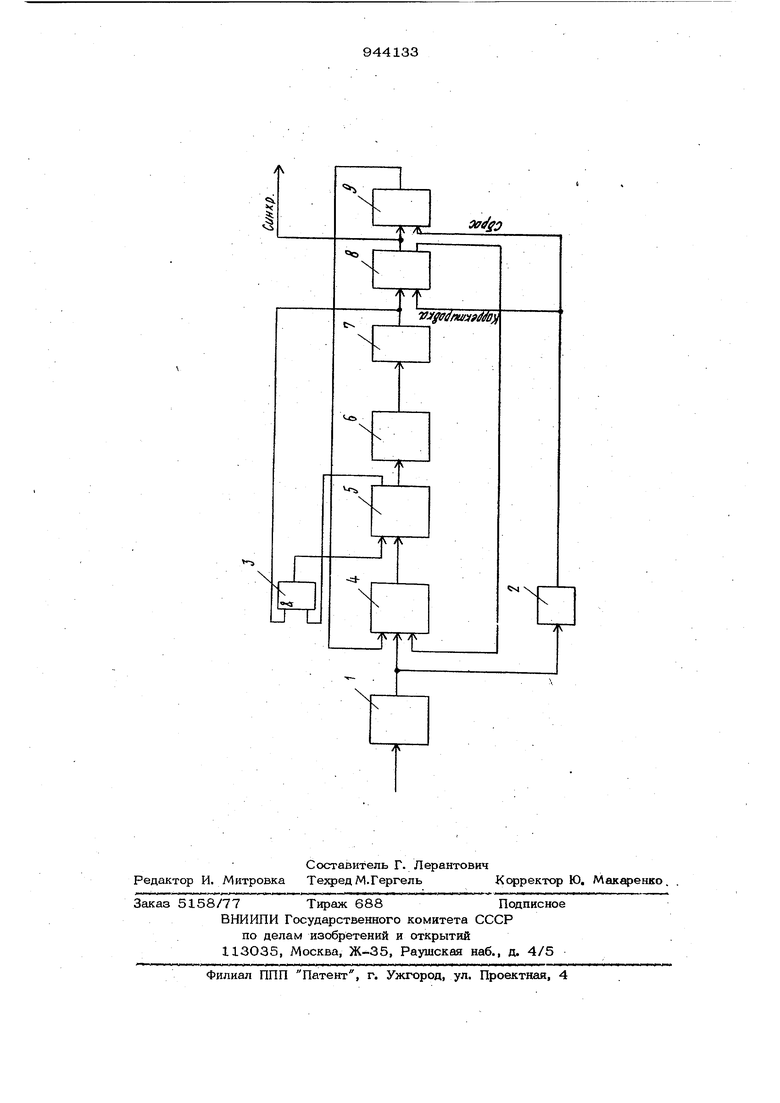

На чертеже предстгшлена структурная электрическая схема устройства.

Устройство содержит блок 1 вьщеления фронтов согнала, блок 2 задерт ки, элемент И 3, 1феобразователь 4, регистр 5 рассогласования, интегратор 6, управляемый генератор 7, делитель 8 частоты, счетчик 9 синхроимпульсов. Устройство работает следующим об разом.. Передние фонты сигналов информаци с блока 1 выделения фронтов сигнала возбуждают преобразователь 4, на второй вход которого поступают сигналы с второго выхода делителя частоты, код на котором указывает величину рассогласования фаз синхроимпульсов и сигналов инфсрмацяи, а на третий вход пре обравователя поступают сигналы с выхода счетчика синхроимпульсов, код последнего фиксирует время отсутствия сигналов информации иа линии связи. Преобразователь 4 путем деления ко делителя 8 частоты на код счетчика 9 синхроимпульсов определяет знак и код рассогласования и устанавливает в соответствующей положение триггерь на регистре 5-рассогласования. Сигнал с, выхода регистра 5 рассогласования возбуждает интегратор 6. Время возбуждения интегратора 6 определяется количеством синхроимпульсов, поступакицих на счетныйвход регистра 5 рассогласования с элемента И 3, выгзывающих переполнение регистра 5 рассогласования. В случае переполнения регистра 5 рассогласования прекращается появление сигналов с выхода элемента И 3 и производятся блокировка возбуждения интегратора 6. Задержанным сигналом с блока 1 выделения фронтов сигнала на блоке 2 задержки производится корректировка кода на делителе 8 частоты и сбра сывается код на счетчик -9 синтфоимпульсов. Изменение потенциала на выходе интегратора 6 вызывае изменение частоты на выхсще управляемого генератора 7. Таким образом, устройство для фазовой синхронизации обеспечивает повышение точности синхронизации путем уменьшения периода измерения величины фазового рассогласования. Формула изобретения Устройство для фазовой синхронизации, содержащее последовательно соединен- , ные интегратор, управляемый генератор, делитель частоты и счетчик синхроимпульсов, а также элемент И, о т л и ч а ю щ е е с я тем, что, с целью повыщения точности синхронизации путем уменьшения периода измерения величины фазового рассогласования, введены блок задержки и последовательно соединенные блок выделения фронтов сигнала, преобразователь и регистр рассогласования, выходы которого подключены к входу интегратора и первому входу элемента И, к второму входу котсрого подключен выход управляемого, генератора, а выход элемента И-подключен к счетному входу регистра рассогласования, при этом выход блока вы-г деления фронтов сигнала через блок задержки подключен к входу сброса -счетчика синхроимпульсов и корректирующему входу делителя частоты, выход которого подключен к второму входу преобразователя, к третьему входу которого подключен выход счетчика синхроимпульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 6О532а, кл. Н, О4Ь 7/О6, 1972 (npoTOTfm).

Авторы

Даты

1982-07-15—Публикация

1980-12-31—Подача