(5) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1980 |

|

SU944135A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство цикловой синхронизации | 1987 |

|

SU1510104A1 |

| Устройство для синхронизации по циклам | 1991 |

|

SU1811019A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

1

Изобретение относится к технике связи и предназначено для синхронизации цифровых систем связи с импульсно-кодовой модуляцией и аремен. нык делением каналов (ИКМ-ВД).

По основному авт.св. № 661836 известно устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, дешифратор, первый анализатор и первый накопитель, к другому входу которого подключен другой выход первого анализатора, а выход - к одному из входов элемента И и к другим входам которого подключены выход дешифратора непосредственно и через последовательно соединенные второй анализатор, блок управления и делитель частоты, выход которого подключен к другому входу второго анализатора, а выход элемента И подключен через генераторный блок к другому входу первого анализатора, причем на управляющие входы регистра сдвига, делителя частоты и генераторного блока подан сигнал тактовой частоты, а так- же измеритель вероятности искажения сигнала, при этом вход группового сигнала регистра сдвига через измеритель вероятности искажения сигнала соединен с дополнительным управляющим входом первого накопителя ШОднако это устройство имеет неtoдостаточную надежность удержания синхронизма при частых искажениях позиций циклового синхросигнала.потому что есть вероятность сколь угодно длительного искажения этих

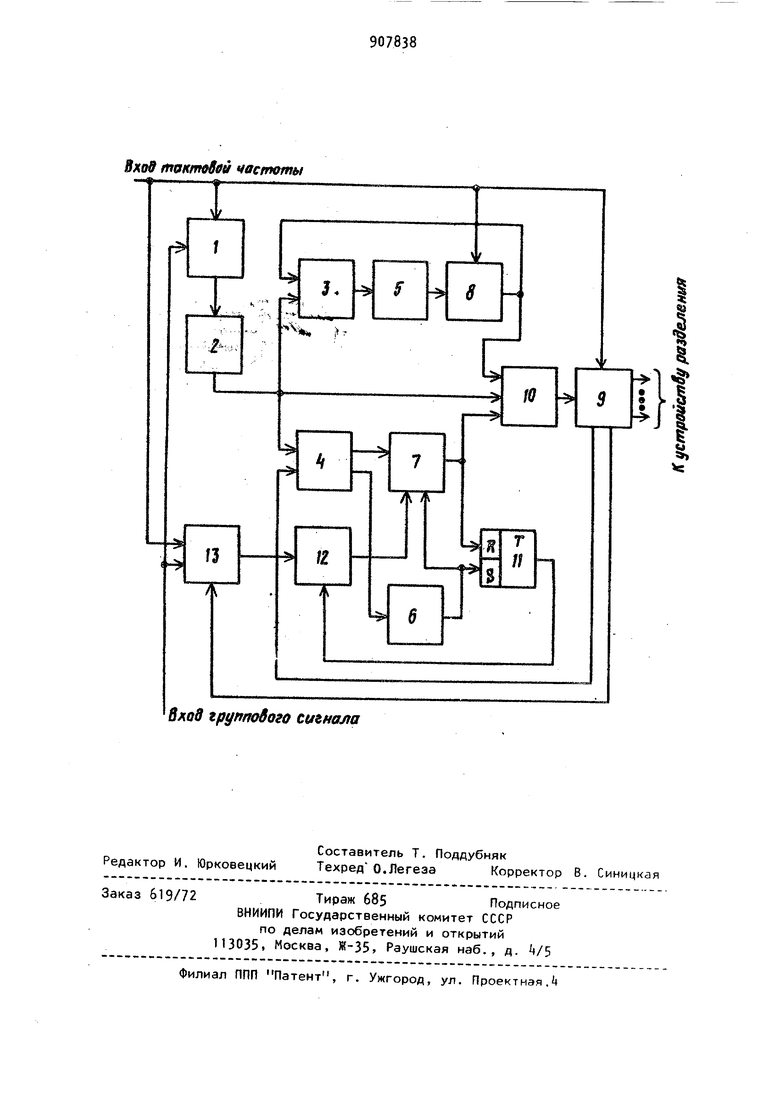

IS позиций во входном групповом сигнале и что, а конечном итоге, приводит к заполнению накопителя по выходу из синхронизма,, ложной установке генераторного блока, а, следователь20но, к сбою работы последнего. Это происходит потому, что измеритель искажения сигнала не уничтожает память об ошибках,вызванных искажениями циклового синхросигнала, а лишь увеличивает емкость накопителя по выходу из синхронизма, тем самым разрешает накопление ошибок и заполнение ими последнего. Кроме того поскольку измеритель искажения сигна ла учитывает все возможные ошибки во входном групповом сигнале, то при сбое синхронизма,- наличие на выходе измерителя сигнала замедления заполнения BTdporo накопителя задерживает прохождение через элемент И установки генераторного блока, т.е. увеличивает время восстановления синхронизма, а значит устройство имеет сравнительно низкое быстродействие. Цель изобретения - повышение помехоустойчивости и быстродействия. Для достижения этой цели в устройство цикловой синхронизации введе ны элемент НЕТ и RS-триггер, первый и второй входы которого подключены к выходам соответствующих накопителей, а выход nS-триггера подсоединен к первому входу элемента НЕТ, яторой вход которого подключен к выходу измерителя вероятности,искажения сигна лов, а выход элемента НЕТ подсоединен к дополнительному входу первого накопителя, при этом дополнительный выход генераторного оборудования подсоединен к дополнительному входу измерителя вероятности искажения сиг нала. На чертеже приведена структурноэлектрическая схемз устройства цикло вой синхронизации. Устройство цикловой синхронизации содержит регистр Т , дешифратор 2, анализаторы 3 и , блок 5 управления , накопители по входу 6 и по выходу 7, делитель 8 частоты, генераторный блок 9, элемент И 10,RS-три гер 11, элемент НЕТ 12, измеритель 13 искажения сигнала. Устройство работает следующим образом. В состоянии синхронизма сигналы на выходах дешифратора 2, делители 8 частоты и генераторного блока 9 совпадают по времени. При этом на выходе анализатора k периодически появляются сигналы, заполняющие накопитель 6 по входу, а накопитель 7 по выходу опустошен. На выходе элемента И-10 сигнала нет, и генераторный блок 9 работает синхронно с входным групповым сигналом. На выходе RS-триггера 11 высокий потенциал, и элемент НЕТ 12 открыт. При искажениях циклового синхросигнала на выходе дешифратора 2 в эти моменты времени сигналы отсутствуют, а на выходе анализатора Ц формируются сигналы несовпадения, которые записываются 8 накопитель 7 по выходу. Одновременно с дополнительного выхода генераторного блока 9 на измеритель 13 искажения сигнала поступает импульсная последовательность огибающая синхросигнала, с помощью которой на выходе измерителя 13 Формируются сигналы, соответствукхцие искаженным синхрогруппам. Пройдя элемент НЕТ 12, эти сигналы вновь опустошают накопитель 7 по выходу. Таким образом, как бы часто не искажался цикловой синхросигнал,накопитель 7 по выходу будет постоянно опустошаться, а ложные синхрокомбинации, присутствующие во входном групповом сигнале и выделяемые дешифратором 2, не могут осуществить сбой генераторного блока 9. ввиду отсутствия на входе элемента И 10 сигнала разрешения с выхода накопителя 7 по выходу, чем и достигается повышение помехоустойчивости устройства. При нарушении синхронизма сигналы на входах анализаторов 3 и не синфазны, сигналы несовпадения с выхода анализатора k поступают на вход накопителя 7 по выходу и заполняют его, на выходе последнего появляется сигнал, который устанавливает низкий потенциал на выходе RS-триггера 11, Этим потенциалом элемент НЕТ 12 закрывается и запрещает прохождение сигналов с выхода измерителя 13 на сброс накопителя 7 по выходу, чем и достигается повышение быстродействия, так как ошибки, выделяемые измерителем 13, не могут опустошить накопитель 7 по выходу, а значит задержать прохождение через элемент И 10 сигнала установки генераторного.блока 9-Первый же сигнал несовпадения.на выходе анализатора 3 подготавливает блок 5 управления к установке делителя 8 частоты. При появлении сигнала на выходе дешифратора 2-на выходах анализатора 3 и блока 5 управления формируются сигналы, устанавливающие делитель 8 частоты. Далее устройство переходит в режим контроля, в котором оно находится до тех пор,

пока на следующей анализируемой позиции не сформируется комбинация символов, отличная от синхрогруппы. После этого следующий сигнал на выходе дешифратора 2 установит делитель 8 частоты и устройство переходит в режим.контроля синхронизма на другой позиции входного группового сигнала. Таким образом осуществляется процесс поиска синхросигнала независимо от состояния накопителя 7 по выходу. При заполнении последнего сигнал с выхода делителя 8 частоты проходит, через элемент И 10 и устанавливает генераторный блок 9 в нулевое состояние. Если установка произошла по синхросигналу, то генераторный блок 9 будет сфазирован относительно входного группового сигнала. При этом накопитель 6 по входу заполняется, опустошает накопитель 7 по выходу и устанавливает высокий потенциал на выходе RS-триггера 11, элемент НЕТ 12 открывается и разрешает прохождение сигналов с выхода измерителя 13 искажения сигнала на сброс накопителя 7 по выходу чем и осуществляется надежное удержание синхронизма при сколь угодно

низкой достоверности входного ГРУППО

вого сигнала.

Положительный эффект от использования предлагаемого устройства заключается в повышении помехоустойчивости циклового синхронизма, а также имеет более высокую надежность удержания синхронизма при резких изменениях достоверности входного сигнала, например при грозовых разрядах или переключениях больших токов.

Формула изобретения

Устройство цикловой синхронизации по основному авт.св. if 661836, отличающееся тем, что, с целью повышения помехоустойчивости и быстродействия, введены элемент НЕТ и RS-триггер, первый и второй входы которого подключены к выходам соответствующих накопителей, а выход RS-триггера подсоединен к первому входу элемента НЕТ, второй вход которого подключен к выходу измерителя вероятности искажения сигналов, а выход элемента НЕТ подсоединен к дополнительному входу первого накопителя, при этом дополнительный выход генераторного оборудования подсоединен к дополнительному входу измерителя вероятности искажения сигнала.

Источники информации, принятые во внимание при экспертизе

Вхо9 тактовва частоты

ВмО групг о9ого сигнала

Авторы

Даты

1982-02-23—Публикация

1980-04-01—Подача