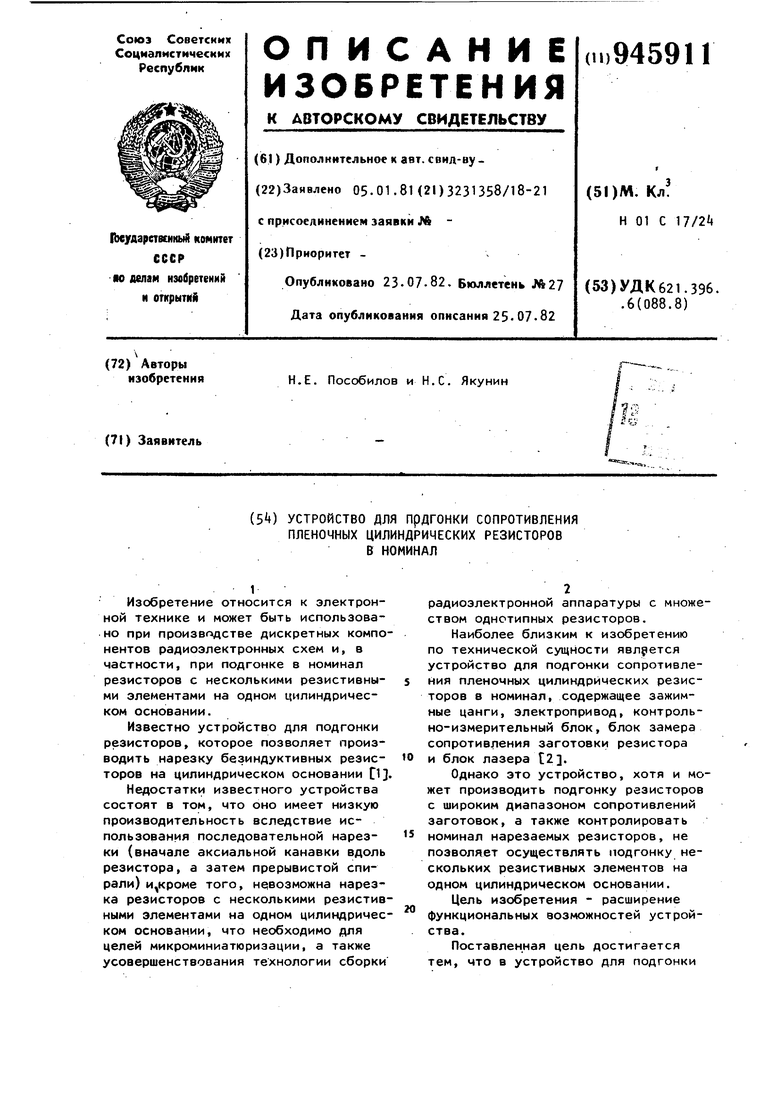

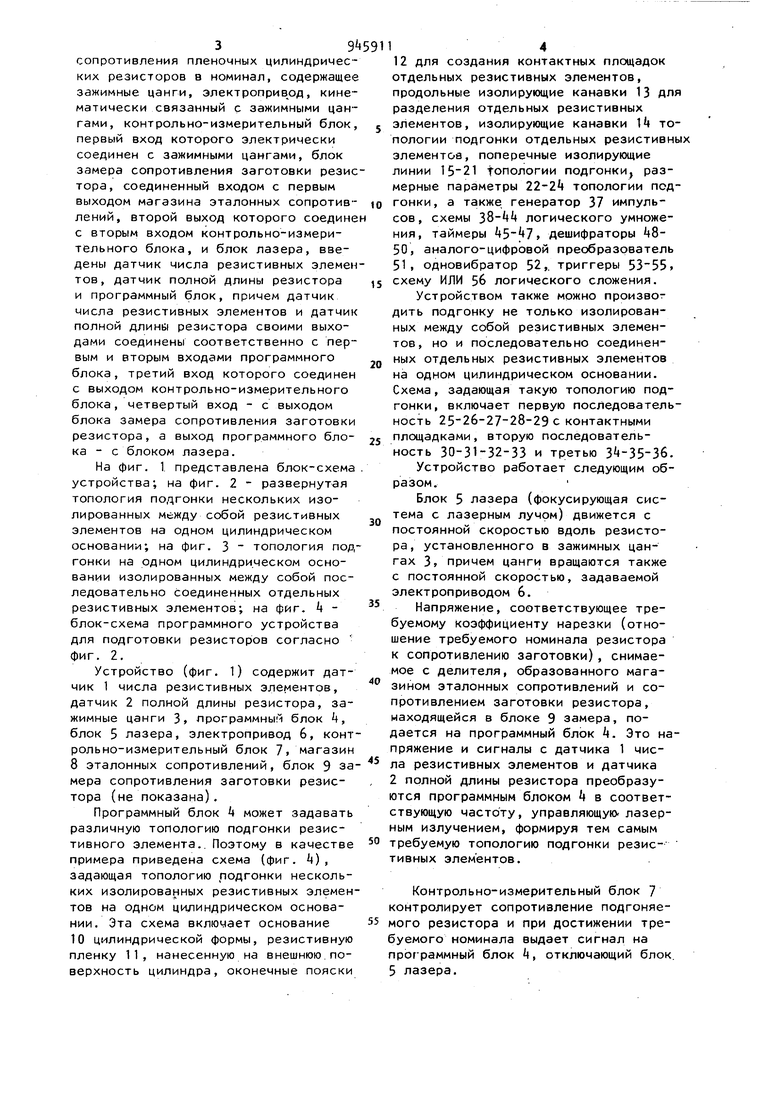

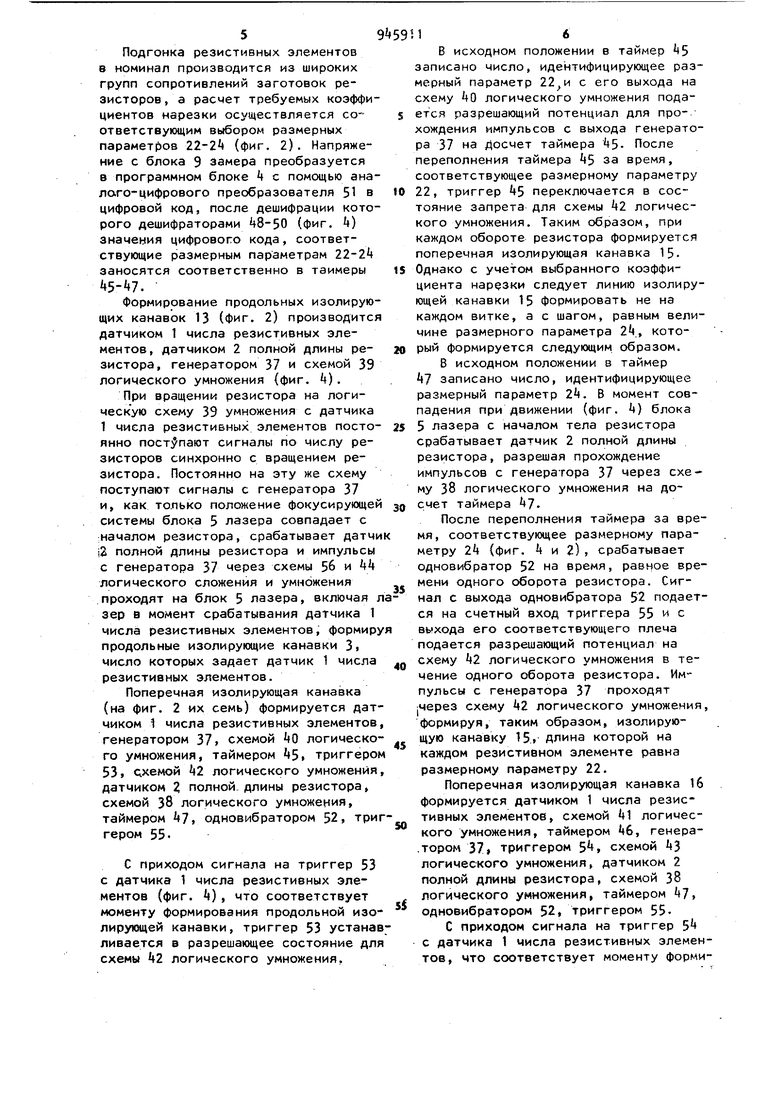

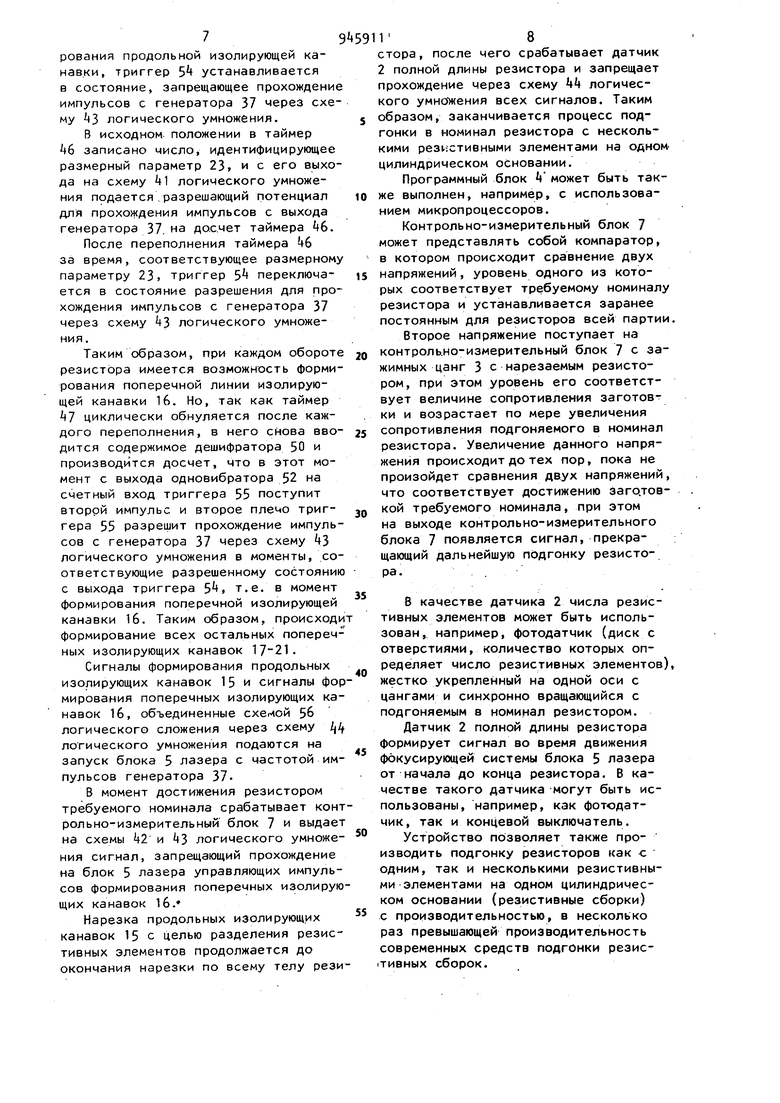

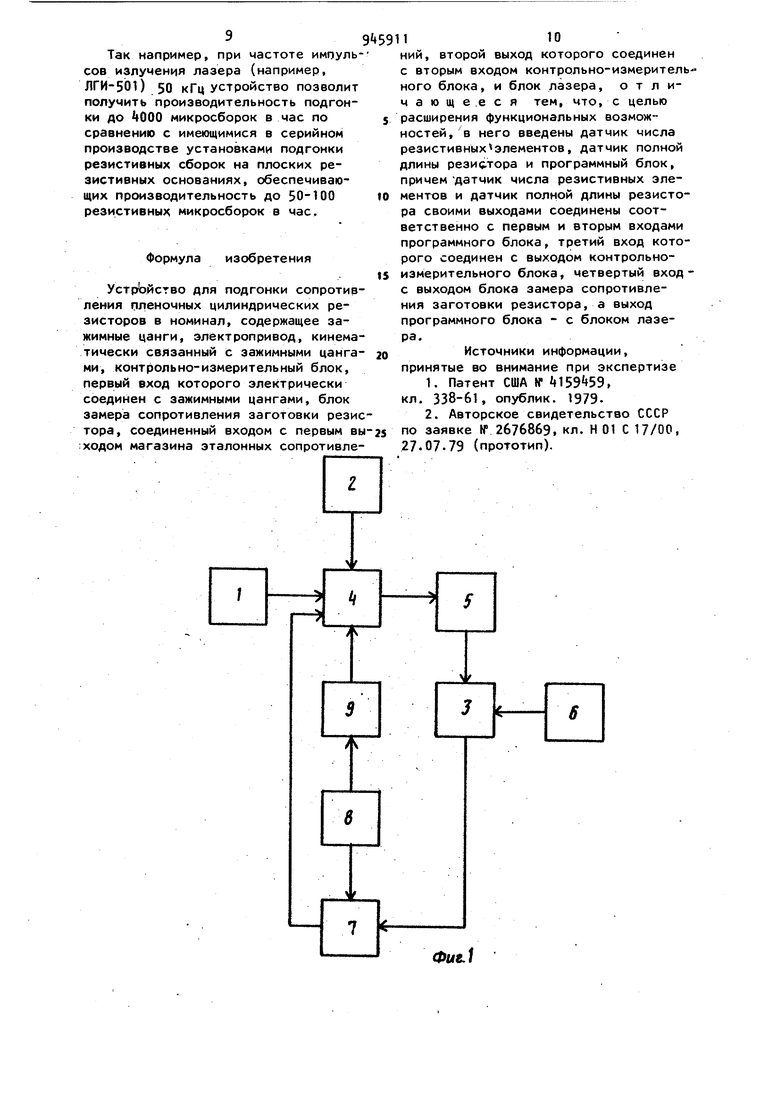

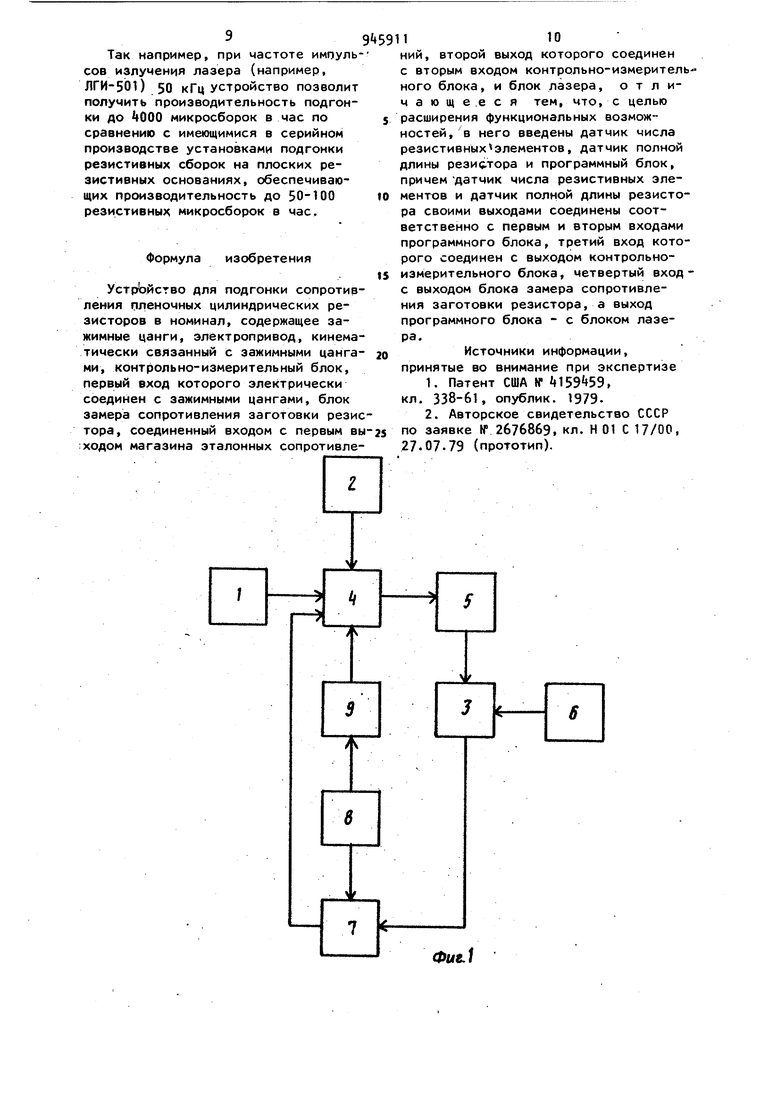

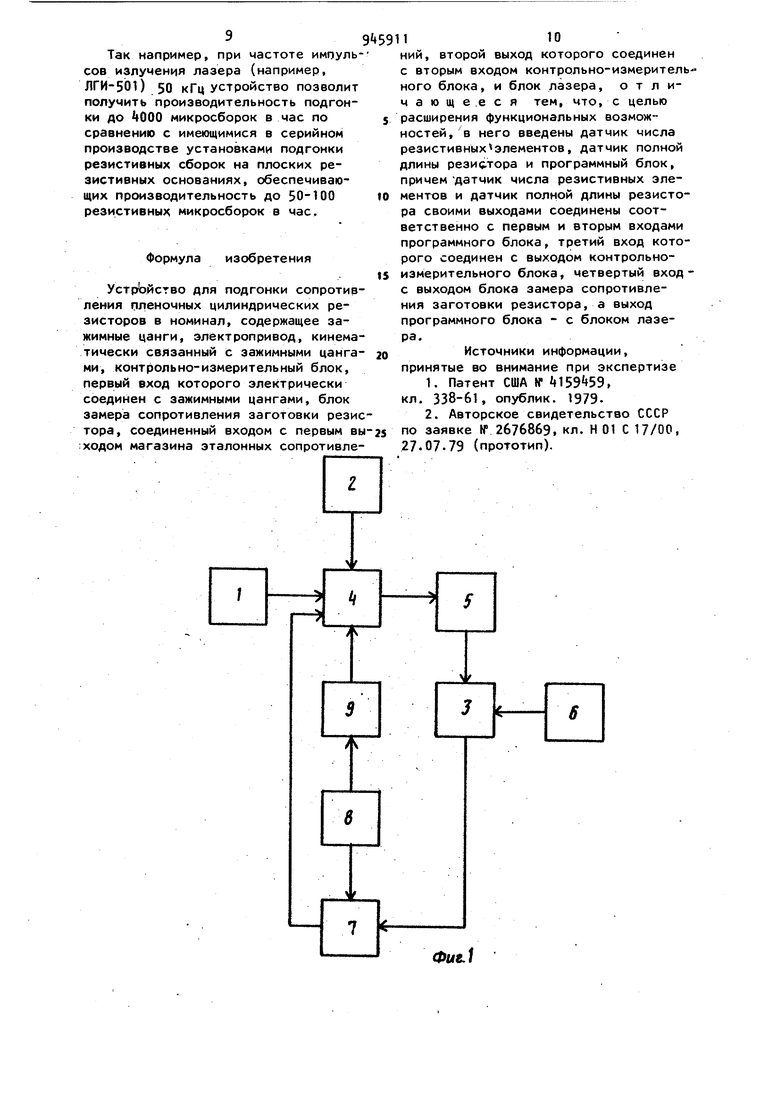

3 g сопротивления пленочных цилиндрических резисторов в номинал, содержащее зажимные цанги, электропривод, кинематически связанный с зажимными цангами, контрольно-измерительный блок, первый вход которого электрически соединен с зажимными цангами, блок замера сопротивления заготовки резис тора, соединенный входом с первым выходом магазина эталонных сопротивлений, второй выход которого соедине с вторым входом контрольно-измерительного блока, и блок лазера, введены датчик числа резистивных элемен тов, датчик полной длины резистора и программный блок, причем датчик числа резистивных элементов и датчик полной ДЛИНВ1 резистора своими выходами соединены соответственно с первым и вторым входами программного блока, третий вход которого соединен с выходом контрольно-измерительного блока, четвертый вход - с выходом блока замера сопротивления заготовки резистора, а выход программного блока - с блоком лазера. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - развернутая топология подгонки нескольких изолированных Между собой резистивных элементов на одном цилиндрическом основании; на фиг. 3 топология под гонки на одном цилиндрическом основании изолированных между собой последовательно соединенных отдельных резистивных элементов; на фиг. k блок-схема программного устройства для подготовки резисторов согласно фиг. 2, Устройство (фиг. 1) содержит датчик 1 числа резистивных элементов, датчик 2 полной длины резистора, зажимные цанги 3, Программный блок k, блок 5 лазера, электропривод 6, конт рольно-измерительный блок 7, магазин 8 эталонных сопротивлений, блок 9 за мера сопротивления заготовки резистора (не показана). Программный блок Ц может задавать различную топологию подгонки резистивного элемента.. Поэтому в качестве примера приведена схема (фиг. k), задающая топологию подгонки нескольких изолированных резистивных элементов на одном цилиндрическом основании. Эта схема включает основание 10 цилиндрической формы, резистивную пленку 11, нанесенную на внешнюю.поверхность цилиндра, оконечные пояски 4 12 для создания контактных площадок отдельных резистивных элементов, продольные изолирующие канавки 13 для разделения отдельных резистивных элементов, изолирующие канавки топологии подгонки отдельных резистивных элементов, поперечные изолирующие линии toпoлoгии подгонки, размерные параметры 22-2 топологии подгонки, а также генератор 37 импульсов , схемы 38-44 логического умножения, таймеры , дешифраторы k850,аналого-цифровой преобразователь 51,одновибратор 52,. триггеры 53-55 схему ИЛИ 5б логического сложения. Устройством также можно произвол дить подгонку не только изолированных между собой резистивных элементов, но и последовательно соединенных отдельных резистивных элементов на одном цилиндрическом основании. Схема, задающая такую топологию подгонки, включает первую последовательность 25-26-27-28-29 с контактными площадками, вторую последовательность 30-31-32-33 и третью 3 -35-36. Устройство работает следующим образом. Блок 5 лазера (фокусирующая система с лазерным лучом) движется с постоянной скоростью вдоль резистора, установленного в зажимных цангах 3, причем цанги вращаются также с постоянной скоростью, задаваемой электроприводом 6. Напряжение, соответствующее требуемому коэффициенту нарезки (отношение требуемого номинала резистора к сопротивлению заготовки), снимаемое с делителя, образованного магазином эталонных сопротивлений и сопротивлением заготовки резистора, находящейся в блоке 9 замера, подается на программный блок А. Это напряжение и сигналы с датчика 1 числа резистивных элементов и датчика 2 полной длины резистора преобразуются программным блоком Ц в соответствующую частоту, управляющую- лазерным излучением, формируя тем самым требуемую топологию подгонки резистивных элементов. Контрольно-измерительный блок 7 контролирует сопротивление подгоняемого резистора и при достижении требуемого номинала выдает сигнал на программный блок 4, отключающий блок. 5 лазера. 5 Подгонка резистивных элементов в номинал производится из широких групп сопротивлений заготовок резисторов , а расчет требуемых коэффициентов нарезки осуществляется соответствующим выбором размерных параметров ZZ-Z (фиг. 2). Напряжение с блока 9 замера преобразуется в программном блоке k с помощью аналаго-цифрового преобразователя 51 в цифровой код, после дешифрации которого дешифраторами 48-50 (фиг. ) значения цифрового кода, соответствующие размерным параметрам 22-2А заносятся соответственно в таймеры . Формирование продольных изолирующих канавок 13 (фиг. 2) производится датчиком 1 числа резистивных элементов, датчиком 2 полной длины резистора, генератором 37 и схемой 39 логического умножения (фиг. t). При вращении резистора на логическую схему 39 умножения с датчика 1 числа резистиБных элементов постоянно пост: пают сигналы по числу резисторов синхронно с вращением резистора. Постоянно на эту же схему поступают сигналы с генератора 37 и, как только положение фокусирующей системы блока 5 лазера совпадает с ;началом резистора, срабатывает датчи |2 полной длины резистора и импульсы с генератора 37 через схемы 5б и 44 логического сложения и умножения проходят на блок 5 лазера, включая л зер в момент срабатывания датчика 1 числа резистивных элементов, формиру продольные изолирующие канавки 3, число которых задает датчик 1 числа резистивных элементов. Поперечная изолирующая канавка (на фиг. 2 их семь) формируется датчиком 1 числа резистивных элементов генератором 37 схемой 40 логического умножения, таймером 45, триггером 53, схемой 42 логического умножения датчиком 2, полной- длины резистора, схемой 38 логического умножения, таймером 47, одновибратором 52, три гером 55С приходом сигнала на триггер 53 с датчика 1 числа резистивных элементов (фиг. 4), что соответствует моменту формирования продольной изо лирующей канавки, триггер 53 устанав ливается в разрешающее состояние для схемы 42 логического умножения. 6 В исходном положении в таймер 45 записано число, идентифицирующее размерный параметр с его выхода на схему 40 логического умножения подается разрешающий потенциал для про-, хождения импульсов с выхода генератора 37 на досчет таймера 45- После переполнения таймера 4$ за время, соответствующее размерному параметру 22, триггер 45 переключается в состояние запрета для схемы 42 логического умножения. Таким образом, при каждом обороте резистора формируется поперечная изолирующая канавка 15Однако с учетом выбранного коэффициента нарезки следует линию изолирующей канавки 15 формировать не на каждом витке, а с шагом, равным величине размерного параметра 24, который формируется следующим образом. В исходном положении в таймер 47 записано число, идентифицирующее размерный параметр 24. В момент совпадения при движении (фиг. 4) блока 5 лазера с началом тела резистора срабатывает датчик 2 полной длины резистора, разрешая прохождение импульсов с генератора 37 через схему 38 логического умножения на досчет таймера 47. После переполнения таймера за время, соответствующее размерному параметру 24 (фиг. 4 и 2), срабатывает одновибратор 52 на время, равное времени одного оборота резистора. Сигнал с выхода одновибратора 52 подается на счетный вход триггера 55 и с выхода его соответствующего плеча подается разрешающий потенциал на схему 42 логического умножения в течение одного оборота резистора. Импульсы с генератора 37 проходят ;через схему 42 логического умножения, формируя, таким образом, изолирующую канавку 15, длина которой на каждом резистивном элементе равна размерному параметру 22. Поперечная изолирующая канавка 1б формируется датчиком 1 числа резистивных элементов, схемой 41 логического умножения, таймером 46, генера.тором 37 триггером 5, схемой 43 логического умножения, датчиком 2 полной длины резистора, схемой 38 логического умножения, таймером 47, одновибратором 52, триггером 55С приходом сигнала на триггер 5 с датчика 1 числа резистивных элементов, что соответствует моменту форми9рования продольной изолирующей канавки, триггер устанавливается а состояние, запрещающее прохождение импульсов с генератора 37 через схему 3 логического умножения. В исходном положении в таймер 6 записано число, идентифицирующее размерный параметр 23, и с его выхода на схему 41 логического умножения подается.разрешающий потенциал для прохождения импульсов с выхода генератора 37. на до.с.чет таймера . После переполнения таймера k6 за время, соответствующее размерному параметру 23, триггер 5 переключается в состояние разрешения для прохождения импульсов с генератора 37 через схему 3 логического умножения. Таким образом, при каждом обороте резистора имеется возможность формирования поперечной линии изолирующей канавки 16. Но, так как таймер kj циклически обнуляется после каждого переполнения, в него снова вводится содержимое дешифратора 50 и производится досчет, что в этот момент с выхода одновибратора 52 на счетный вход триггера 55 поступит второй импульс и второе плечо триггера 55 разрешит прохождение импульсов с генератора 37 через схему k3 логического умножения в моменты, .соответствующие разрешенному состоянию с выхода триггера 5, т.е. в момент формирования поперечной изолирующей канавки 16. Таким образом, происходи формирование всех остальных поперечных изолирующих канавок . Сигналы формирования продольных изолирующих канавок 15 и сигналы фор мирования поперечных изолирующих канавок 16, объединенные схемой 5б логического сложения через схему логического умножения подаются на запуск блока 5 лазера с частотой импульсов генератора 37. В момент достижения резистором требуемого номинала срабатывает конт рольно-измерительный блок 7 и выдает на схемы k2 и 43 логического умноже ния сигнал, запрещающий прохождение на блок 5 лазера управляющих импульсов формирования поперечных изолирую щих канавок 16. Нарезка продольных изолирующих канавок 15 с целью разделения резистивных элементов продолжается до окончания нарезки по всему телу рези 8 стора, после чего срабатывает датчик 2 полной длины резистора и запрещает прохождение через схему kk логического умножения всех сигналов. Таким образом, заканчивается процесс подгонки в номинал резистора с несколькими резистивными элементами на одноМ цилиндрическом основании. Программный блок может быть также выполнен, например, с использованием микропроцессоров. Контрольно-измерительный блок 7 может представлять собой компаратор, в котором происходит сравнение двух напряжений, уровень одного из которых соответствует требуемому номиналу резистора и устанавливается заранее постоянным для резисторов всей партии. Второе напряжение поступает на контрольно-измерительный блок 7 с зажимных цанг 3 с нарезаемым резистором, при этом уровень его соответствует величине сопротивления заготовки и возрастает по мере увеличения сопротивления подгоняемого в номинал резистора. Увеличение данного напряжения происходит до тех пор, пока не произойдет сравнения двух напряжений, что соответствует достижению заго.товкой требуемого номинала, при этом на выходе контрольно-измерительного блока 7 появляется сигнал, прекращающий дальнейшую подгонку резистора. . В качестве датчика 2 числа резистивных элементов может быть использован, например, фотодатчик (диск с отверстиями, количество которых определяет число резистивных элементов), жестко укрепленный на одной оси с цангами и синхронно вращающийся с подгоняемым в номинал резистором. Датчик 2 полной длины резистора формирует сигнал во время движения фокусирующей системы блока 5 лазера от качала до конца резистора. В качестве такого датчика могут быть использованы, например, как фотодатчик, так и концевой выключатель. Устройство позволяет также производить подгонку резисторов как с одним, так и несколькими резистивными элементами на одном цилиндрическом основании (резистивные сборки) с производительностью, в несколько раз превышающей производительность современных средств подгонки резисТИВНЫХ сборок. Так например, при частоте импульсов излучения лазера (например, ЛГИ-501) 50 кГц устройство позволит получить производительность подгонки до tOOO микросборок в час по сравнению с имеющимися в серийном производстве установками подгонки резистивных сборок на плоских резистивных основаниях, обеспечивающих производительность до 50-100 резистивных микросборок в час. Формула изобретения УстрЬйство для подгонки сопротивления пленочных цилиндрических резисторов в номинал, содержащее зажимные цанги, электропривод, кинематически связанный с зажимными цангами, контрольно-измерительный блок, первый вход которого электрически соединен с зажимными цангами, блок замера сопротивления заготовки резис тора, соединенный входом с первым вы ;ходом магазина эталонных сопротивлений, второй выход которого соединен с вторым входом контрольно-измерительного блока, и блок лазера, о т л ичающе.еся тем, что, с целью расширения функциональных возможностей, в него введены датчик числа резистивных элементов, датчик полной длины резистора и программный блок, причем датчик числа резистивных элементов и датчик полной длины резистора своими выходами соединены соответственно с первым и вторым входами программного блока, третий вход которого соединен с выходом контрольноизмерительного блока, четвертый входс выходом блока замера сопротивления заготовки резистора, а выход программного блока - с блоком лазера. Источники информации, принятые во внимание при экспертизе 1.Патент США № , кл. 338-61, опублик. 1979. 2.Авторское свидетельство СССР по заявке №2676869, кл. Н 01 С 17/00, 27.07.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подгонки сопротивления пленочных резисторов в номинал | 1981 |

|

SU997106A1 |

| Устройство для подгонки сопротивления пленочных резисторов | 1982 |

|

SU1048524A1 |

| Устройство подгонки резисторов в номинал | 1980 |

|

SU920855A1 |

| Устройство для подгонки сопротивлений пленочных резисторов | 1978 |

|

SU788079A1 |

| Способ подгонки цилиндрических пленочных резисторов | 1982 |

|

SU1038970A1 |

| Устройство для подгонки сопротивления пленочных цилиндрических резисторов | 1980 |

|

SU983765A1 |

| Устройство для подгонки пленочных цилиндрических резисторов | 1976 |

|

SU627546A2 |

| Устройство для подгонки пленочных цилиндрических резисторов | 1975 |

|

SU543992A1 |

| Устройство для подгонки пленочных цилиндрических резисторов в номинал | 1980 |

|

SU943865A1 |

| Цилиндрический резистор | 1983 |

|

SU1088077A1 |

Фие.}

п n

ft

п. 18 13 iO/ 21

Т

п

а

/

12

//

П П 11 Н Фие.1

2S П

19 30

32

3it 36

26

и

Л

5J

35

т

Првграммнов устройство

ФигЛ

Авторы

Даты

1982-07-23—Публикация

1981-01-05—Подача