Изобретение относится к вычислительной технике и может быть использовано для построения преобразователей кодов как дробных, так и целых

чисел.

ч

Цель изобретения - повьшение быстродействия преобразователя за счет преобразования одного двоично-десятичного разряда за один такт.

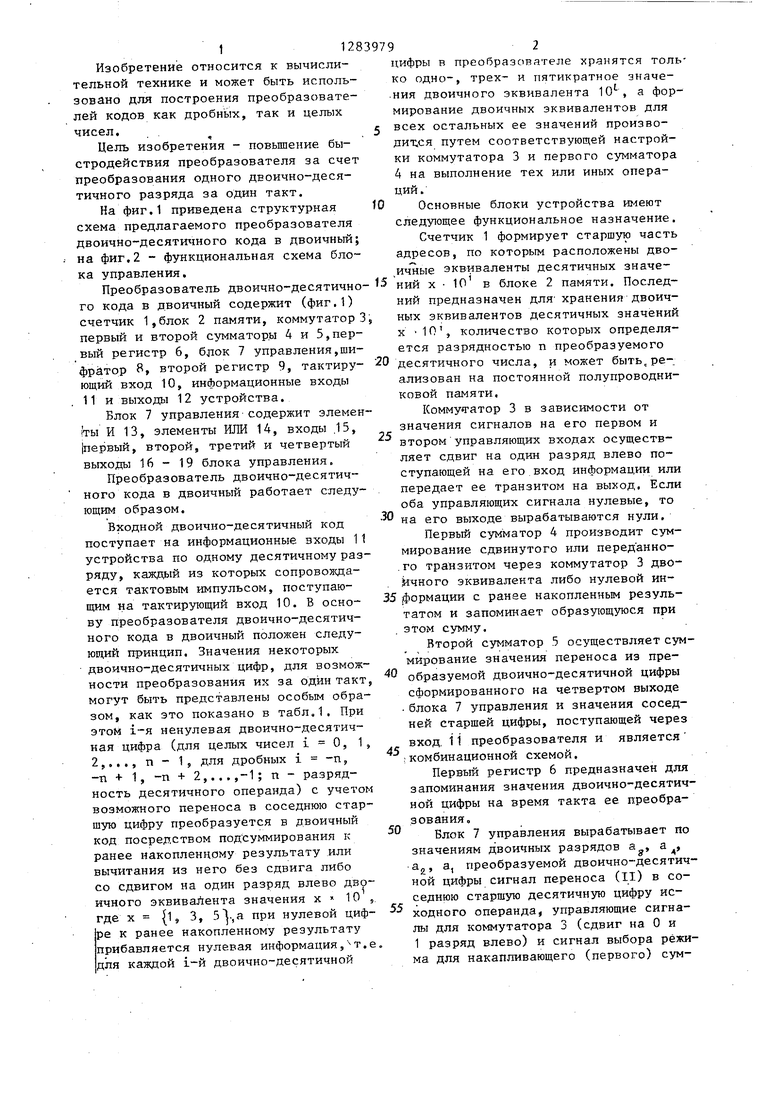

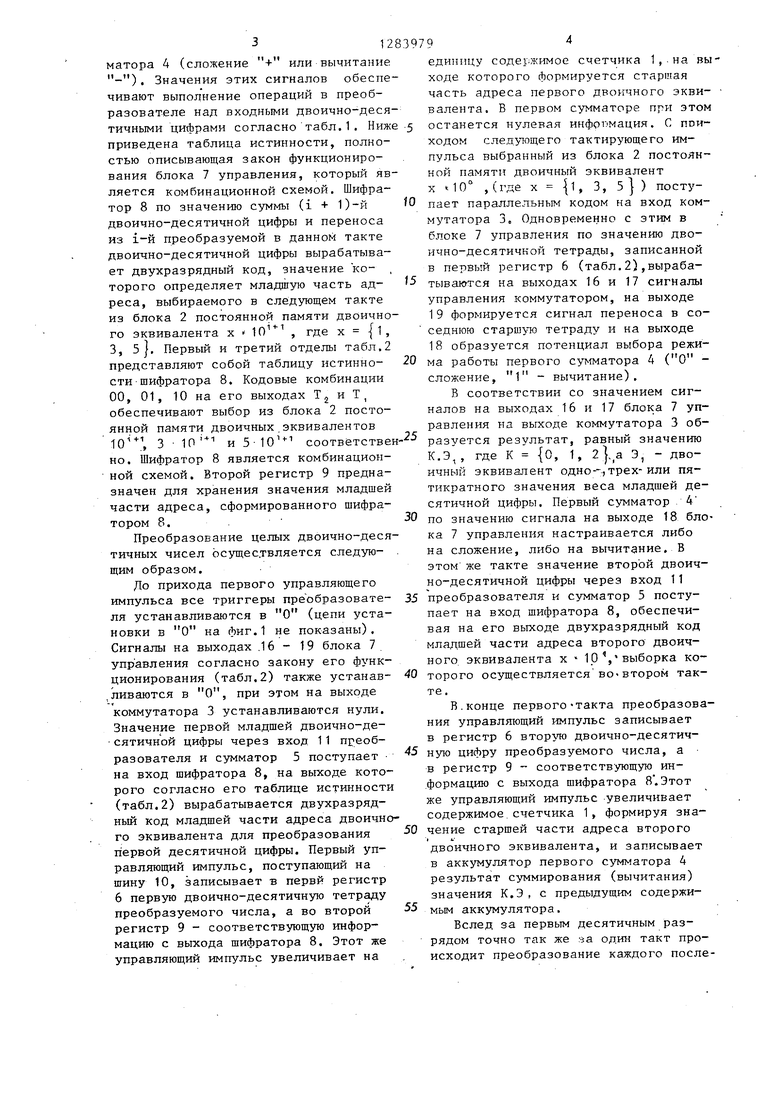

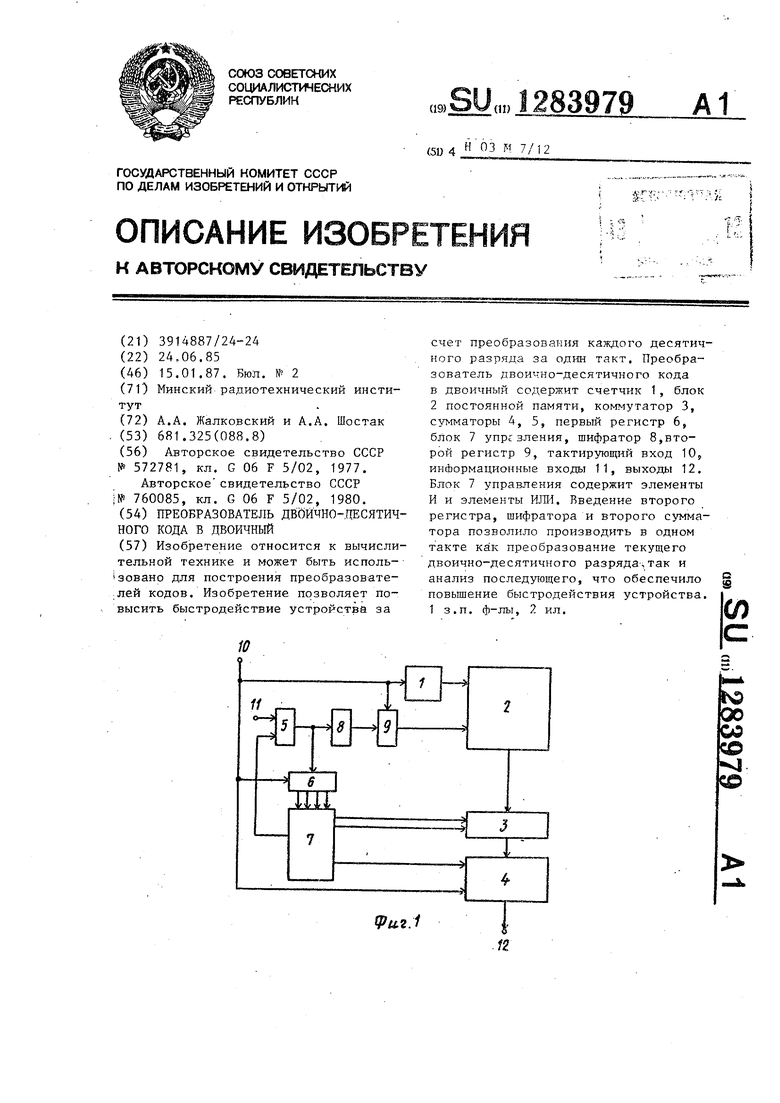

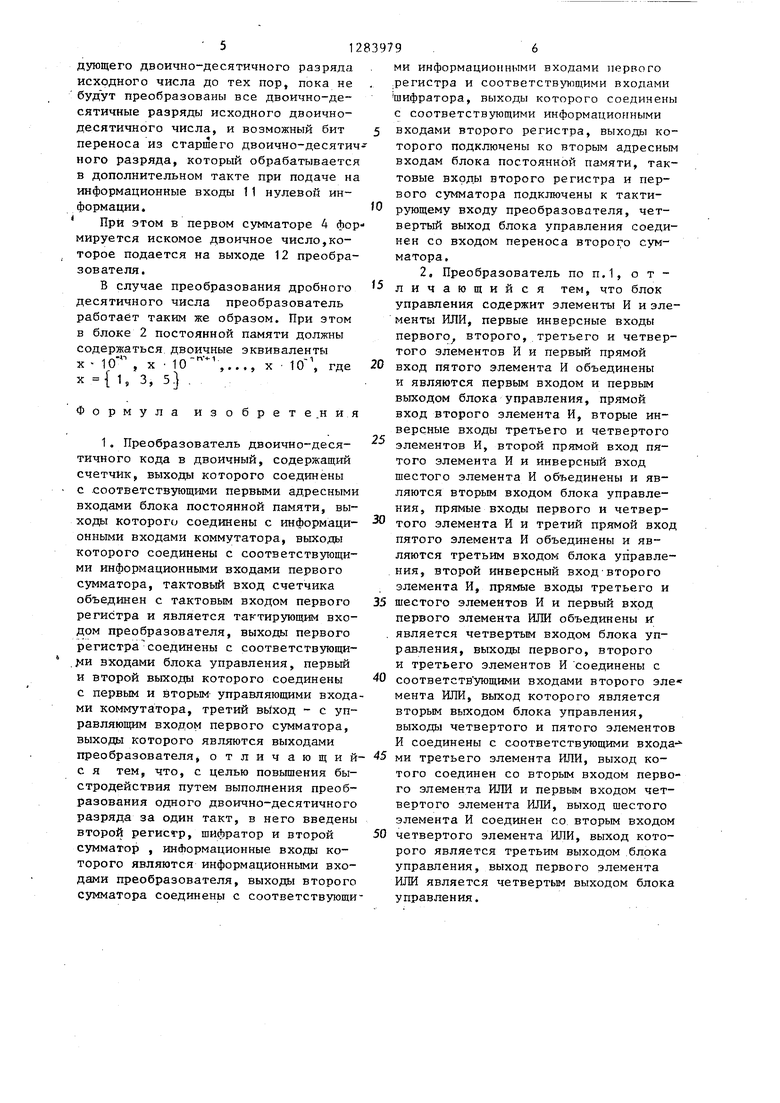

На фиг.1 приведена структурная схема предлагаемого преобразователя двоично-десятичного кода в двоичный; на фиг.2 - функциональная схема блока управления.

10

цифры в преобразователе хранятся толь ко одно-, трех- и пятикратное эначе- .ния двоичного эквивалента Ю -, а формирование двоичных эквивалентов для всех остальных ее значений произво- ди1;ся путем соответствующей настройки коммутатора 3 и первого сумматора 4 на выполнение тех или иных операций.

Основные блоки устройства имеют следующее функциональное назначение.

Счетчик 1 формирует старшую часть адресов, по которым расположены дво- ич ные эквиваленты десятичных значеПреобразователь двоично-десятично- ний х 10 в блоке 2 памяти. Последго кода в двоичный содержит (фиг.1) счетчик 1,блок 2 памяти, коммутатор 3 первый и второй сумматоры 4 и 5,первый регистр 6, блок 7 управления,ши- фрйтор В, второй регистр 9, тактирующий вход 10, информационные входы 11 и выходы 12 устройства.

Блок 7 управления-содержит элемен- Ьы И 13, элементы ИЛИ 14, входы .15, первый, второй, третий и четвертый выходы 16 - 19 блока управления.

Преобразователь двоично-десятичного кода в двоичный работает следующим образом.

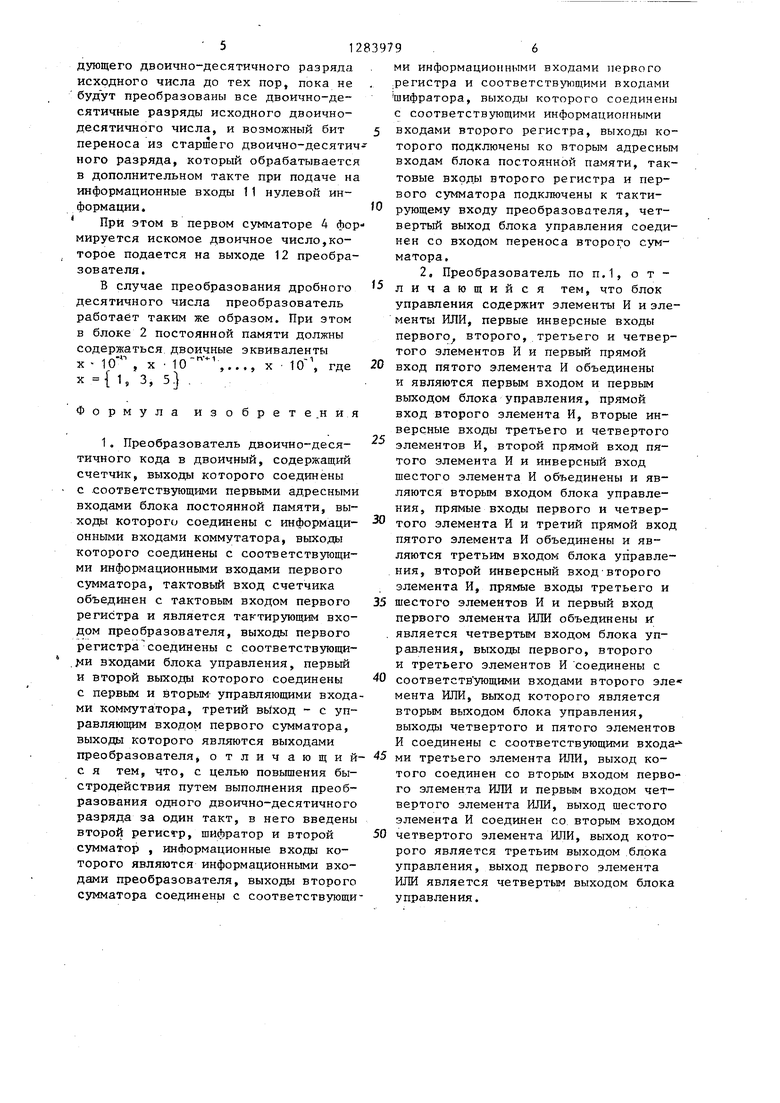

Входной двоично-десятичный код поступает на информационные входы 11 устройства по одному десятичному разряду, каждый из которых сопровождается тактовым импульсом, поступающим на тактирующий вход Ю. В основу преобразователя двоично-десятичного кода в двоичный положен следующий принцип. Значения некоторых двоично-десятичных цифр, для возможности преобразования их за один такт, могут быть представлены особым образом, как это показано в табл.1. При этом i-я ненулевая двоично-десятичная цифра (для целых чисел , 1, 2,..., п - 1, для дробных i -п, -п + 1, -п + 2,...,-1; п - разрядность десятичного операнда) с учетом возможного переноса в соседнюю старшую цифру преобразуется в двоичный код посредством под суммирования к ранее накопленному результату .или вычитания из него без сдвига либо со сдвигом на один разряд влево двоичного эквивалента значения х 10 , где X (1, 3, 5Y,a при нулевой цифре к ранее накопленному результату прибавляется нулевая информация, т. е для каждой i-й двоично-десятичной

цифры в преобразователе хранятся только одно-, трех- и пятикратное эначе- .ния двоичного эквивалента Ю -, а формирование двоичных эквивалентов для всех остальных ее значений произво- ди1;ся путем соответствующей настройки коммутатора 3 и первого сумматора 4 на выполнение тех или иных операций.

Основные блоки устройства имеют следующее функциональное назначение.

Счетчик 1 формирует старшую часть адресов, по которым расположены дво- ич ные эквиваленты десятичных значе0

5

0

ний предназначен для хранения двоичных эквивалентов десятичных значений X 10 , количество которых определяется разрядностью п преобразуемого десятичного числа, и может быть,реализован на постоянной полупроводниковой памяти.

Комму гатор 3 в зависимости от значения сигналов на его первом и втором управляющих входах осуществляет сдвиг на один разряд влево поступающей на его вход информации или передает ее транзитом на выход. Если оба управляющих сигнала нулевые, то на его выходе вырабатываются нули.

Первый сумматор 4 производит суммирование сдвинутого или перед анно- .го транзитом через коммутатор 3 дво- lt4Horo эквивалента либо нулевой ин- 5 формации с ранее накопленным результатом и запоминает образующуюся при этом сумму.

Второй сумматор 5 осуществляет суммирование значенрш переноса из пре- 0 образуемой двоично-десятичной цифры сформированного на четвертом выходе блока 7 управления и значения соседней старшей цифры, поступающей через вход, 11 преобразователя и является комбинационной схемой.

Первый регистр 6 предназначен для запоминания значения двоично-десятичной цифры на время такта ее преобразования.

Блок 7 управления вырабатывает по значениям двоичных разрядов а , а , ар, а, преобразуемой двоично-десятич5

0

55

ной цифры сигнал переноса (II) в соседнюю старшую десятичную цифру исходного операнда, управляющие сигналы для коммутатора 3 (сдвиг на О и 1 разряд влево) и сигнал выбора режима для накапливающего (первого)

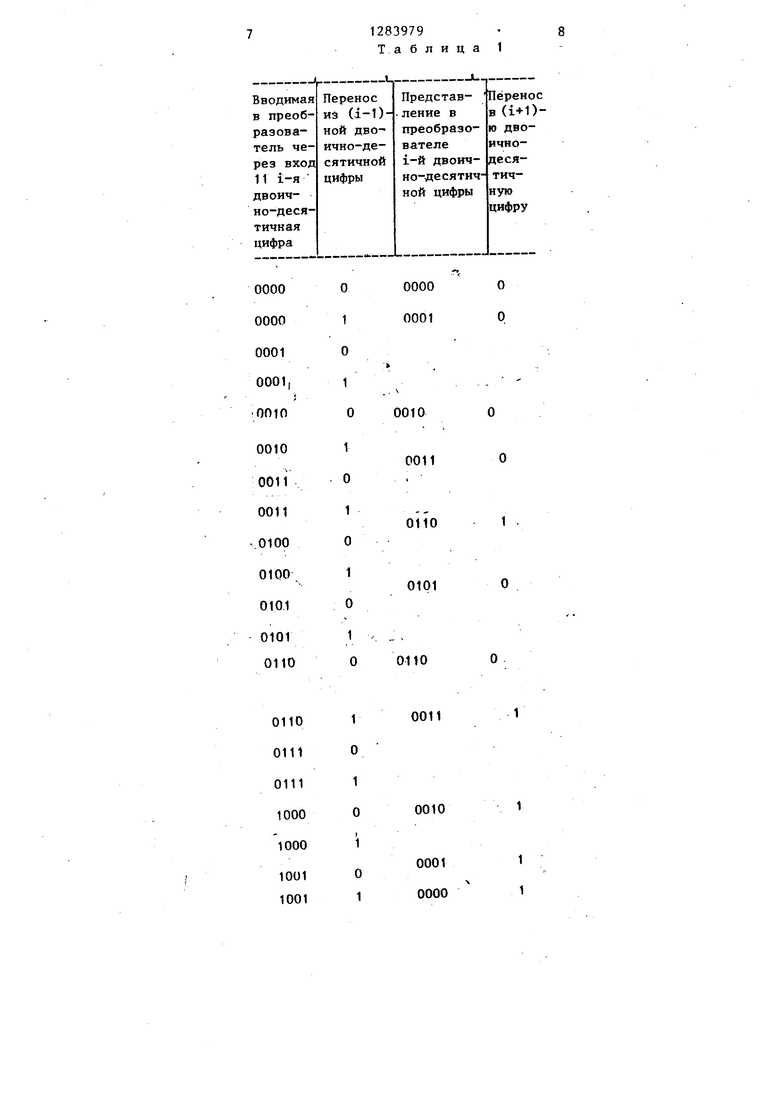

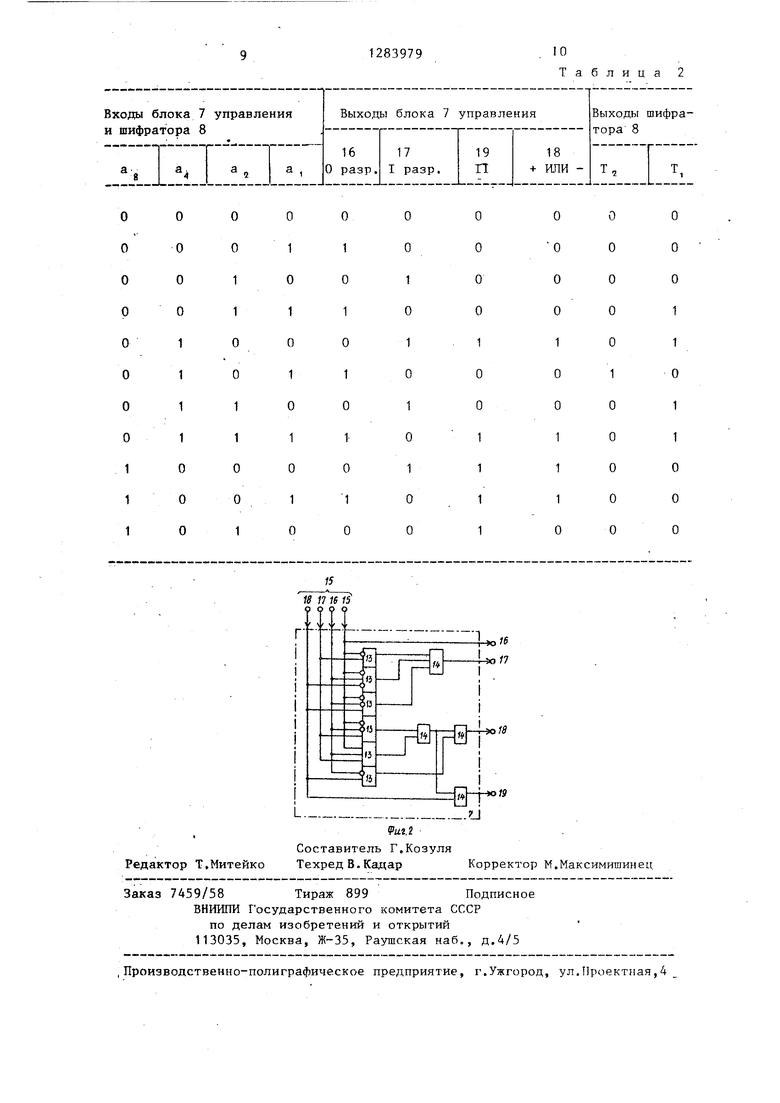

матора 4 (сложение + или вычитание -). Значения этих сигналов обеспечивают выполнение операций в преобразователе над входными двоично-десятичными цифрами согласно табл.1. Ниж приведена таблица истинности, полностью описывающая закон функционирования блока 7 управления, который является комбинационной схемой. Шифратор 8 по значению суммы (i + 1)-й двоично-десятичной цифры и переноса из i-й преобразуемой в данном такте двоично-десятичной цифры вырабатывает двухразрядный код, значение которого определяет младшую часть ад- реса, выбираемого в следующем такте из блока 2 постоянной памяти двоичного эквивалента х 10 , где х |l, 3, 5j. Первый и третий отделы табл.2 представляют собой таблицу истинно- стишифратора 8. Кодовые комбинации 00, 01, 10 на его выходах Т и Т, обеспечивают выбор из блока 2 постоянной памяти двоичных .эквивалентов fO , 3 и 5-10 соответствен но. Шифратор 8 является комбинационной схемой. Второй регистр 9 предназначен для хранения значения младшей части адреса, сформированного шифратором 8. .

Преобразование целых двоично-десятичных чисел осуществляется следую- щим образом.

До прихода первого управляющего импульса все триггеры преобразовате- ля устанавливаются в О (цепи установки в О на фиг.1 не показаны). Сигналы на выходах .16 - 19 блока 7 управления согласно закону его функционирования (табл.2) также устанав-

,ливаются в О, при этом на выходе коммутатора 3 устанавливаются нули. Значение первой младшей двоично-десятичной цифры через вход 11 преоб

разователя и сумматор 5 поступает

на вход шифратора 8, на выходе которого согласно его таблице истинности (табл.2) вырабатывается двухразрядный код младшей части адреса двоичного эквивалента для преобразования первой десятичной цифры. Первый управляющий импульс, поступающий на шину 10, записывает в первй регистр 6 первую двоично-десятичную тетраду преобразуемого числа, а во второй регистр 9 - соответствующую информацию с вьгеода шифратора 8. Этот же управляющий импульс увеличивает на

5 0 5 20 25 -30

35 0

5

5

794

единицу содержимое счетчика 1,.на выходе которого формируется старшая часть адреса первого двоичного эквивалента. В первом сумматоре при этом останется нулевая информация. С пои- ходом следующего тактирующего импульса выбранный из блока 2 постоянной памяти двоичный эквивалент X И0° ,(где X |l, 3, 5 ) поступает параллельным кодом на вход коммутатора Зе Одновременно с этим в блоке 7 управления по значению дво- ично-десятичкой тетрады, записанной в первый регистр 6 (табл.2),вырабатываются на выходах 16 и 17 сигналы управления коммутатором, на выходе 19 формируется сигнал переноса в соседнюю старш то тетраду и на выходе 18 образуется потенциал выбора режима работы первого cyNfMaTopa 4 (О - сложение, 1 - вычитание).

В соответствии со значением сигналов на выходах 16 и 17 блока 7 управления на выходе коммутатора 3 образуется результат, равный значению К.Э,, где К {о, 1, 2}.а Э, - двоичный эквивалент одно-,трех-или пятикратного значения веса младшей десятичной цифры. Первый сумматор 4 по значению сигнала на выходе 18 блока 7 управления настраивается либо на сложение, либо на вычитание. В этом же такте значение второй двоично-десятичной цифры через вход 11 преобразователя и сумматор 5 поступает на вход шифратора 8, обеспечивая на его выходе двухразрядный код младшей части адреса второго двоичного эквивалента х 10% выборка которого осуществляется во-втором такте .

В.конце первого-такта преобразования управляющий импульс записывает в регистр 6 вторую двоично-десятичную цифру преобразуемого числа, а в регистр 9 соответствующую ин- .формацию с выхода шифратора 8. Этот же управляющий импульс увеличивает содержимое.счетчика 1, формируя значение старшей части адреса второго

| .

двоичного эквивалента, и записывает в аккумулятор первого сумматора 4 результат суммирования (вычитания) значения К.Э , с предыдущим содержимым аккумулятора.

Вслед за первым десятичным разрядом точно так же за один такт происходит преобразование каждого последующего двоично-десятичного разряда исходного числа до тех пор, пока не будут преобразованы все двоично-десятичные разряды исходного двоично- десятичного числа, и возможный бит переноса из старшего двоично-десятичного разряда, который обрабатывается в дополнительном такте при подаче на информационные входы 11 нулевой информации.

При этом в первом сумматоре 4 формируется искомое двоичное число,которое подается на выходе 12 преобразователя.

В случае преобразования дробного десятичного числа преобразователь работает таким же образом. При этом в блоке 2 постоянной памяти должны

эквиваленты

- 1

., X 10 , где

брете.ния

1. Преобразователь двоично-десятичного кода в двоичный, содержащий счетчик, выходы которого соединены с соответствующими первыми адресными входами блока постоянной памяти, выходы которого соединены с информационными входами коммутатора, выходы которого соединены с соответствующими информационными входами первого сумматора, тактовый вход счетчика объединен с тактовым входом первого регистра и является тактирующим входом преобразователя, выходы первого регистра соединены с соответствующи- . 1И входами блока управления, первый и второй выходы которого соединены с первым и вторым управляющими входами коммутатора, третий вь1ход - с управляющим входом первого сумматора, выходы которого являются выходами преобразователя, отличающий- с я тем, что, с целью повьппения быстродействия путем выполнения преобразования одного двоично-десятичного разряда за один такт, в него введены второй регистр, шифратор и второй сумматор , инАормационные входы которого являются информационными входами преобразователя, выходы второго сумматора соединены с соответствующи

10

15

20

-

25

839796

ми информационными входами первого .регистра и соответствующими входами шифратора, выходы которого соединены с соответствующими информационными 5 входами второго регистра, выходы которого подключены ко вторым адресным входам блока постоянной памяти, тактовые входы второго регистра и первого сумматора подключены к тактирующему входу преобразователя, четвертый выход блока управления соединен со входом переноса второго сумматора.

2, Преобразователь по п.1, о т - личающийся тем, что блок управления содержит элементы И и элементы ИЛИ, первые инверсные входы первого второго, третьего и четвертого элементов И и первый прямой вход пятого элемента И объединены и являются первым входом и первым выходом блока управления, прямой вход второго элемента И, вторые инверсные входы третьего и четвертого элементов И, второй прямой вход пятого элемента И и инверсный вход шестого элемента И объединены и являются вторым входом блока управления, прямые входы первого и четвертого элемента И и третий прямой вход пятого элемента И объединены и являются третьим входом блока управления, второй инверсный вход-второго элемента И, прямые входы третьего и шестого элементов И и первый вход первого элемента ИЛИ объединены и; является четвертым входом блока управления, выходы первого, второго и третьего элементов И соединены с соответств ующими входами второго эле мента Или, выход которого является вторым выходом блока управления, выходы четвертого и пятого элементов И соединены с соответствующими входа- ми третьего элемента ИЛИ, выход ко- того соединен со вторым входом первого элемента ШШ и первым входом четвертого элемента ИЛИ, выход шестого элемента И соединен со вторым входом четвертого элемента ИЛИ, выход которого является третьим выходом блока управления, выход первого элемента ИЛИ является четвертым выходом блока управления.

30

35

40

45

50

0110

0110 0111 0111 1000 1000

1001 1001

О

0110

О

ООП

0010 1

0001 1 0000 1

1

1

1

о

о

о

о

1

1

1

1

о

о

о

о

о

1

1

о

о

1

1

о

о

1

о

1

о

1

о

1

о

1

о

1

о

о 1

о

1

о

1

о

1

о

1

о

о о о о 1

о о 1 1

о

О

о о 1 о о 1 1 1 о

о о о о о 1

о о о о о

о о о 1 1 о 1 1

о о о

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

Изобретение относится к вычислительной технике и может быть исполь зовано для построения преобразователей кодов. Изобретение позволяет повысить быстродействие устройства за счет преобразовакия каждого десятичного разряда за один такт. Преобразователь двоично-десятичного кода в двоичный содержит счетчик 1, блок 2 постоянной памяти, коммутатор 3, сумматоры 4, 5, первый регистр 6, блок 7 управления, шифратор 8,второй регистр 9, тактирующий вход 10, инсЬормационные входы 11, выходы 12. Блок 7 управления содержит элементы И и элементы ИЛ-. Введение второго регистра, шифратора и второго сумматора позволило производить в одном такте как преобразование текущего двоично-десятичного разряда,так и анализ последующего, что обеспечило повышение быстродействия устройства. 1 3.п. ф-лы, 2 ил. I (Л ю 00 со (Г) fpu.2.i

Редактор Т.Митейко

1и

Put.t

Составитель Г.Козуля Техред В.Кадар Корректор М.Максимишинец

Заказ 7459/58 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д.4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 760085, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-24—Подача