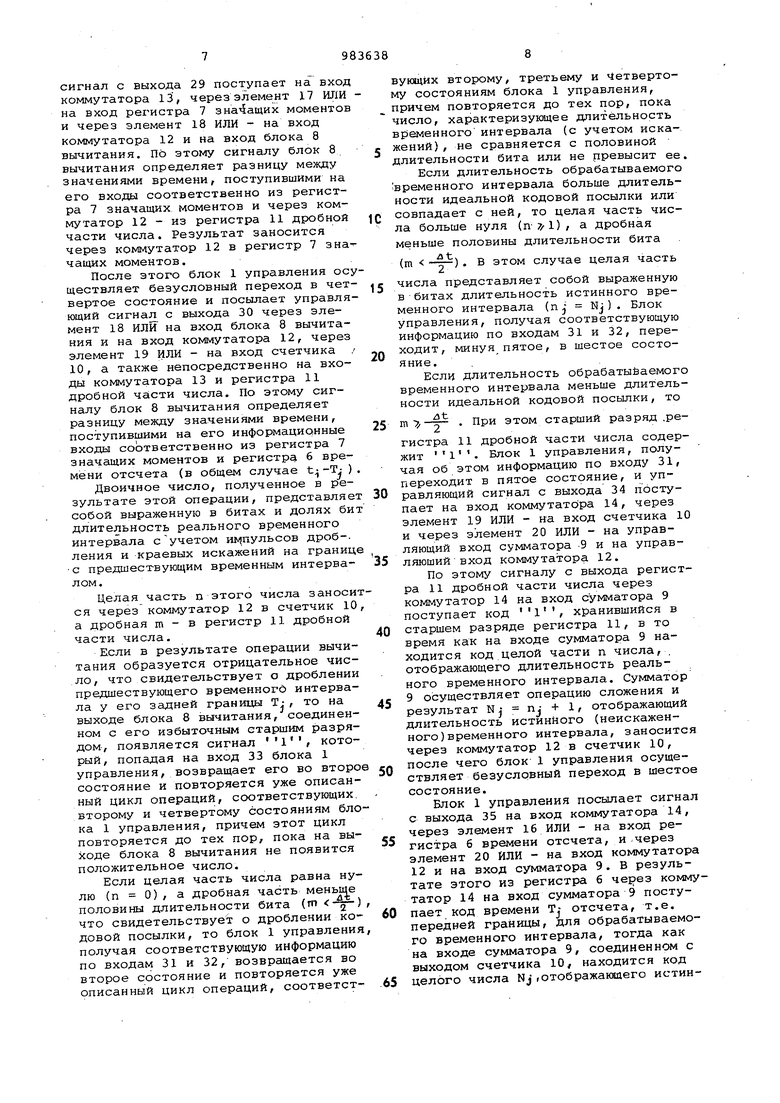

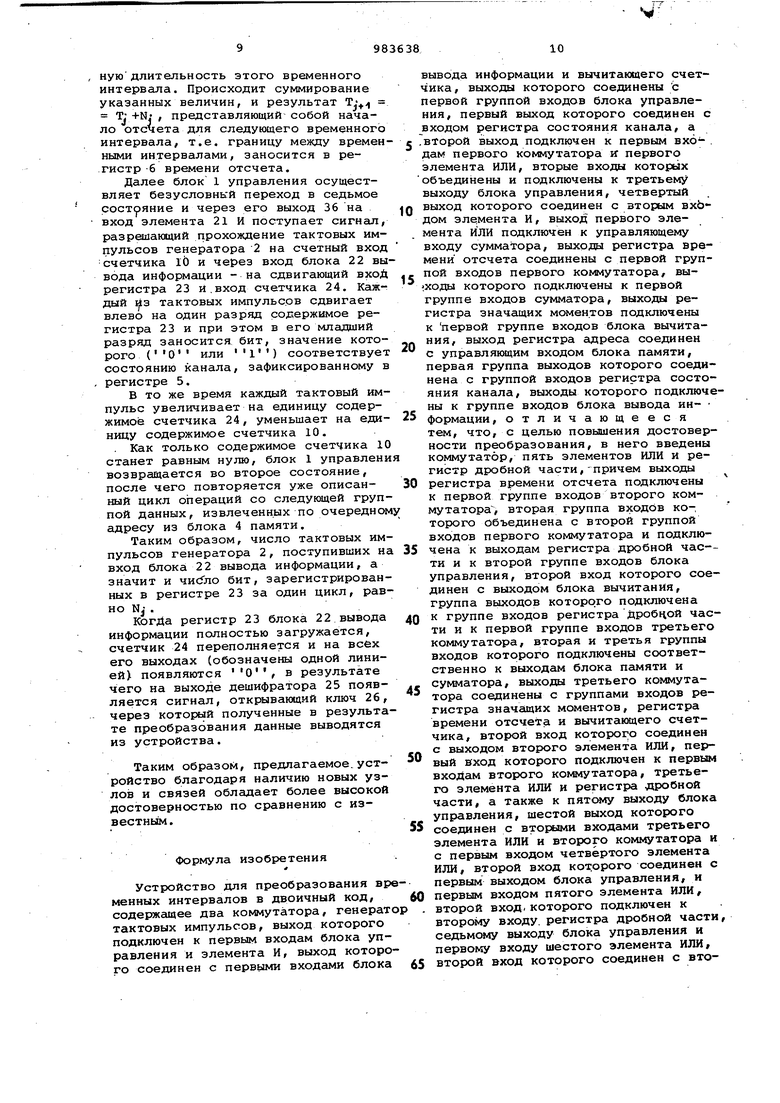

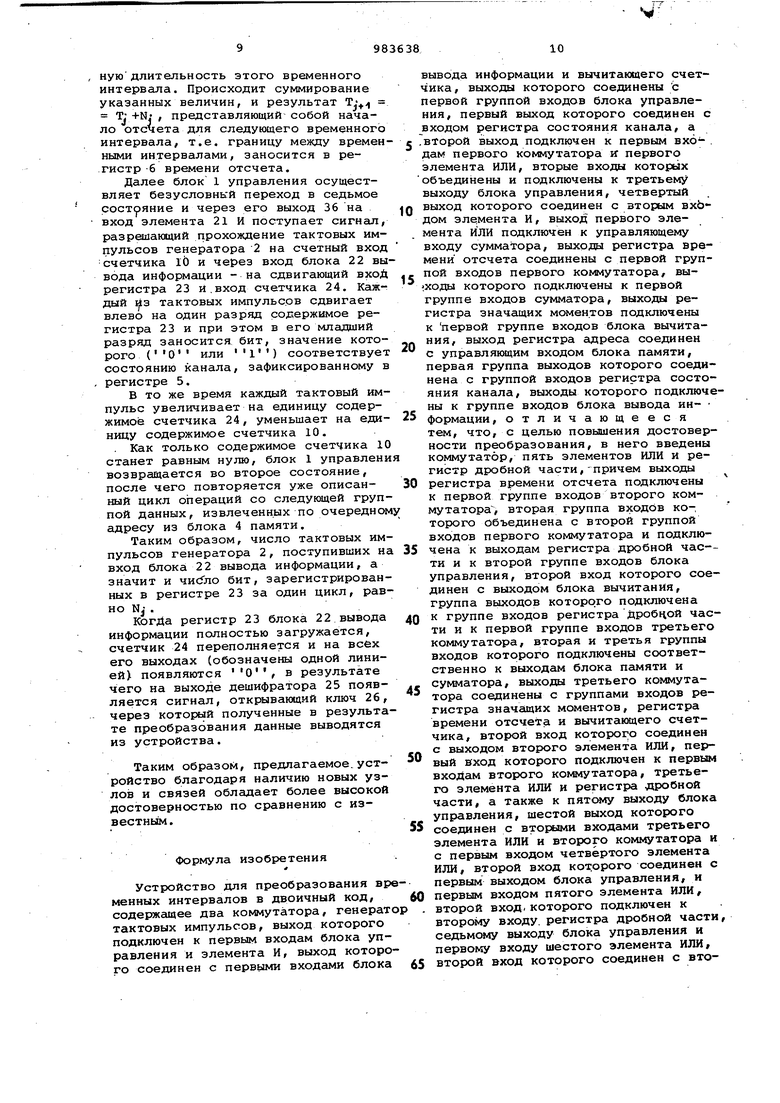

который содержит разряды для записи кода состояния канала - регистр состояния канала, и разряды для записи кода времени изменения состояния канала - регистр значащих моментов, выход которого соединен с одним из входов блока вычитания, регистр времени отсчета, сумматор и вычитающий счетчик, выход которого соединен с вторым входом блока управления, бло вывода информации, два коммутатора, элемент ИЛИ и элемент И 3. Недостатком этого устройства является низкая достоверность преобразования, обусловленная низкой помехозащищенностью устройства. Целью изобретения является повышение достоверности преобразования. .Поставленная цель достигается тем что в устройство для преобразования временных интервалов в двоичный код содержащее два коммутатора, генератор тактовых импульсов, выход которого подключен к первым входам блока управления и элемента И, выход которого соединен с первыми входами блока вывода информации и вычитающе го счетчика, выходы которого соединены с первой группой входов блока управления, первый выход которого соединен с входом регистра состояния канала, а второй выход подключе к первым входам первого коммутатора и первого элемента ИЛИ, вторые входы которых объединены и подключенык третьему выходу блока управления, четвертый выход которого соединен с вторым входом элемента И, выход пер вого элемента ИЛИ подключен к управ ляющему входу сумматора, выходы ген ратора времени отсчета соединены с первой группой входов первого комму татора, выходы которого подключены к первой группе входов сумматора, выходы регистра значащих моментов подключены к первой группе входов блока вычитания, выход регистра адреса соединен с управляющим входом блока памяти, первая группа выходов которого соединена с группой входов регистра состояния канала, выходы которого подключены к входов блока вывода информации, введены коммутатор, пять элементов ИЛИ и ре гистр дробной части, причем выходы регистра времени отсчета подключены к первой группе входов второго комму татора, вторая группа входов которого объединена с второй группой входов первого коммутатора и подключена к выходам регистра дробной части и второй группе входов блока управления, второй вход которого соединен с выходом блока вычитания, группа выходов которого подключена к группе входов регистра дробной части и к первой группе входов треть его коммутатора,вторая и третья группы .входов которого подключены соответственно к выходам блока памяти и сумматора, выходы третьего коммутатора соединены с группами входов регистра значащих, моментов, регистра времени отсчета и вычитающего счетчика, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к первым входам второго коммутатора, третьего элемента ИЛИ и регистра дробной части, а также к пятому выходу блока управления, шетой выход которого соединен с вторыми входами третьего элемента ИЛИ и второго коммутатора и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с первым выходом блока управления, и первым входом пятого элемента ИЛИ, второй вход которого подключен к второму входу регистра дробной части, седьмому выходу блока управления и первому входу шестого элемента ИЛИ, второй вход которого соединен с вторым входом первого коммутатора, а выход подключен к входу регистра времени отсчета, выходы вычитающего счетчика соединены с второй группой входов сумматора, выходы второго коммутатора подключены к второй группе входов блока вычитания, вход которого соединен с выходом третьего элемента ИЛИ и первым входом третьего коммутатора, второй вход которого подключен к выходу пятого элемента ИЛИ и входу регистра адреса, а третий в-ход соединен с выходом первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к входу регистра значащих моментов. На фиг. 1 представлена функциональная схема устройства преобразования временных интервалов в двоичный код; на фиг. 2 - пример функциональной схемы блока управления. Устройство содержит блок 1 управления, генератор 2 тактовых импульсов, регистр 3 адреса, блок 4 памяти, регистр 5 состояния канала, регистр 6 времени отсчета, регистр 7 знача1цих моментов, блок 8 вычитания с избыточнЕлм старшим разрядом, сумматор 9, вычитающий счетчик 10, регистр 11 дробной части числа, коммутаторы 12-14, элементы 15-20 ИЛИ, элемент 21 И и блок 22 вывода информации, содержащий регистр 23 сдвига, счетчик 24 и дешифратор 25 и ключ 26. Блок 1 управления содержит седьмой выход 27, первый выход 28, шестой выхсзд 29, пятый выход 30, вторую шину 31 входов, первую группу 32 входов, второй вход 33, второй выход 34, третий выход 35, четвертый выход 36, вход луска-37, подключенный к .шине 37 пуска, первый .вход 38. fta фиг. 2 представлена функционал ная схема одного из возможных вариантов выполнения блока 1 управления 1 управления содержит D-три геры 39-45, элементы 46-49 ИЛИ, эле менты 50-57 И и дешифраторы 58 и 59 Дешифратор 58 содержит элемент 60 И, элементы 61-63 ИЛИ и элементы 64 и 65 НЕ. Дешифратор 59 содержит элемент 66 ИЛИ и элемент 67 НЕ. Устройство работает следующим об разом. В блок 4 памяти предварительно заносят принятые по каналу связи данные в виде кода состояния канала в сопровождении кода текущего време ни , отображающего в двоичном .исчисл нии моменты изменения состояния канала (значащие моменты) . При эт.ом масштаб отсчета времени всегда можно выбрать таким, чтобы единица отсчета соответствовала длительности одного бита. Команда Пуск, подаваемая по шине 37, включает генератор 2 тактовых импульсов, устанавливает в состояние 1 триггер 39 блока 1, остальные три устанавливает в геры 40-45 и блок 1 управления, по-сылаетпоследовательно по тактам упрарЛяющие сигналы на соответствую цие входы узлов у стррйства. Первый управляющий, сигнал поступает с выхода 27 блока 1 управления на один вход регистра И дробной части числа, сбрасывая все его разряды в б , через элемент 15 ИЛИ на вход регистра 3 адреса и на вход коммутатора 12 и через элемент 16 ИЛИ - на вход регистра 6 времени отдчета. В. результате этого по адресу, хранящемуся в регистре 3 адре са, из блока4 памяти через коммутатор 12 в регистр 6 времени отсчета переписывается код начального времени Ц изменения состояния- кана ла, которое является начальным моментом (t ) отсчета единиц информации (бит), содержащихся в преобразуемых временных интервалах, т.е. является передней границей пер вого временного интервала. В то же время происходит модификация аду/еса в регистре 3. Затем блок I управления осуществляет -безусловный переход во второе состояние и управляющий сигнал поступает с выхода 281 на вход регистр 5 состояния канала, через элемент 15 ИЛИ -; на вход регистра 3 адреса на вход коммутатора 12, через элемент 17 ИЛИ - на вход регистра 7 зн чащих моментов. В результате этого .по очередному адресу из блока 4 памяти через коммутатор 12 в регистр значащих-моментов переписываются данные о следующем t,- времени изменения состояния канала, а в регистр 5 состояния - код состояния О или , предшествукнцего этому изменению.. Дальнейший порядок операций зависит от содержимого регистра 11, в котором хранится представленная в двоичном коде дробная часть m числа, характеризующего длительность пред- шествующего реального вретленного интервала. В первом цикле работы устройства все разряды регистра 11 содержат О(т 0) в силу того, что пер- . вый сигнал с выхода 27 блока 1 управления, сбрасывает, как уже отмечалось, регистр 11 в нулевое состояние. Блок 1 управления получая об этом информацию по входам 31, переходит, минуя третье, в четвертое состояние. В последующих циклах работы устройства содержимое регистра II определяется длительностью предшествующего реального временного интервала. Если преддаествующий временной ин.тервал не искажен и его. длительность совпадает с длительностью идеальной кодовой посылки,.то он содер«ит целое число бит. При этом все разряд регистра 11 дробной части числа со(т 0) . держат Если длительность предшествукяцего временного интервала вследствие краевых искажений и помех.меньше длительности идеальной кодовой посылки, то дробная часть числа, х-арактеризующегр эту длительность, больше или равна половине длительности бита (). При этом старший разряд регистра 11 содержит 4J В этом случае, как и- в двух предьщущих, блок 1.управления, получая соответствующую информацию по входам 31, переходит, минуя третъе, в четвертое состояние. Если длительность предшествующего временного интервала, вследствие краевых искажений и помех, больше длительности идеальной кодовой посылки, то дробная часть числа, характеризующего эту длительность, меньше половины длительности бита (т -§). При этом старший разряд .регистра 11 содержит О и по меньшей мере один из остальных его разрадов содержит Ч. Такое же стостояние имеет регистр 11 и тогда, когда предшествующий реальный временной интервал образован импульсом дробления и его длительность меньше половины длительности бита. В обоих этих случаях блок 1 управления, получая соответствующую информацию по входам 31, переходит в третье состояние и управляющий сигнал с выхода 29 поступает на вхо коммутатора 13, через элемент Х7 ИЛИ на вход регистра 7 значащих моменто и через элемент 18 ИЛИ - на вход коммутатора 12 и на вход блока 8 вычитания. По этому сигналу блок 8 вычитания определяет разницу между значениями времени, поступившими на его входы соответственно из регистра 7 значащих моментов и через коммутатор 12 - из регистра 11 дробной части числа. Результат заносится через коммутатор 12 в регистр 7 зна чащих моментов. После этого блок 1 управления ос ществляет безусловный переход в чет вертое состояние и посылает управля ющий сигнал с выхода 30 через элемент 18 ИЛЙ на вход блока 8 вычитания и на вход коммутатора 12, через элемент 19 ИЛИ - на вход счетчика 10, а также непосредственно на входы коммутатора 13 и регистра 11 дробной части числа. По этому сигналу блок 8 вычитания определяет разницу между значениями времени, поступившими на его информационные входы соответственно из регистра 7 значащих моментов и регистра 6 времени отсчета (в общем случае ) Двоичное число, полученное в результате этой операции, представляе собой выраженную в битах и долях би длительность реального временного интервала сучетом иг пульсов дроб-. Ленин и краевых искажений на границ с предшествующим временным интервалом. Целая часть ц этого числа заноси ся через коммутатор 12 в счетчик 10 а дробная m - в регистр 11 дробной части числа. Если в результате операции вычитания образуется отрицательное число, что свидетельствует а дроблении предшествующего временного интервала у его задней границы Т-, то на выходе блока 8 вычитания, соединенном с его избыточным старшим разрядом, появляется сигнал , который, попадая на вход 33 блока 1 управления, возвращает его во второ состояние и повторяется уже описанный цикл операций, соответствующих, второму и четвертому состояниям бло ка 1 управления, причем этот цикл повторяется до тех пор, пока на выходе блока 8 вычитания не появится положительное число. Если целая часть числа равна нулю (п 0), а дробная часть меньше половины длительности бита (тп -) что свидетельствует о дроблении кодовой посылки, то блок 1 управления получая соответствующую информацию по входам 31 и 32, возвращается во второе состояние и повторяется уже описанный цикл операций, соответствуюцИх второму, третьему и четвертому состояниям блока 1 управления, причем повторяется до тех пор, пока число, характеризующее длительность временного интервала (с учетом искажений) , не сравняется с половиной длительности бита или не превысит ее. Если длительность обрабатываемого временного интервала больше длительности идеальной кодовой посылки или совпадает с ней, то целая часть числа больше нуля (п-7/1), а дробная меньше половины длительности бита at. ). В этом случае целая часть числа представляет собой выраженную в битах длительность истинного временного интервала (nj Nj). Блок управления, получая соответствующую информацию по входам 31 и 32, переходит, минуя пятое, в шестое состояние. Если длительность обрабатываемого временного интервала меньше длительности идеальной кодовой посылки, то m -2 . При этом старший разряд .регистра 11 дробной части числа содержит . Блок 1 управления, получая об этом информацию по входу 31, переходит в пятое состояние, и управляющий сигнал с выхода 34 поступает на вход коммутатЬра 14, через элемент 19 ИЛИ - на вход счетчика 10 и через элемент 20 ИЛИ - на управляющий вход сумматора -9 и на управляющий вход коммутатора 12. По этому сигналу с выхода регистра 11 дробной части числа через коммутатор 14 на вход сумматора 9 , х1ранившийся в поступает код старшем разряде регистра 11, в то время как на входе сумматора 9 находится код целой части п числа, , отображающего длительность реального временного интервала. Сумматор 9 осуществляет операцию сложения и результат N j j + 1, отображающий длительность истинного (неискаженного) временного интервала, заносится через коммутатор 12 в счетчик 10, после чего блок 1 управления осуществляет безусловный переход в шестое состояние. Блок 1 управления посылает сигнал с выхода 35 на вход коммутатора 14, через элемент 16 ИЛИ - на вход регистра 6 времени отсчета, и через элемент 20 ИЛИ - на вход коммутатора 12 и на вход сумматора 9. В результате этого из регистра 6 через коммутатор 14 на вход сумматора 9 поступает код времени Т.- отсчета, т.е. передней границы, для обрабатываемого временного интервала, тогда как на входе сумматора 9, соединенном с выходом счетчика 10, находится код целого числа Nj (Отображакндего истинную длительность этого временного интервала. Происходит суммирование указанных величин, и результат Т.- Т| +N; , представляющий собой начало отсчета для следующего временного интервала, т.е. границу между времен ными интервалами, заносится в регистр -б времени отсчета. Далее блок 1 управления осуществляет безусловный переход в седьмое состояние и через его выход 36 на вход элемента 21 И поступает сигнал разрешающий прохождение тактовых импульсов генератора 2 на счетный вход счетчика 10 и через вход блока 22 вы вода информации - на сдвигающий вхоД регистра 23 и.вход счетчика 24. Каждый тактовых импульсов сдвигает влево на один разряд содержимое регистра 23 и при этом в его младший разряд заносится бит, значение кото1) соответствуе рого ( О состоянию канала, зафиксированному регистре 5. В то же время каждый тактовый им пульс увеличивает на единицу содержимое счетчика 24, уменьшает на еди ницу содержимое счетчика 10. . Как только содержимое счетчика 1 станет равным нулю, блок 1 управлен возвращается во второе состояние, после чего повторяется уже описанный цикл операций со следующей груп пой данных, извлеченных по очереднс адресу из блока 4 памяти. Таким образом, число тактовых им пульсов генератора 2, поступивших н вход блока 22 вывода информации, а значит и чисГло бит, зарегистрирован ных в регистре 23 за один цикл, рав но NJ- . КогДа регистр 23 блока 22 вывода информации полностью загружается, счетчик 24 переполняется и на всех его выходах (обозначены одной линией)1 появляются О, в результате чего на выходе дешифратора 25 появляется сигнал, открывающий ключ 26, через которьай полученные в результа те преобразования данные выводятся из устройства. Таким образом, предлагаемое.устройство благодаря наличию новых узлов и связей обладает более высокой достоверностью по сравнению с изBecTHbiM. Формула изобретения Устройство для преобразования вр менных интервалов в двоичный код, содержащее два коммутатора, генерат тактовых импульсов, выход которого подключен к первым входам блока управления и элемента И, выход которо го соединен с первыми входами блока вывода информации и вычитающего счетчика, выходы которого соединены с первой группой входов блока управления, первый выход которого соединен с входом регистра состояния канала, а второй выход подключен к первым вхо дам первого коммутатора и первого элемента ИЛИ, вторые входы которых объединены и подключены к третьему выходу блока управления, четвертый выход которого соединен с вторым вхЬдом эле.мента И, выход первого элемента ИЛИ подключен к управляющему входу сумматора, выходы регистра времени отсчета соединены с первой группой входов первого коммутатора, выходы которого подключены к первой группе входов сумматора, выходы регистра значащих моментов подключены к первой группе входов блока вычитания, выход регистра адреса соединен с управляющим входом блока памяти, первая группа выходов которого соединена с группой входов регистра состояния канала, выходы которого подключены к группе входов блока вывода ин- формации, отличающееся тем, что, с целью повышения достоверности преобразования, в него введены коммутатор, пять элементов ИЛИ и регистр дробной части,причем выходы регистра времени отсчета подключены к первой группе входов второго коммутатора, вторая группа входов ко-, торого объединена с второй группой входов первого коммутатора и подключена к выходам регистра дробной час-ти и к второй группе входов блока управления, второй вход которого соединен с выходом блока вычитания, группа выходов которого подключена к группе входов регистрадробной части и к первой группе входов третьего коммутатора, вторая и третья группы входов которого подключены соответственно к выходам блока памяти и сумматора, выходы третьего коммутатора соединены с группами входов регистра значащих моментов, регистра времени отсчета и вычитающего счетчика, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к первым входам второго коммутатора, третьего элемента ИЛИ и регистра дробной части, а также к пятому выходу блока управления, шестой выход которого соединен с вторыми входами третьего элемента ИЛИ и второго коммутатора и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с первым выходом блока управления, и первым входом пятого элемента ИЛИ, второй вход, которого подключен к второму входу, регистра дробной части, седьмому выходу блока управления и первому входу шестого элемента ИЛИ, второй вход которого соединен с вторым входом первого коммутатора, а выход подключен к входу регистра времени отсчета выходы вычитающего счетчика соединены с второй группой входов сумматора, выходы второго коммутатора подключены к второй группе входов блока вычитания, вход которого соединен с выходом третьего элемента ИЛИ и первым входом третьего ко1Ф1утатора, второй вход которого подключен к выходу пятого элемента ИЛИ и входу регистра адреса, а третий вход соединен с йыходом первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к входу регистра значащих моментов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 646437, кл. Н 03 К 13/20, 1978.

2.Авторское свидетельство СССР f 497725, кл. Н 03 К 13/20, 1970.

3.Авторское свидетельство СССР по заявке 3210569,кл.С 04 F 10/04, 18.06.81 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования временных интервалов в двоичный код | 1980 |

|

SU945980A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Адаптивное цифровое устройство для определения амплитуды и длительности случайных сигналов | 1983 |

|

SU1233170A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

Авторы

Даты

1982-12-23—Публикация

1981-02-25—Подача