1

Изобретение относится к запоминающим устройствам и может быть использовано для контроля оперативных запоминающих устройств, работающих в реальном масштабе времени.

Известно устройство для контроля записи информации в блоках памяти, которое содержит накопитель, регистр числа, регистр адреса, дешифратор адреса с адресными формирователями, разрядные формирователи, блок усилителей воспроизведения, блок образования контрольной информации, два триггера и пять логических элементов 1 .

Недостаток устройства - невозможность самоконтроля.

Наиболее близким техническим решением к изобретению является устройство, содержащее формирователи интервала записи и конца считывания, элементы И и элементы ИЛИ, входы которого подключены соответственно к выходу формирователя записи и первого элемента И, а выход соединен с шиной «Запись и через последовательно включенные формирователи считывания и конца считывания - с входом второго элемента И, другой вход которого соединен с выходом схемы сравнения, а выход - с первыми входами первого и третьего элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам формирователя интервала записи, вход которого соединен с выходом формирователя записи, причем выход третьего элемента И подключен к шине «Отказ 2.

Недостатком этого устройства является низкое быстродействие, так как сигнал на выходе схемы сравнения может вызывать повторную запись по данному адресу до тех пор, пока не окончится отведенное на коррекцию сбоя время-интервал контроля.

Цель изобретения - повышение быстродействия при применении для контроля верности записи данных контрольного считывания.

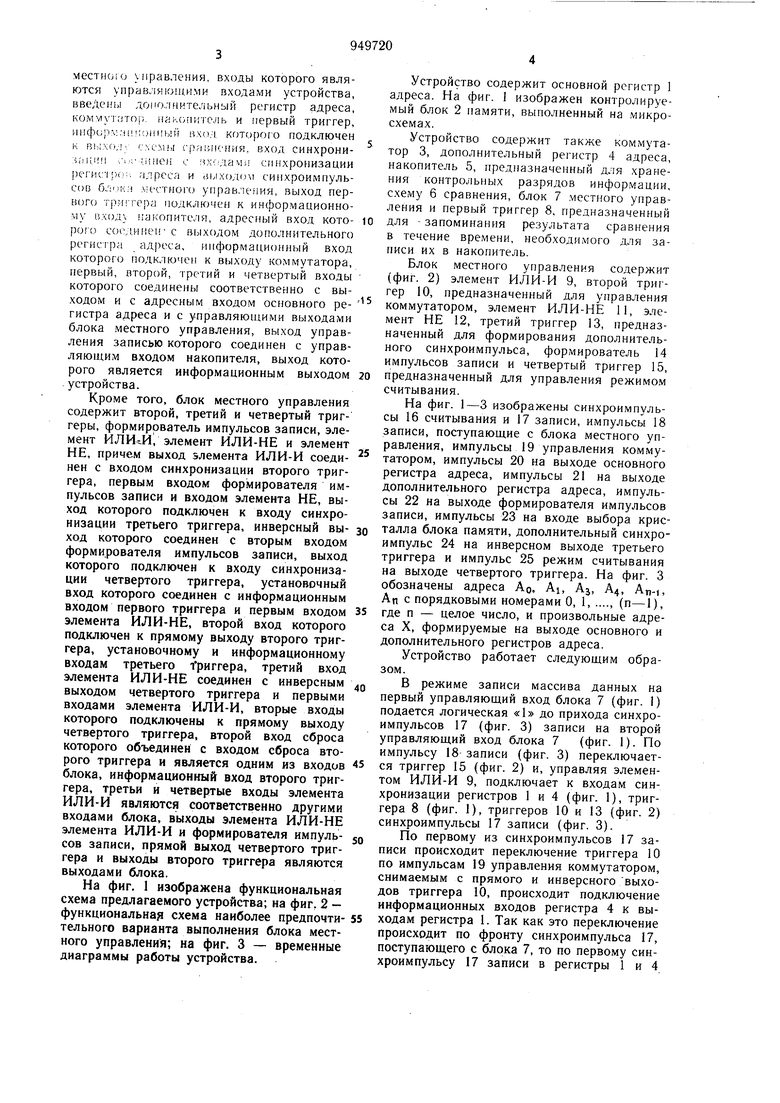

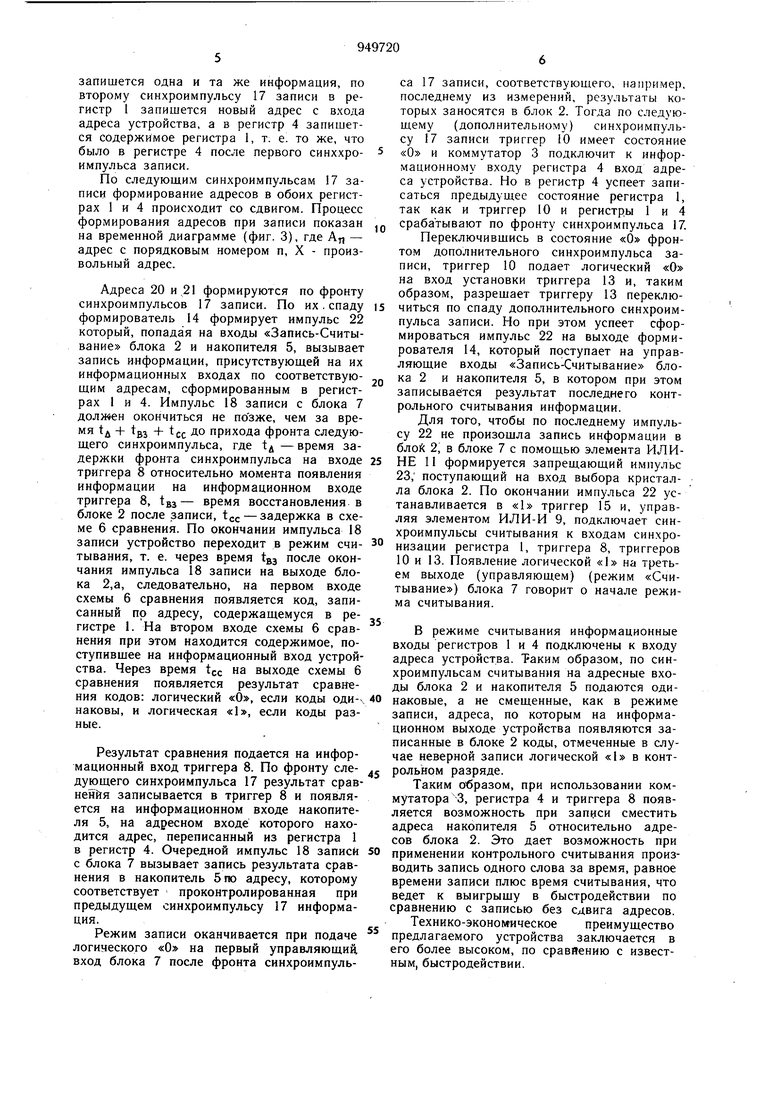

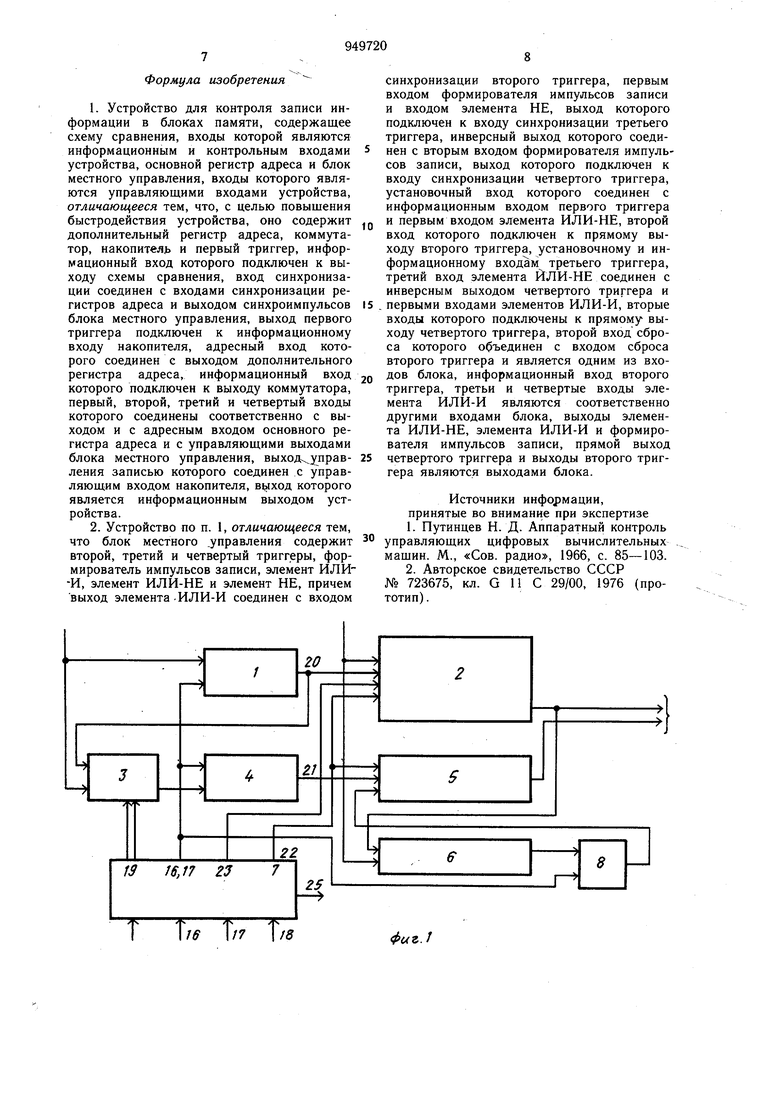

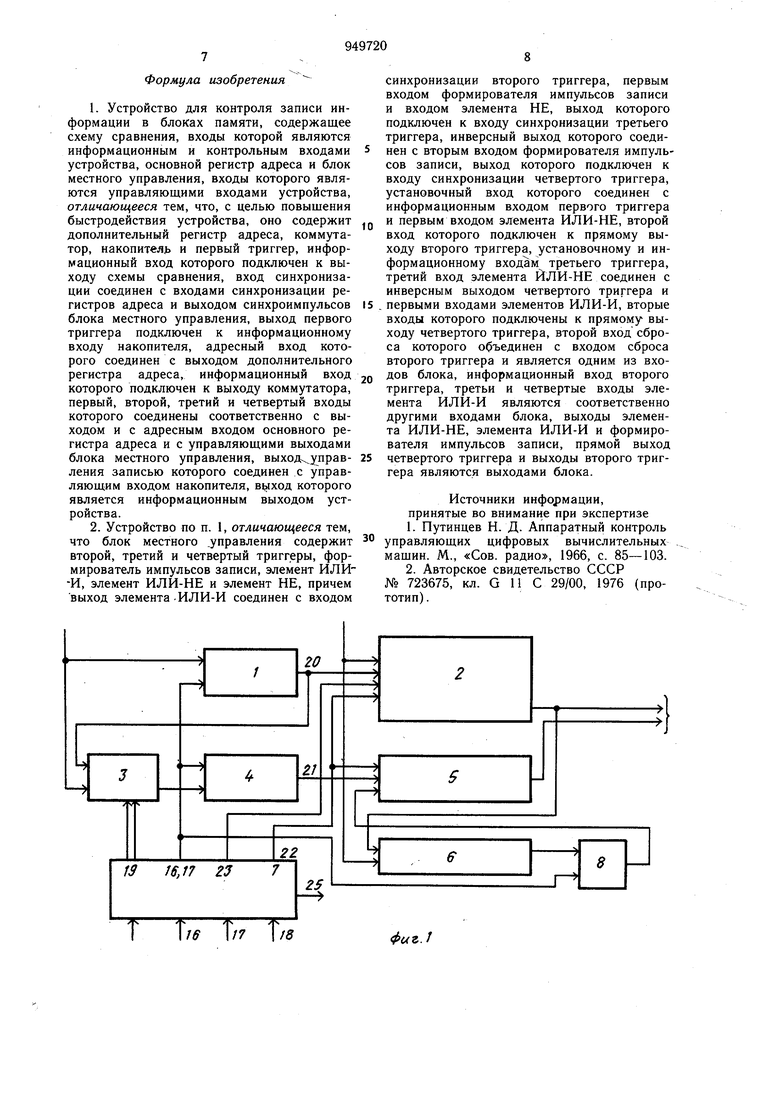

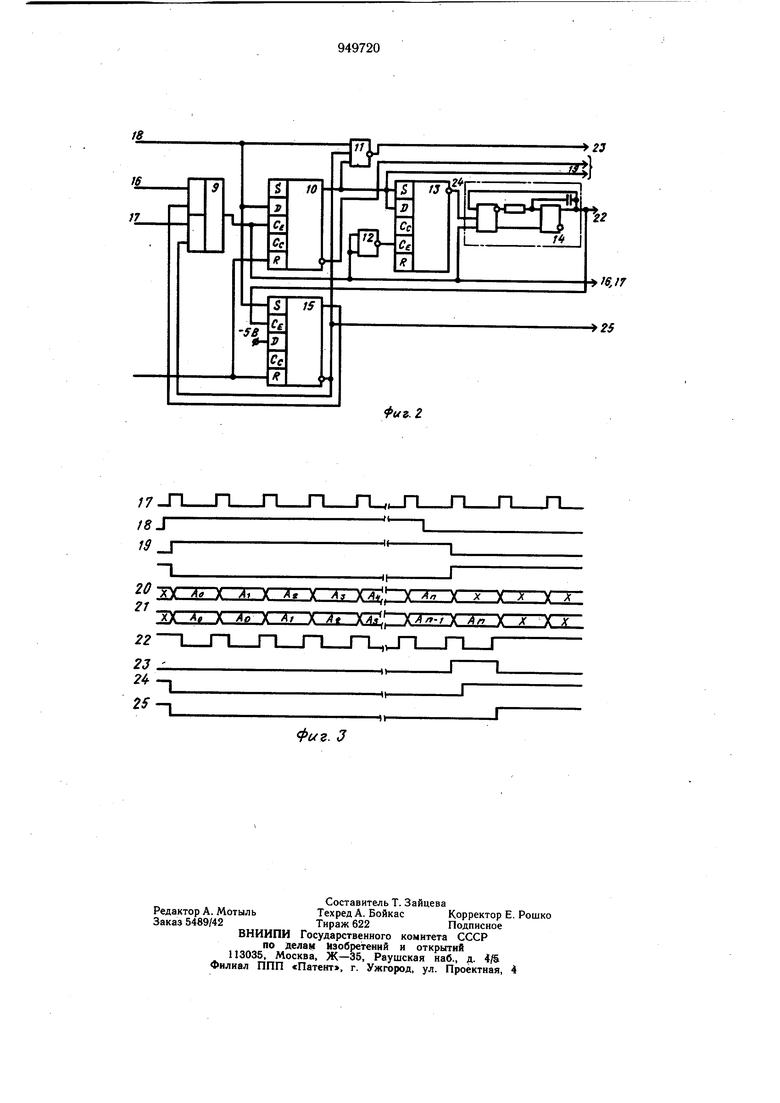

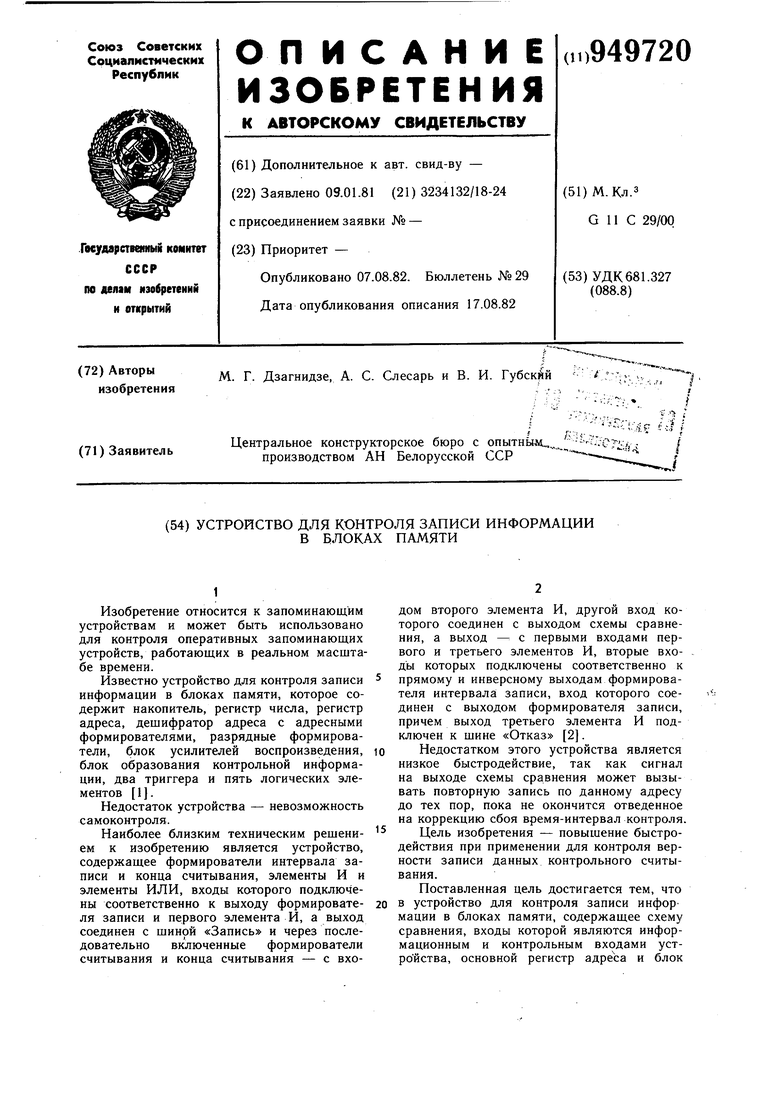

Поставленная цель достигается тем, что 20 в устройство для контроля записи информации в блоках памяти, содержащее схему сравнения, входы которой являются информационным и контрольным входами устройства, основной регистр адреса и блок местного управления, входы которого являются управляющими входами устройства, введены дополнительный регистр адреса, коммут;ггор. iiaKOiiirrcJih и первый триггер, )л:.() iixo.i. KOTopoio подключен к R),ivfj, ;.емьг сраинония, вход синхрони:i; iii n N-i-riiiiiCH ij мхода п синхронизации регИ.. .члреса и ,)ых() синхроимпульсов 6л)-. MfcTHoio управления, выход первого триггер;, подключен к информационному ВХОД} накопителя, адресный вход которого сое,1,ннеи- с выходом дополнительного регисгра адреса, информационный вход которого подключен к выходу коммутатора, первый, второй, третий и четвертый входы которого соединены соответственно с выходом и с адресным входом основного регистра адреса и с управляющими выходами блока местного управления, выход управления записью которого соединен с управляющим входом накопителя, выход которого является информационным выходом устройства. Кроме того, блок местного управления содержит второй, третий и четвертый триггеры, формирователь импульсов записи, элемент ИЛИ-Й1 элемент ИЛИ-НЕ и элемент НЕ, причем выход элемента ИЛИ-И соединен с входом синхронизации второго триггера, первым входом формирователя импульсов записи и входом элемента НЕ, выход которого подключен к входу синхронизации третьего триггера, инверсный выход которого соединен с вторым входом формирователя импульсов записи, выход которого подключен к входу синхронизации четвертого триггера, установочный вход которого соединен с информационным входом первого триггера и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к прямому выходу второго триггера, установочному и информационному входам третьего fpHrrepa, третий вход элемента ИЛИ-НЕ соединен с инверсным выходом четвертого триггера и первыми входами элемента ИЛИ-И, вторые входы которого подключены к прямому выходу четвертого триггера, второй вход сброса которого объединен с входом сброса второго триггера и является одним из входов блока, информационный вход второго триггера, третьи и четвертые входы элемента ИЛИ-И являются соответственно другими входами блока, выходы элемента ИЛИ-НЕ элемента ИЛИ-И и формирователя импульсов записи, прямой выход четвертого триггера и выходы второго триггера являются выходами блока. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг, 2 - функциональная схема наиболее предпочтительного варианта выполнения блока местного управления; на фиг. 3 - временные диаграммы работы устройства. Устройство содержит основной регистр 1 адреса. На фиг. 1 изображен контролируемый блок 2 памяти, выполненный на микросхемах. Устройство содержит также коммутатор 3, дополнительный регистр 4 адреса, накопитель 5, предназначенный для хранения контрольных разрядов информации, схему 6 сравнения, блок 7 местного управления и первый триггер 8, предназначенный для - запоминания результата сравнения в течение времени, необходимого для записи их в накопитель. Блок местного управления содержит (фиг. 2) элемент ИЛИ-И 9, второй триггер 10, предназначенный для управления коммутатором, элемент ИЛИ-НЕ 11, элемент НЕ 12, третий триггер 13, предназначенный для формирования дополнительного синхроимпульса, формирователь 14 импульсов записи и четвертый триггер 15, предназначенный для управления режимо.м считывания. На фиг. 1-3 изображены синхроимпульсы 16 считывания и 17 записи, импульсы 18 записи, поступающие с блока местного управления, импульсы 19 управления коммутатором, импульсы 20 на выходе основного регистра адреса, импульсы 21 на выходе дополнительного регистра адреса, импульсы 22 на выходе формирователя импульсов записи, импульсы 23 на входе выбора кристалла блока памяти, дополнительный синхроимпульс 24 на инверсном выходе третьего триггера и импульс 25 режим считывания на выходе четвертого триггера. На фиг. 3 обозначены адреса АО, AI, Aj, А4, АП с порядковыми номерами О, 1, (п-1), где п - целое число, и произвольные адреса X, формируемые на выходе основного и дополнительного регистров адреса. Устройство работает следующим образом. В режиме записи массива данных на первый управляющий вход блока 7 (фиг. 1) подается логическая «1 до прихода синхроимпульсов 17 (фиг. 3) записи на второй управляющий вход блока 7 (фиг. 1). По импульсу 18 записи (фиг. 3) переключается триггер 15 (фиг. 2) и, управляя элементом ИЛИ-И 9, подключает к входам синхронизации регистров 1 и 4 (фиг. 1), триггера 8 (фиг. 1), триггеров 10 и 13 (фиг. 2) синхроимпульсы 17 записи (фиг. 3). По первому из синхроимпульсов 17 записи происходит переключение триггера 10 по импульсам 19 управления коммутатором, снимаемым с прямого и инверсного выходов триггера 10, происходит подключение информационных входов регистра 4 к выходам регистра 1. Так как это переключение происходит по фронту синхроимпульса 17, поступающего с блока 7, то по первому синхроимпульсу 17 записи в регистры 1 и 4

запишется одна и та же информация, по второму синхроимпульсу 17 записи в регистр 1 запишется новый адрес с входа адреса устройства, а в регистр 4 запишется содержимое регистра 1, т. е. то же, что было в регистре 4 после первого синххроимпульса записи.

По следующим синхроимпульсам 17 записи формирование адресов в обоих регистрах 1 и 4 происходит со сдвигом. Процесс формирования адресов при записи показан на временной диаграмме (фиг. 3), где АП - адрес с порядковым номером п, X - произвольный адрес.

Адреса 20 и.21 формируются по фронту синхроимпульсов 17 записи. По их.спаду формирователь 14 формирует импульс 22 который, попадая на входы «Запись-Считывание блока 2 и накопителя 5, вызывает запись информации, присутствующей на их информационных входах по соответствующим адресам, сформированным в регистрах I и 4. Импульс 18 записи с блока 7 должен окончиться не позже, чем за время t -f tgj + tjj. до прихода фронта следующего синхроимпульса, где t - время задержки фронта синхроимпульса на входе триггера 8 относительно момента появления информации на информационном входе триггера 8, время восстановления в блоке 2 после записи, tec - задержка в схеме 6 сравнения. По окончании импульса 18 записи устройство переходит в режим считывания, т. е. через время tea после окончания импульса 18 записи на выходе блока 2,а, следовательно, на первом входе схемы 6 сравнения появляется код, записанный по адресу, содержащемуся в регистре 1. На втором входе схемы 6 сравнения при этом находится содержимое, поступившее на информационный вход устройства. Через время tec на выходе схемы 6 сравнения появляется результат сравнения кодов: логический «О, если коды оди-х наковы, и логическая «1, если коды разные.

Результат сравнения подается на информационный вход триггера 8. По фронту еледующего синхроимпульса 17 результат сравнения записывается в триггер 8 и появляется на информационном входе накопителя 5, на адресном входе которого находится адрес, переписанный из регистра 1 в регистр 4. Очередной импульс 18 записи с блока 7 вызывает запись результата сравнения в накопитель 5 по адресу, которому соответствует проконтролированная при предыдущем синхроимпульсу 17 информация.

Режим записи оканчивается при подаче логического «О на первый управляющие вход блока 7 после фронта синхроимпульса 17 записи, соответствующего, например, последнему из измерений, результаты которых заносятся в блок 2. Тогда по следующему (дополнительному) синхроимпульсу 17 записи триггер 10 имеет состояние «О и коммутатор 3 подключит к информационному входу регистра 4 вход адреса устройства. Но в регистр 4 успеет записаться предыдущее состояние регистра 1, так как и триггер 10 и регистры 1 и 4 срабатывают по фронту синхрои.мпульса 17.

Переключившись в состояние «О фронтом дополнительного синхроимпульса записи, триггер 10 подает логический «О на вход установки триггера 13 и, таким образом, разрещает триггеру 13 переключиться по спаду дополнительного синхроимпульса записи. Но при этом успеет сформироваться импульс 22 на выходе формирователя 14, который поступает на управляющие входы «Запись-Считывание блока 2 и накопителя 5, в котором при этом записывается результат последнего контрольного считывания информации.

Для того, чтобы по последнему импульсу 22 не произощла запись информации в блоЛ 2, в блоке 7 с помощью элемента ИЛИНЕ 11 формируется запрещающий импульс 23; поступающий на вход выбора кристалла блока 2. По окончании импульса 22 устанавливается в «1 триггер 15 и, управляя элементом ИЛИ-И 9, подключает синхроимпульсы считывания к входам синхронизации регистра 1, триггера 8, триггеров 10 и 13. Появление логической «Ь на третьем выходе (управляющем) (режим «Считывание) блока 7 говорит о начале режима считывания.

В режиме считывания информационные входы регистров 1 и 4 подключены к входу адреса устройства. Таким образом, по синхроимпульсам считывания на адресные входы блока 2 и накопителя 5 подаются одинаковые, а не смещенные, как в режиме записи, адреса, по которым на информационном выходе устройства появляются записанные в блоке 2 коды, отмеченные в случае неверной записи логической «1 в контрольном разряде.

Таким образом, при использовании коммутатора 3, регистра 4 и триггера 8 появляется возможность при записи сместить адреса накопителя 5 относительно адресов блока 2. Это дает возможность при применении контрольного считывания производить запись одного слова за время, равное времени записи плюс время считывания, что ведет к выигрыщу в быстродействии по сравнению с записью без сдвига адресов.

Texникo-экoнo fичecкoe преимущество предлагаемого устройства заключается в его более высоком, по сравЯению с известным, быстродействии.

Формула изобретения

1.Устройство для контроля записи информации в блоках памяти, содержащее схему сравнения, входы которой являются информационным и контрольным входами устройства, основной регистр адреса и блок местного управления, входы которого являются управляющими входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный регистр адреса, коммутатор, накопителе и первый триггер, информационный вход которого подключен к выходу схемы сравнения, вход синхронизации соединен с входами синхронизации регистров адреса и выходом синхроимпульсов блока местного управления, выход первого триггера подключен к информационному входу накопителя, адресный вход которого соединен с выходом дополнительного регистра адреса, информационный вход которого подключен к выходу коммутатора, первый, второй, третий и четвертый входы которого соединены соответственно с выходом и с адресным входом основного регистра адреса и с управляющими выходами блока местного управления, выход улравЛенин записью которого соединен с у правляющим входом накопителя, вь1ход которого является информационным выходом устройства.

2.Устройство по п. 1, отличающееся тем, что блок местного .управления содержит второй, третий и четвертый триггеры, формирователь импульсов записи, элемент ИЛИ

-И, элемент ИЛИ-НЕ и элемент НЕ, причем выход элемента-ИЛИ-И соединен с входом

синхронизации второго триггера, первым входом формирователя импульсов записи и входом элемента НЕ, выход которого подключен к входу синхронизации третьего триггера, инверсный выход которого соединен с вторым входом формирователя импульсов записи, выход которого подключен к входу синхронизации четвертого триггера, установочный вход которого соединен с информационным входом первого триггера и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к прямому выходу второго триггера, установочному и информационному входам третьего триггера, третий вход элемента ЙЛИ-НЕ соединен с инверсным выходом четвертого триггера и первыми входами элементов ИЛИ-И, вторые входы которого подключены к прямому выходу четвертого триггера, второй вход сброса которого объединен с входом сброса второго триггера и является одним из входов блока, информационный вход второго триггера, третьи и четвертые входы элемента ИЛИ-И являются соответственно другими входами блока, выходы элемента ИЛИ-НЕ, элемента ИЛИ-И и формирователя импульсов записи, прямой выход четвертого триггера и выходы второго триггера являются выходами блока.

Источники информации, принятые во внимание при экспертизе

1.Путинцев Н. Д. Аппаратный контроль управляющих цифровых вычислительных мащин. М., «Сов. радио, 1966, с. 85-103.

2.Авторское свидетельство СССР

№ 723675, кл. G 11 С 29/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1156146A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280456A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

1/7 Т/5

Фиг.1

Фиг. 3 Фиг.2 /«/7

Авторы

Даты

1982-08-07—Публикация

1981-01-09—Подача