Изобретение относится к вычислительной технике и может быть использовано в качестве промежуточной памяти при построении средств векторной обработки сигналов, например при вычислении быстрого преобразования Фурье.

Целью изобретения является повышение быстродействия устройства.

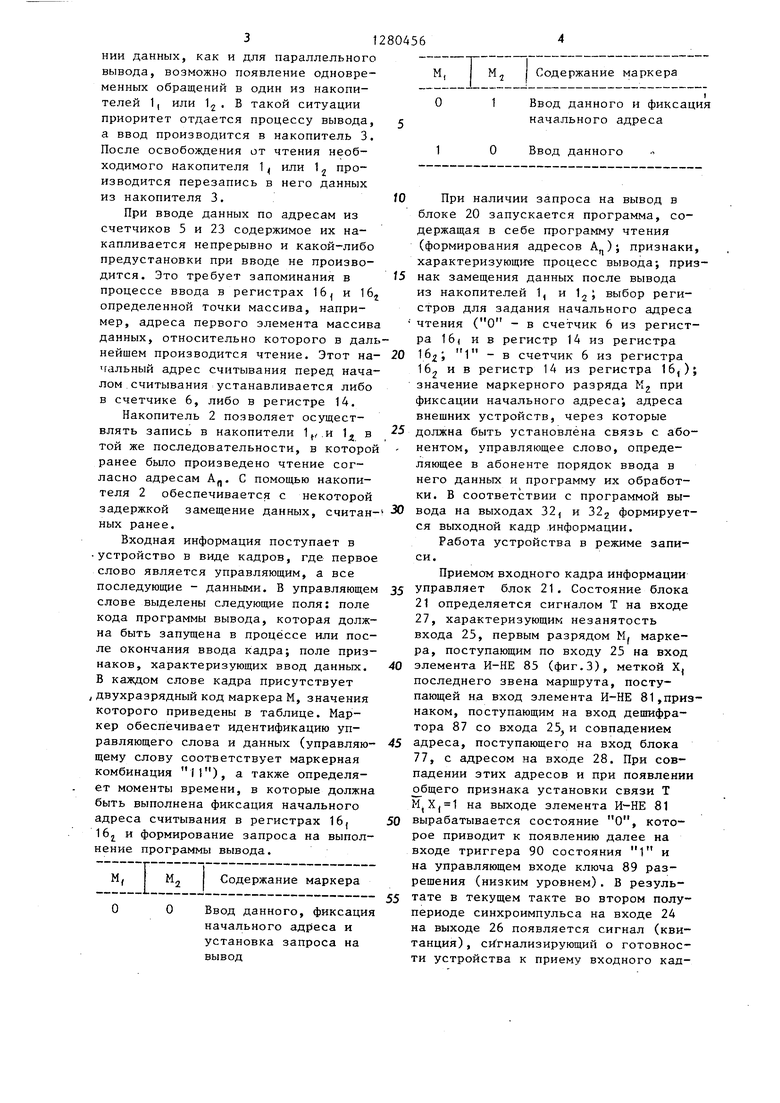

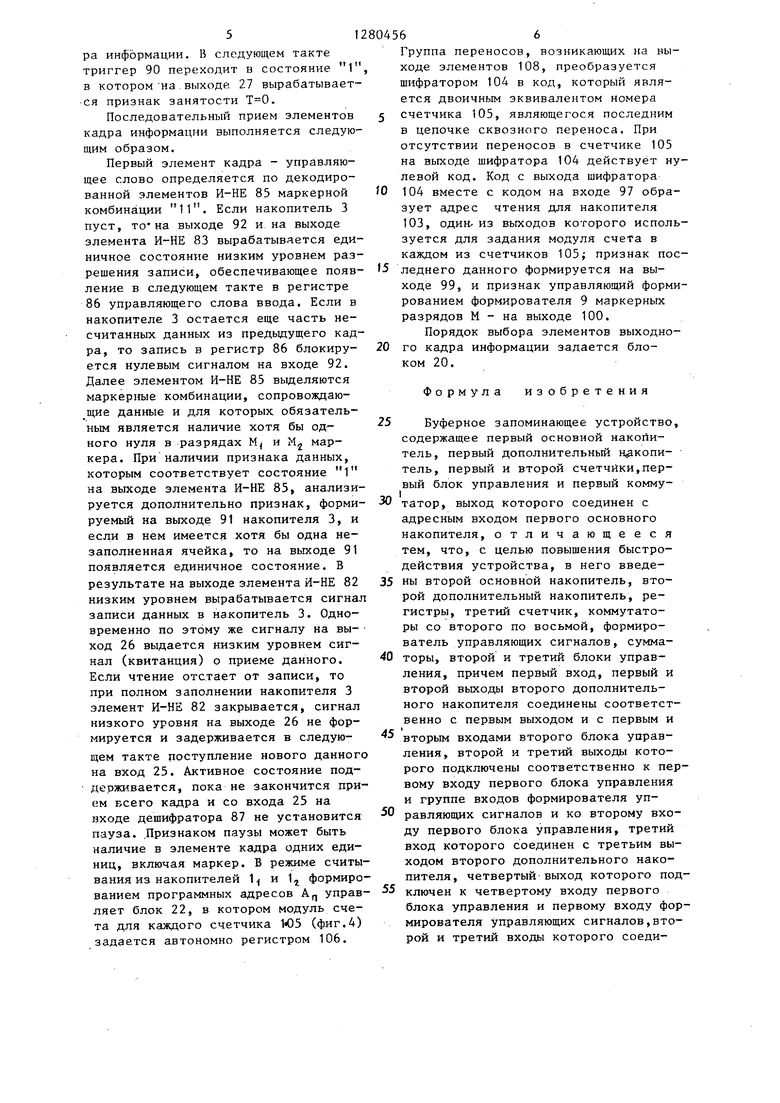

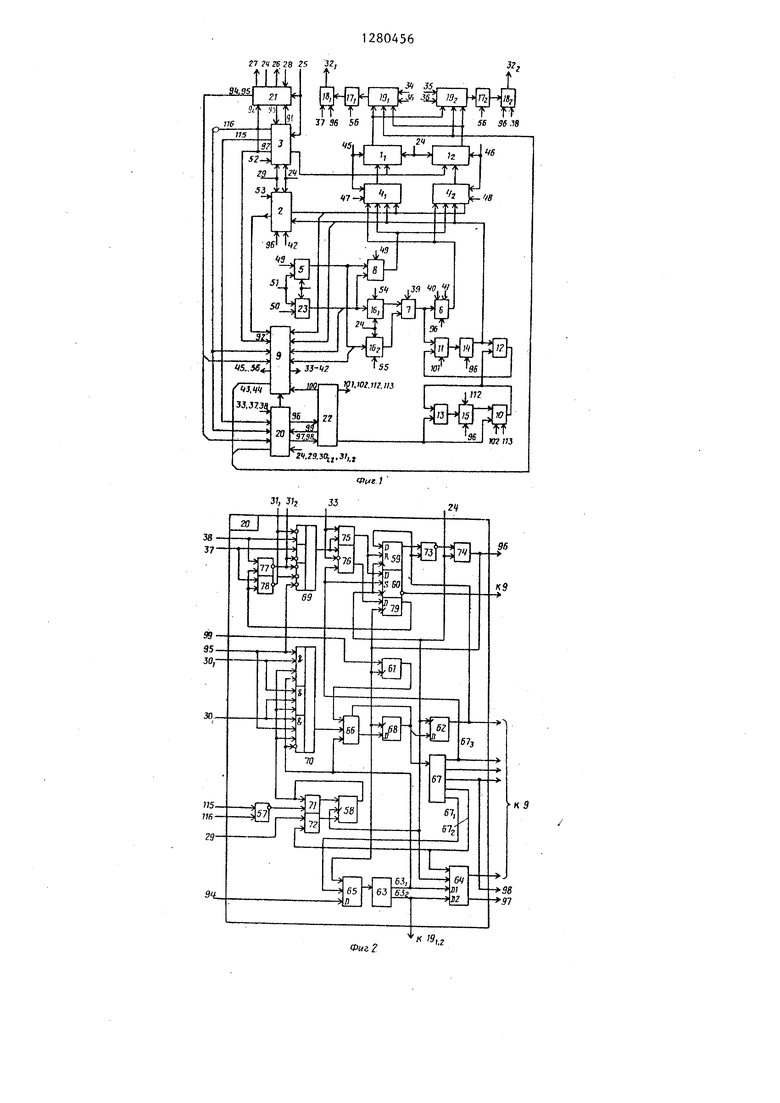

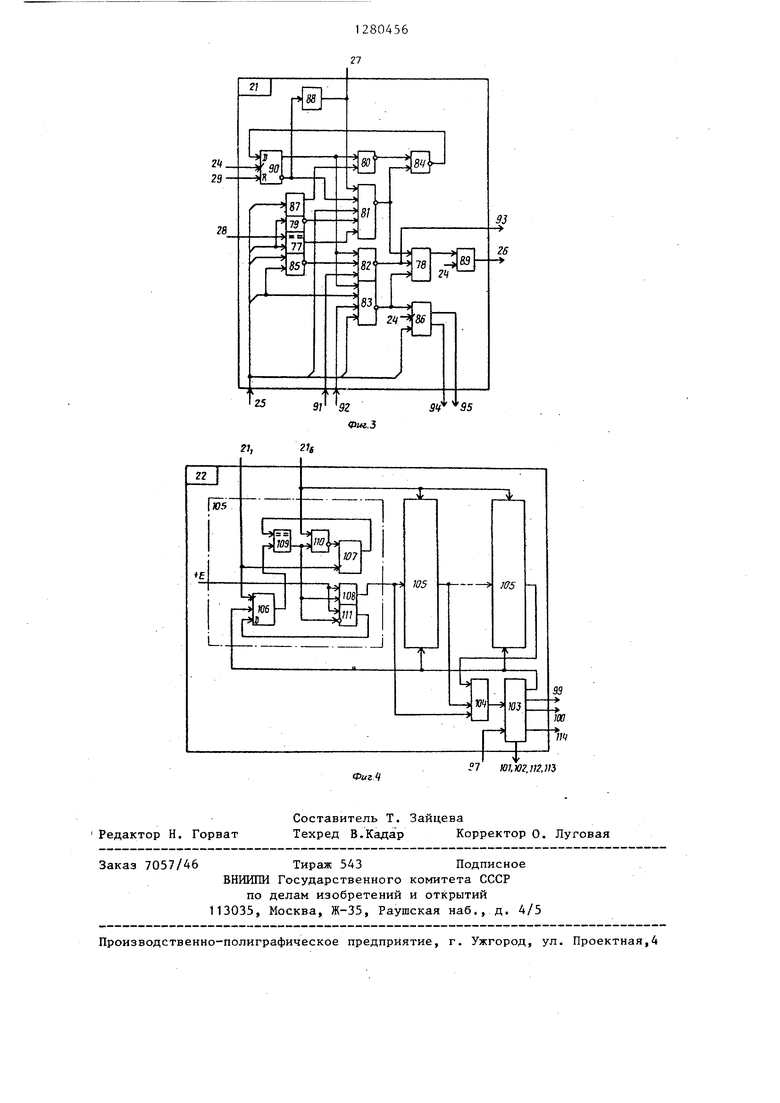

На фиг.1 представлена функциональная схема предложенного устройства; на фиг,2-4 - функциональные схемы блоков местного управления.

Устройство содержит (фиг.1) первый 1, и второй 1j основные накопители, первый 2 и второй 3 дополнительные накопители, первый 4( и второй Aj коммутаторы, первый 5 и второй 6 счетчики, третий 7 и четвертый 8 коммутаторы, формирователь 9 управляющих сигналов, пятый 10 и шестой 11 коммутаторы, первый 12 и второй 13 сумматоры, регистры 14, 15, 16,, 16,;, 17,, 172, 3 182 с первого по восьмой, седьмой 19( и восьмой 192 коммутаторы, блоки 20-22 управления с первого по третий и третий счетчик 23.

На фиг.1 обозначены вход 24 синхронизации, информационный вход 25, управляющие выход 26, вход и выход 27, вход 28, вход 29 начальной установки, управляющие входы 30, ЗОг 31( и 31,, информационные выходы 32, и 322 устройства, выходы 33-56 с первого по двадцать четвертый формирователя 9 управляющих сигналов.

Первый блок 20 управления содержит (фиг.2) элемент ИЛИ-НЕ 57,триггеры 58-62, накопитель 63, регистр 64 команд, счетчик 65, формирователь 66 сигналов следующего состояния, дешифратор 67 состояний,регистр 68 состояний, элементы И-ИЛИ 69- 70, элементы ИЛИ 71 и 72, элементы И 73-76. Второй блок 21 управления содержит (фиг.З) блок 77 сравнения, элемент И 78, элемент НЕ 79, элементы И-НЕ 80-85, регистр 86, дешифратор 87, повторитель 88, ключ 89, триггер 90. На фиг.З обозначены вхо .да 91,92 и выходы 93-95 второго блока 21 управления.

На фиг.4 обозначены входы 96-98 и выходы 99-102 третьего блока 22 управления, который содержит (фиг.4 накопитель 103, шифратор ,104 и счетчики 105, каждый из которых содерO

5

0

5

0

5

0

5

0

5

жит регистр 106, счетчик 107, элемент И 108, блок 109 сравнения,элемент ИЛИ-НЕ 110 и элемент И 111.

На фиг.1-4 обозначены также выходы 112-114 блока 22 управления, третий 115 и четвертый 116 выходы накопителя 3.

Устройство работает следующим образом.

Записываемая информация располагается в накопителях 1, и 12 двумя способами. При первом способе сплошной массив данных располагается целиком в одном из накопителей 1 (или 12). При втором способе данные, имеюшд1е четные адреса, записываются в один, а данные с нечетными адресами - в другой из накопителей 1, и Ij (чередующееся размещение данных).

При вводе данные размещаются с постоянным или переменным шагом. В первом случае для адресации применяются счетчика 5 и 23, а во втором случае применяется накопитель 2, в котором накапливаются программно сформированные адреса А.

Вывод массива данных производится из одного или одновременно из двух накопителей 1, и 1 через выходы 32, и 32. При чтении только из одного накопителя 1, и 1 используется всегда программно сформированный адрес Ар, считываемый с выхода регистра 14. В случае одновременного чтения, т.е. параллельного вывода из двух накопителей 1 и Ij, в одном из них производится чтение по адресу из счетчика 6, а в другом - по адресу А. При чередующемся размещении параллельный вывод не применяется, поскольку в адресе А в общем случае отсутствует постоянство в чередовании четных и нечетных адресов. В результате при параллельном выводе возможно появление одновременных обращений к одному и тому же накопи- .телю 1 (или 12), что приводит к нарушению синхронности в появлении данных на разных выходах 32 и 322, так как возникает необходимость систематического притормаживания одного из обращений.

Применение двух накопителей 1 и Ij позволяет организовать, кроме параллельного вывода, также и параллельные ввод и вывод. Для сплошного размещения данных такая возможность очевидна. При чередующемся размеще31280456

НИИ данных, как и для параллельного вывода, возможно появление одновременных обращений в один из накопителей 1, или 12. В такой ситуации приоритет отдается процессу вывода, 5 а ввод производится в накопитель 3. После освобождения от чтения необходимого накопителя 1 или 1 производится перезапись в него данных из накопителя 3.W

При вводе данных по адресам из счетчиков 5 и 23 содержимое их накапливается непрерывно и какой-либо предустановки при вводе не производится. Это требует запоминания в 5 процессе ввода в регистрах 16 и 16 определенной точки массива, например, адреса первого элемента массива данных, относительно которого в дальнейшем производится чтение. Этот на- 20 чальный адрес считывания перед началом считывания устанавливается либо в счетчике 6, либо в регистре 14.

Накопитель 2 позволяет осущестВвод данного

При наличии запроса на вывод в блоке 20 запускается программа, содержащая в себе программу чтения (формирования адресов А); признаки, характеризующие процесс вывода; признак замещения данных после вывода из накопителей 1, и выбор регистров для задания начального адреса чтения (О - в счетчик 6 из регистра 16( ив регистр 14 из регистра 1 - в счетчик 6 из регистра 162 и в регистр 14 из регистра 16,);

значение маркерного разряда Кг при фиксации начального адреса; адреса внешних устройств, через которые

влять запись в накопители 1, .и Ц в 25 должна быть установлена связь с або- той же последовательности, в которой - нентом, управляющее слово, определяющее в абоненте порядок ввода в него данных и программу их обработранее было произведено чтение согласно адресам А. С помощью накопителя 2 обеспечивается с некоторой

ки. В соответствии с программой вызадержкой замещение данных, считан- -30 вода на выходах 32, и 322 формируется выходной кадр информации.

Работа устройства в режиме записи.

Приемом входного кадра информации управляет блок 21. Состояние блока 21 определяется сигналом Т на входе 27, характеризующим незанятость входа 25, первым разрядом М, маркера, поступающим по входу 25 на вход элемента И-НЕ 85 (фиг.З), меткой X, последнего звена маршрута, поступающей на вход элемента И-НЕ 81,приз40

ных ранее.

Входная информация поступает в

устройство в виде кадров, где первое слово является управляющим, а все последующие - данными. В управляющем 35 слове выделены следующие поля: поле кода программы вывода, которая должна быть запущена в процессе или после окончания ввода кадра; поле признаков, характеризующих ввод данных. В каждом слове кадра присутствует

,двухразрядный код маркера М, значения которого приведены в таблице. Маркер обеспечивает идентификацию управляющего слова и данных (управляю- 45 адреса, поступающего на вход блока щему слову соответствует маркерная комбинация 11), а также определяет моменты времени, в которые должна быть выполнена фиксация начального адреса считывания в регистрах 1б( 50 16 и формирование запроса на выполнение программы вывода.

наком, поступающим на вход дешифратора 87 со входа 25 и совпадением

77, с адресом на входе 28. При совпадении этих адресов и при появлении общего признака установки связи Т ,1 на выходе элемента И-НЕ 81 вырабатывается состояние О, которое приводит к появлению далее на входе триггера 90 состояния 1 и на управляющем входе ключа 89 разрешения (низким уровнем). В результате в текущем такте во втором полупериоде синхроимпульса на входе 24 на выходе 26 появляется сигнал (квитанция) , си гнализирующий о готовности устройства к приему входного

Содержание маркера

Ввод данного, фиксация начального адреса и установка запроса на вывод

Ввод данного

При наличии запроса на вывод в блоке 20 запускается программа, содержащая в себе программу чтения (формирования адресов А); признаки, характеризующие процесс вывода; признак замещения данных после вывода из накопителей 1, и выбор регистров для задания начального адреса чтения (О - в счетчик 6 из регистра 16( ив регистр 14 из регистра 1 - в счетчик 6 из регистра 162 и в регистр 14 из регистра 16,);

значение маркерного разряда Кг при фиксации начального адреса; адреса внешних устройств, через которые

ки. В соответствии с программой вы40

35

адреса, поступающего на вход блока

наком, поступающим на вход дешифратора 87 со входа 25 и совпадением

адреса, поступающего на вход блока

77, с адресом на входе 28. При совпадении этих адресов и при появлении общего признака установки связи Т ,1 на выходе элемента И-НЕ 81 вырабатывается состояние О, которое приводит к появлению далее на входе триггера 90 состояния 1 и на управляющем входе ключа 89 разрешения (низким уровнем). В результате в текущем такте во втором полупериоде синхроимпульса на входе 24 на выходе 26 появляется сигнал (квитанция) , си гнализирующий о готовности устройства к приему входного кадpa информации. В сле дующем такте триггер 90 переходит в состояние 1 в котором на выходе 27 вырабатывает- ся признак занятости .

Последовательный прием элементов кадра информации выполняется следующим образом.

Первый элемент кадра - управляющее слово определяется по декодированной элементов И-НЕ 85 маркерной комбинации 11. Если накопитель 3 пуст, ТО на выходе 92 и на выходе элемента И-НЕ 83 вырабатывается единичное состояние низким уровнем разрешения записи, обеспечивающее появление в следующем такте в регистре 86 управляющего слова ввода. Если в накопителе 3 остается еще часть несчитанных данных из предьщущего кадра, то запись в регистр 86 блокируется нулевым сигналом на входе 92. Далее элементом И-НЕ 85 вьщеляются маркерные комбинации, сопровождаю- щие данные и для которых обязательным является наличие хотя бы одного нуля в разрядах М( и М маркера. При наличии признака данных, которым соответствует состояние 1 на выходе элемента И-НЕ 85, анализируется дополнительно признак, формируемый на выходе 91 накопителя 3, и если в нем имеется хотя бы одна незаполненная ячейка, то на выходе 91 появляется единичное состояние. В результате на выходе элемента И-НЕ 82 низким уровнем вырабатывается сигнал записи данных в накопитель 3. Одновременно по этому же сигналу на вы- ход 26 выдается низким уровнем сигнал (квитанция) о приеме данного. Если чтение отстает от записи, то при полном заполнении накопителя 3 элемент И-НЕ 82 закрывается, сигнал низкого уровня на выходе 26 не формируется и задерживается в следующем такте поступление нового данного на вход 25. Активное состояние поддерживается, пока не закончится прием всего кадра и со входа 25 на входе дешифратора 87 не установится пауза. Признаком паузы может быть наличие в элементе кадра одних единиц, включая маркер. В режиме считывания из накопителей 1 и Ij формированием программных адресов А, управляет блок 22, в котором модуль счета для каждого счетчика W)5 (фиг.4) задается автономно регистром 106.

Группа переносов, возникающих на выходе элементов 108, преобразуется шифратором 104 в код, который является двоичным эквивалентом номера

счетчика 105, являющегося последним в цепочке сквозного переноса. При отсутствии переносов в счетчике 105 на выходе шифратора 104 действует нулевой код. Код с выхода шифратора

104 вместе с кодом на входе 97 образует адрес чтения для накопителя 103, один-из вьгходов которого используется для задания модуля счета в каждом из счетчиков 105; признак последнего данного формируется на выходе 99, и признак управляющий формированием формирователя 9 маркерных разрядов М - на выходе 100.

Порядок выбора элементов выходного кадра информации задается блоком 20.

Формула изобретения

Буферное запоминающее устройство, содержащее первый основной накопитель, первый дополнительный ндкопи- тель, первый и второй счетчики,первый блок управления и первый комму

I

татор, выход которого соединен с адресным входом первого основного накопителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй основной накопитель, второй дополнительный накопитель, регистры, третий счетчик, коммутаторы со второго по восьмой, формирователь управляющих сигналов, сумматоры, второй и третий блоки управления, причем первый вход, первый и второй выходы второго дополнительного накопителя соединены соответственно с первым выходом и с первым и

вторьм входами второго блока управления, второй и третий выходы которого подключены соответственно к первому входу первого блока управления и группе входов формирователя управляющих сигналов и ко второму входу первого блока управления, третий вход которого соединен с третьим выходом второго дополнительного накопителя, четвертый выход которого подключен к четвертому входу первого блока управления и первому входу формирователя управляющих сигналов,второй и третий входы которого соедийены соответственно со вторым выходом второго дополнительного накопителя и с управляющими выходами первого дополнительного накопителя, информационный выход которого подключен к первым входам первого и второго коммутаторов и чeтвepтo iy входу формирователя управляющих сигналов, пятый вход которого и информационный вход первого дополнительного накопителя подключены к выходу первого регистра, первому входу первого сумматора и вторым входам первого и второго коммутаторов, третьи входы которых соединены с выходом второго счетчика, вход которого соединен с выходом третьего коммутатора и первым входом шестого коммутатора, выход которого подключен ко входу первого регистра, а второй вход - к выходу первого сумматора, второй вход которого соединен с выходом пятого коммутатора и первым входом второго сумматора, выход которого подключен ко входу второго регистра, выход которого соединен с первым входом пятого коммутатора, первый и второй входы третьего коммутатора подключены к выходам третьего и четвертого регистров, входы которых соединены соответственно с выходом третьего счетчика и первым входом четвертого коммутатора и с выходом первого счетчика и вторым входом четвертого регистра, выход которого подключен к четвертым входам первого и второго коммутаторов, выходы пятого и шестого регистров соединены соответственно со входами седьмого и восьмого регистров, а входы пятого и шестого регистров - соответственно с выходами седьмого и восьмого коммутаторов, одни из входов которых подключены соответственно к выходам первого и второго основных накопителей, информационные входы которых соедин ены с пятым выходом второго дополнительного накопителя, адресный вход второго основного накопителя подключен к выходу второго коммутатора, выходы первого и третьего счетчиков соединены соответственно с шестым и седьмым входами формирователя управW

f5

20

25

80456

ляющих сигналов, восьмой вход которого подключен к по.рвому выходу третьего блока управления, второй выход и первый вход которого соединены с пятым входом и первым выходом первого блока управления, второй и третий выходы которого подключены ко второму входу третьего блока управления, третий выход которого соединен со вторыми входами второго сумматора два и пятого коммутатора, управляющий и стробирующий входы которого, управляющие входы второго регистра и шестого коммутатора подключены к выходам с четвертого по седьмой третьего блока управления, другие входы седьмого и восьмого коммутаторов подключены соответственно к четвертому выходу первого блока управления и маркерному выходу формирователя управляющих сигналов, девятый вход которого соединен с группой выходов первого блока управления, первый выход которого подключен к сйнхровходам первого дополнительного накопителя,второго счетчика, первого, второго, седьмого и восьмого регистров, управляющие входы накопителей, счетчиков, коммутаторов с первого по четвертый, седьмого и восьмого, регистров с пятого по восьмой соединены с управляющими выходами формирователя управляющих сигналов, девятый вход первого и третий вход второго блоков управления, входы синхронизации накопителей, первого и третьего счетчиков, третьего и четвертого регистров являются входом синхронизации устройства, информационными выходами и входами которого являются выходы седьмого и восьмого регистров, второй вход второго дополнительного накопителя и четвертый вход второго блока управления, его пятый и шестой входы, четвертый и пятый выходы, а также десятый и одиннадцатый входы первого блока управления являются управляющими входами устройства, входом начальной установки которого являются Входы установки дополнительных накопителей и двенадцатый вход первого блока управления.

30

35

40

45

50

34: 3S

n ч ге 28 25 зг,

iln

31, 31z33

99 95 30,

us. т

29

гч

УК 5

Фиг 2

к 9.

1.2

Фиг.З J, Zlg

Ю5

m

Ю7

f

L.

21

Г1

Ю5

IffS

..J

Ш

55

1a7 w

Редактор Н. Горват

Составитель Т. Зайцева

Техред В.Када р Корректор О. Луговая

Заказ 7057/46Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

f

Фиг ц

SI т.юг.1П.т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство управления накопителями на магнитных дисках | 1982 |

|

SU1053143A1 |

| Устройство для вывода информации | 1984 |

|

SU1167614A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферной памяти при построении средств векторной обработки сигналов, например при вычислении быстрого преобразования Фурье. Целью изобретения явля- повышение быстродействия устройства. Устройство содержит два основных накопителя, два дополнительных накопителя, три счетчика, коммутаторы с первого по восьмой, формирователь управляющих сигналов, два сумматора по модулю два, восемь регистров, три блока местного управления. Быстродействие устройства повышается за счет организации параллельного ввода и вывода информации в два главных накопителя, а также за счет введения средств вычисления адресов размещения информации в основных накопителях. В описываемом устройстве используется принцип управления с помощью потоков данных,в котором вся управляющая информация передается вместе с данными, что также повышает быстродействие устройства. Информация размещается в двух основных накопителях либо сплошным массивом как в едином накопителе,, либо различными массива- ми:данные с четными адресами записываются в одном, а с нечетными адресами - в другом основном накопителе. Первый дополнительный накопитель содержит программно сформированные адреса, которые используются при адресации с переменным шагом. Второй дополнительный накопитель является буферным при записи данных в случае, если основные накопители не свободны. 4 ил., 1 табл. с (Л №0

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-30—Публикация

1985-06-11—Подача